# FPGA Hardware Acceleration of Phylogenetic Tree Reconstruction with Maximum Parsimony Algorithms (FPGA を用いた最節約法による進化系統樹構築アルゴリズム の高速化)

# 2018年 3月

Henry Jose Block Saldana

# FPGA Hardware Acceleration of Phylogenetic Tree Reconstruction with Maximum Parsimony Algorithms (FPGA を用いた最節約法による進化系統樹構築アルゴリズム の高速化)

## Henry Jose Block Saldana

システム情報工学研究科

筑波大学

2018年 3月

## Abstract

In this research, we investigate, propose, evaluate and implement an FPGA-hardware approach for molecular phylogenetic tree reconstruction under maximum parsimony. Phylogenetic reconstruction has been investigated for many decades in different fields such as biology and medicine. Several software algorithms and hardware solutions have been proposed for phylogenetics. However, there is still the need to reduce the time required to reach a reliable solution. This research aims to contribute in this regard by proposing a general approach, faster than current software or hardware approaches, that can work for large phylogenetic problems.

We study different software algorithms and methods for accelerating the tree reconstruction and the heuristic search for the best tree. First, we start from a basic approach and gradually improve it. In total, we design and implement five FPGA hardware approaches based on the software algorithms studied. Each approach uses a new idea from a software algorithm or acceleration method, which helps to improve the performance over the other approaches.

We evaluate the implementation of each approach for several realworld biological datasets by comparing the results obtained with those from previous approaches, and with those from the phylogenetic software TNT (Tree analysis using New Technology), known as the fastest available parsimony program. We compare for each dataset the total execution time, the execution time required for evaluating a single tree, and the best score obtained. The datasets used are of medium to large size and each one of them consists of hundreds of sequences, each of them with thousands of DNA characters.

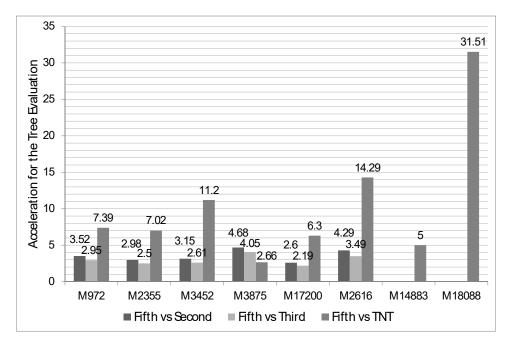

Our fifth and current approach, the fastest of all five, achieves acceleration rates between 2.66 and 31.94 against TNT for the evaluation of a single tree. These acceleration rates achieved are thanks to a combination of using the Indirect Calculation of Tree Lengths method, the Incremental Tree Optimization method, and the parallel and pipeline processing used. In our proposed hardware approach, all the DNA characters in a sequence are processed in parallel.

The main contribution of this work is to present an FPGA hardware approach for phylogenetic tree reconstruction under maximum parsimony that effectively addresses the evaluation of a single tree rearrangement and the stochastic local search. For the first time in the literature, an approach that covers both the complete and incremental first- and second-pass optimization, as well as the tree rearrangement evaluation has been proposed.

## Acknowledgements

My greatest gratitude is for my supervisor Professor Tsutomu Maruyama for his valuable guidance and unlimited support through all these 6 years. He gave me the opportunity to be part of his laboratory, where I found the ideal place to pursue the research I desired, and kindly gave me advice whenever I needed. This thesis could not have been possible without him.

I would also like to thank all the members in the Reconfigurable Computing Systems Laboratory for their friendship and incredible support. They always helped me without hesitation whenever I encountered any difficulties.

Finally, I would like to thank all my friends in Tsukuba and around for the great moments we spent together. Thanks to them I felt home since the first day, and motivated to work in my research.

## Contents

Abstract

| A | cknow | wledgements                                   | iii |

|---|-------|-----------------------------------------------|-----|

| 1 | Intr  | oduction                                      | 1   |

|   | 1.1   | Phylogenetics                                 | 1   |

|   |       | 1.1.1 Phylogenetic Trees                      | 1   |

|   |       | 1.1.2 Phylogenetic Tree Inference Methods     | 2   |

|   |       | 1.1.3 The Maximum Parsimony Criterion         | 3   |

|   |       | 1.1.4 Relevance of Molecular Sequence Data    | 4   |

|   |       | 1.1.5 Applications of Phylogenetics           | 4   |

|   | 1.2   | Background                                    | 6   |

|   |       | 1.2.1 FPGAs                                   | 6   |

|   |       | 1.2.2 Hardware Acceleration                   | 7   |

|   |       | 1.2.3 Software Solutions for Phylogenetics    | 8   |

|   |       | 1.2.4 Hardware Solutions for Phylogenetics    | 8   |

|   |       | 1.2.5 Problem Statement                       | 9   |

|   | 1.3   | Purpose of this Research                      | 9   |

|   | 1.4   | Thesis Outline                                | 10  |

| 2 | Alg   | orithms for Phylogenetic Tree Reconstruction  | 11  |

|   | 2.1   | Phylogenetic Tree Reconstruction              | 11  |

|   |       | 2.1.1 Stochastic Local Search                 | 11  |

|   |       | 2.1.2 Subtree Pruning and Regrafting (SPR)    | 12  |

|   |       | 2.1.3 Tree Optimization                       | 13  |

|   |       | 2.1.3.1 First-pass Optimization               | 13  |

|   |       | 2.1.3.2 Second-pass Optimization              | 14  |

|   | 2.2   | Software Algorithms                           | 15  |

|   |       | 2.2.1 Progressive Tree Neighborhood           | 15  |

|   |       | 2.2.2 Indirect Calculation of Tree Lengths    | 17  |

|   |       | 2.2.3 Alternative Second-pass Optimization    | 18  |

|   |       | 2.2.4 Incremental Tree Optimization           | 20  |

|   |       | 2.2.4.1 Incremental First-pass Optimization . | 21  |

|   |       | 2.2.4.2 Incremental Second-pass Optimization  | 22  |

| 3 | Apr   | proach for the Progressive Tree Neighborhood  | 23  |

|   | 3.1   | Algorithm Overview                            | 23  |

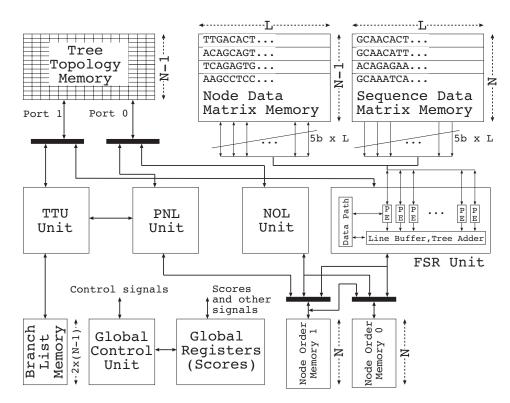

|   | 3.2   | Phylogenetic Data Structure                   | 24  |

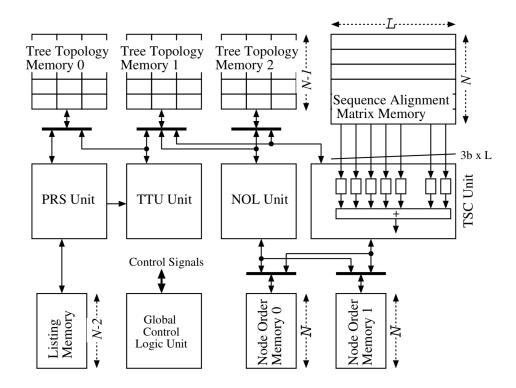

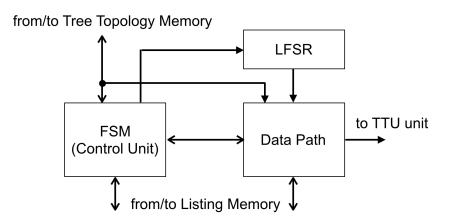

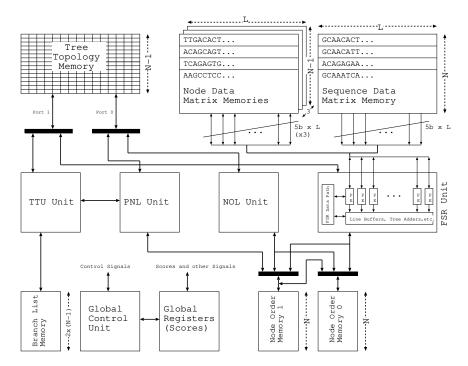

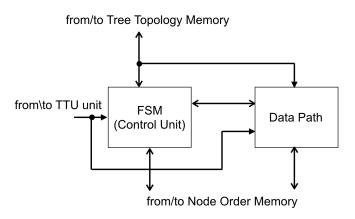

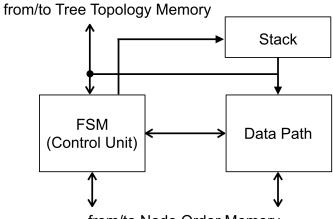

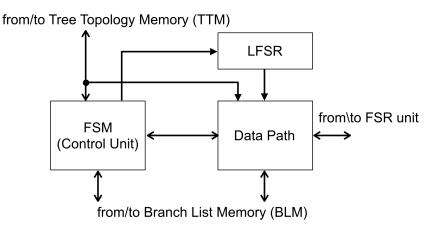

|   | 3.3   | Proposed Hardware Architecture                | 25  |

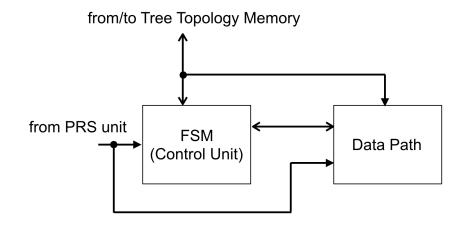

|   |       | 3.3.1 Prune and Reinsert Selection (PRS) unit | 26  |

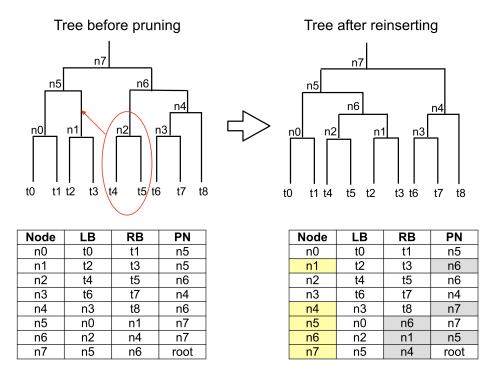

|   |       | 3.3.2 Tree Topology Update (TTU) unit         | 27  |

i

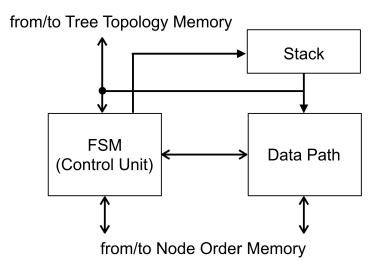

|   |            | 3.3.3 Node Order Listing (NOL) unit                       | 29       |

|---|------------|-----------------------------------------------------------|----------|

|   |            | 3.3.4 Tree Score Calculation (TSC) unit                   | 31       |

|   |            | 3.3.5 Global Control (GC) unit                            | 33       |

|   | 3.4        | Implementation Results                                    | 34       |

|   |            | 3.4.1 Hardware Utilization and Performance Results        | 34       |

|   | 3.5        | Comparison and Performance Evaluation                     | 35       |

|   |            | 3.5.1 Execution Time for the Score Calculation            | 35       |

|   |            | 3.5.2 Local Search Results Comparison                     | 35       |

|   | 3.6        | Discussion                                                | 37       |

| 4 | App        | proach for the Indirect Calculation of Tree Lengths       | 39       |

|   | 4.1        | Algorithm Overview                                        | 39       |

|   | 4.2        | Phylogenetic Data Structure                               | 40       |

|   | 4.3        | Proposed Hardware Architecture                            | 41       |

|   |            | 4.3.1 Tree Topology Update (TTU) unit                     | 43       |

|   |            | 4.3.2 Progressive Neighborhood Listing (PNL) unit .       | 45       |

|   |            | 4.3.3 Node Order Listing (NOL) unit                       | 46       |

|   |            | 4.3.4 First-, Second-pass and Rearrangement Evalu-        |          |

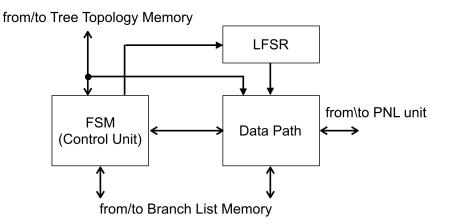

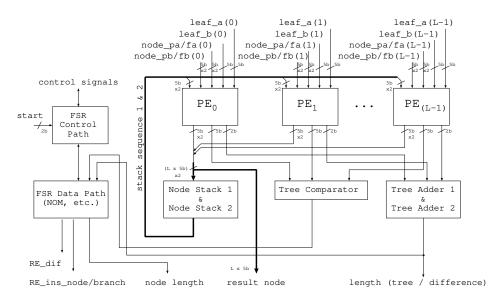

|   |            | ation (FSR) unit                                          | 48       |

|   |            | 4.3.4.1 First-pass Optimization (FSR-FP)                  | 50       |

|   |            | 4.3.4.2 Second-pass Optimization (FSR-SP)                 | 51       |

|   |            | 4.3.4.3 Rearrangement Evaluation (FSR-RE) .               | 52       |

|   |            | 4.3.5 Global Control (GC) unit                            | 53       |

|   | 4.4        | Implementation Results                                    | 54       |

|   |            | 4.4.1 Hardware Utilization and Performance Results        | 54       |

|   | 4.5        | Comparison and Performance Evaluation                     | 55       |

|   | 4.6        | Discussion                                                | 57       |

| 5 | ۸ nr       | proach for the Alternative Second-pass                    | 59       |

| 5 | 5.1        | Algorithm Overview                                        | 59<br>59 |

|   | 5.1<br>5.2 | Phylogenetic Data Structure                               |          |

|   | 5.2<br>5.3 | Proposed Hardware Architecture                            | 61       |

|   | 5.5        | -                                                         |          |

|   |            |                                                           | 63       |

|   |            | 5.3.2 Progressive Neighborhood Listing (PNL) unit .       | 65       |

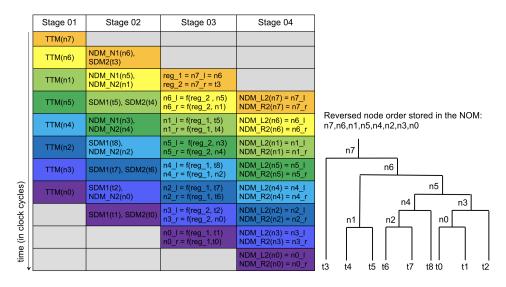

|   |            | 5.3.3 Node Order Listing (NOL) unit                       | 67       |

|   |            | 5.3.4 First-, alternative Second-pass and Rearrange-      | (0       |

|   |            | ment evaluation (FSR) unit                                | 68       |

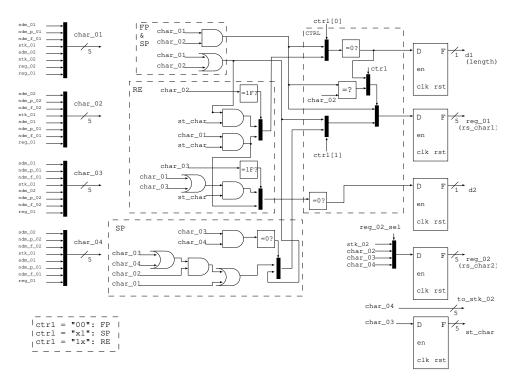

|   |            | 5.3.4.1 First-pass Optimization (FSR-FP)                  | 70       |

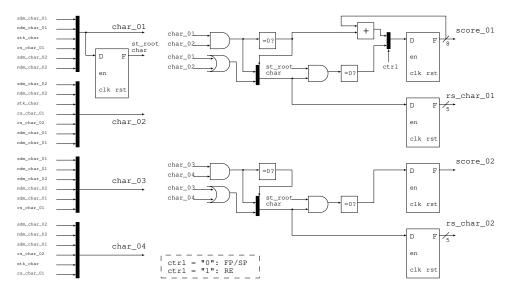

|   |            | 5.3.4.2 Alternative Second-pass Optimization<br>(FSR-ASP) | 71       |

|   |            | 5.3.4.3 Rearrangement Evaluation (FSR-RE) .               | 72       |

|   |            | 5.3.5 Global Control (GC) unit                            | 74       |

|   | 5.4        | Implementation Results                                    | 74       |

|   |            | 5.4.1 Hardware Utilization and Performance Results        | 74       |

|   | 5.5        | Comparison and Performance Evaluation                     | 75       |

|   | 5.6        | Discussion                                                | 77       |

| 6  | App   | <b>roach</b> t | for the In | cremental Tree Optimization           | 79    |

|----|-------|----------------|------------|---------------------------------------|-------|

|    | 6.1   | Appro          | oach One   |                                       | . 79  |

|    |       | 6.1.1          | Algorith   | m Overview                            | . 79  |

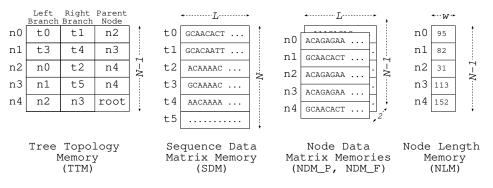

|    |       | 6.1.2          |            | enetic Data Structure                 |       |

|    |       | 6.1.3          |            | d Hardware Architecture               |       |

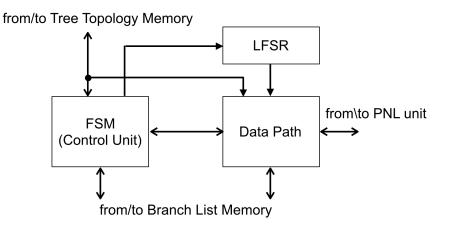

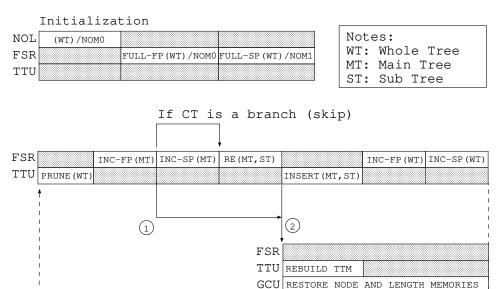

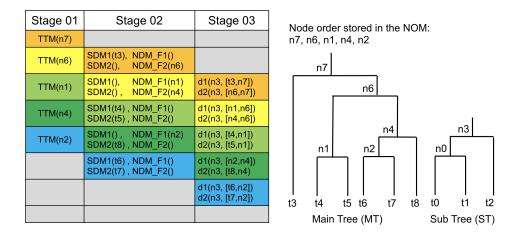

|    |       |                | 6.1.3.1    | Tree Topology Update (TTU) unit       |       |

|    |       |                | 6.1.3.2    |                                       |       |

|    |       |                | 6.1.3.3    | e e                                   |       |

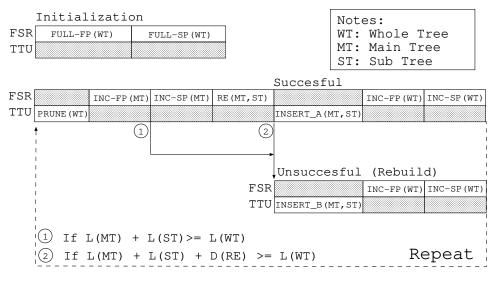

|    |       |                |            | Evaluation (FSR) unit                 |       |

|    |       |                | 6.1.3.4    | Global Control (GC) unit              |       |

|    |       | 6.1.4          | Implem     | entation Results                      |       |

|    |       |                | 6.1.4.1    |                                       |       |

|    |       |                |            | Results                               | . 97  |

|    |       | 6.1.5          | Compai     | rison and Performance Evaluation      | . 97  |

|    |       | 6.1.6          |            | ion                                   |       |

|    | 6.2   | Appro          | oach Two   |                                       | . 101 |

|    |       | 6.2.1          |            | m Overview                            |       |

|    |       | 6.2.2          |            | enetic Data Structure                 |       |

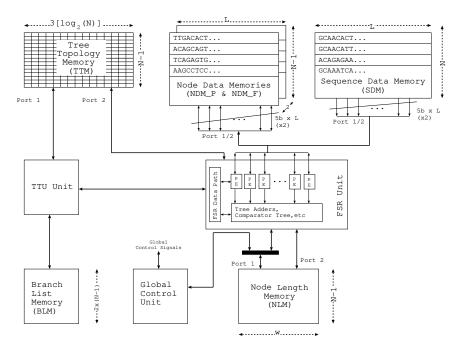

|    |       | 6.2.3          |            | d Hardware Architecture               |       |

|    |       |                | 6.2.3.1    | Tree Topology Update (TTU) unit       | . 104 |

|    |       |                | 6.2.3.2    | First-, Second-pass and Rearrangement | ţ     |

|    |       |                |            | Evaluation (FSR) unit                 | . 106 |

|    |       |                | 6.2.3.3    | Global Control (GC) unit              | . 114 |

|    |       | 6.2.4          | Implem     | entation Results                      | . 115 |

|    |       |                | 6.2.4.1    | Hardware Utilization and Performance  |       |

|    |       |                |            | Results                               | . 115 |

|    |       | 6.2.5          | Compai     | rison and Performance Evaluation      | . 116 |

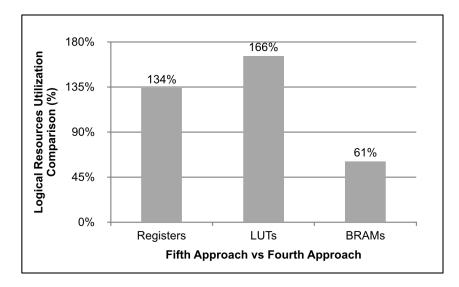

|    |       |                | 6.2.5.1    | Logical Resources Utilization Compar- |       |

|    |       |                |            | ison                                  | . 116 |

|    |       |                | 6.2.5.2    | Local Search Results Comparison       | . 117 |

|    |       | 6.2.6          | Discuss    | ion                                   | . 119 |

| _  | ~     | 1.5            |            |                                       |       |

| 7  | Gen   | eral Di        | iscussion  |                                       | 121   |

| 8  | Con   | clusion        | ns and Fu  | ture Directions                       | 125   |

|    | 8.1   | Contr          | ibutions o | of this Work                          | . 126 |

|    | 8.2   | Futur          | e Directio | ns                                    | . 126 |

| Bi | bliog | raphy          |            |                                       | 127   |

# **List of Figures**

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Phylogeny of True Flies (Diptera) [3] Number of possible trees versus number of taxa [4] A summary of some applications of phylogenetics [12] Conceptual structure of an FPGA [14] Conceptual diagram of a logic cell [14] | 2<br>3<br>5<br>6<br>7 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 2.1                             | Example of Subtree Pruning and Regrafting (SPR) [35]                                                                                                                                                                       | 12                    |

| 2.2                             | First-pass optimization algorithm [40]                                                                                                                                                                                     | 13                    |

| 2.3                             | Example of the first-pass optimization                                                                                                                                                                                     | 14                    |

| 2.4                             | Second-pass optimization algorithm [40]                                                                                                                                                                                    | 14                    |

| 2.5                             | Example of the second-pass optimization                                                                                                                                                                                    | 15                    |

| 2.6                             | Example of the progressive tree neighborhood                                                                                                                                                                               | 16                    |

| 2.7                             | Difference Score Calculation [42]                                                                                                                                                                                          | 17                    |

| 2.8                             | Example of the rearrangement evaluation process                                                                                                                                                                            | 18                    |

| 2.9                             | Example of rerooting the tree                                                                                                                                                                                              | 19                    |

| 2.10                            | Rerooting the tree for the ICTL                                                                                                                                                                                            | 19                    |

| 2.11                            | Traversing the tree in all three different ways                                                                                                                                                                            | 20                    |

| 2.12                            | Example of the incremental first-pass optimization                                                                                                                                                                         | 21                    |

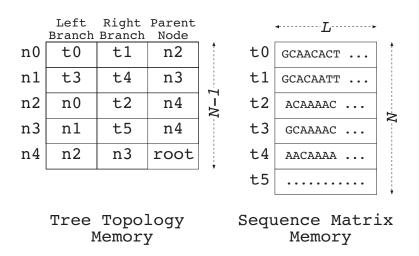

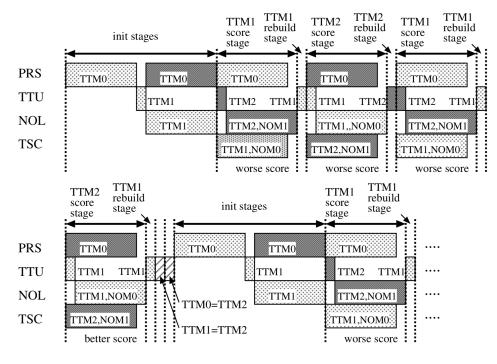

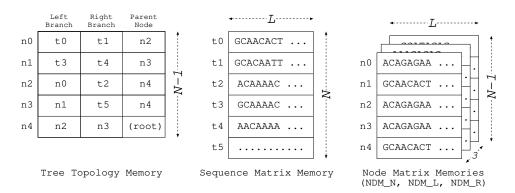

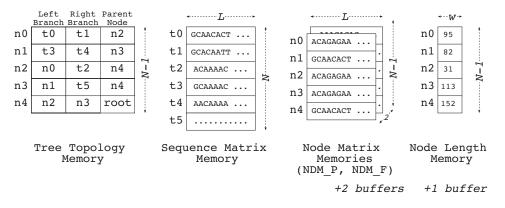

| 3.1                             | First approach: memory data structure                                                                                                                                                                                      | 24                    |

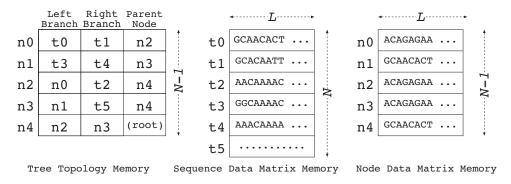

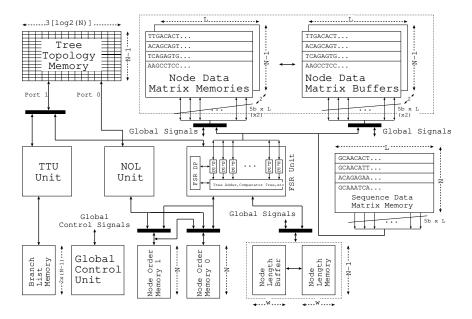

| 3.2                             | First approach: general block diagram of the proposed                                                                                                                                                                      |                       |

|                                 | hardware architecture                                                                                                                                                                                                      | 26                    |

| 3.3                             | First approach: general block diagram of the PRS unit .                                                                                                                                                                    | 26                    |

| 3.4                             | First approach: general block diagram of the TTU unit .                                                                                                                                                                    | 28                    |

| 3.5                             | First approach: example of the nodes modified by the                                                                                                                                                                       |                       |

|                                 | pruning and regrafting process                                                                                                                                                                                             | 28                    |

| 3.6                             | First approach: general block diagram of the NOL unit                                                                                                                                                                      | 29                    |

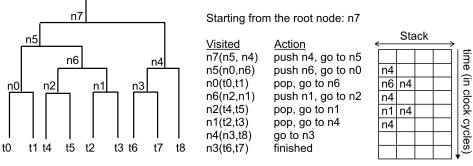

| 3.7                             | First approach: example of the NOL unit listing process                                                                                                                                                                    | 30                    |

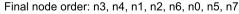

| 3.8                             | First approach: general block diagram of the TSC unit .                                                                                                                                                                    | 31                    |

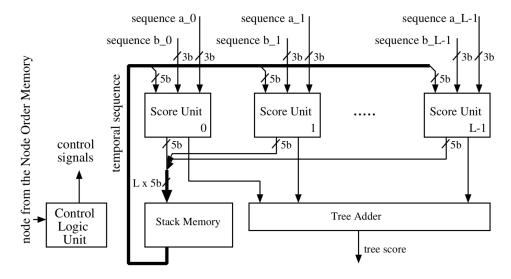

| 3.9                             | First approach: general block diagram of the Score Unit                                                                                                                                                                    | 32                    |

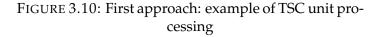

| 3.10                            | First approach: example of TSC unit processing                                                                                                                                                                             | 33                    |

| 3.11                            | First approach: execution flow of the proposed hard-                                                                                                                                                                       |                       |

|                                 | ware architecture                                                                                                                                                                                                          | 34                    |

| 4.1                             | Second approach: memory data structure                                                                                                                                                                                     | 41                    |

| 4.2                             | Second approach: general block diagram of the pro-                                                                                                                                                                         |                       |

|                                 | posed hardware architecture                                                                                                                                                                                                | 42                    |

| 4.3                             | Second approach: general block diagram of the TTU                                                                                                                                                                          |                       |

|                                 | unit                                                                                                                                                                                                                       | 43                    |

| 4.4                             | Second approach: example of the nodes modified by                                                                                                                                                                          |                       |

|                                 | the pruning process                                                                                                                                                                                                        | 44                    |

| 4.5         | Second approach: example of the nodes modified by                                                             |          |

|-------------|---------------------------------------------------------------------------------------------------------------|----------|

|             | the reinsertion process                                                                                       | 44       |

| 4.6         | Second approach: general block diagram of the PNL                                                             |          |

|             | unit                                                                                                          | 45       |

| 4.7         | Second approach: example of the PNL listing                                                                   | 46       |

| 4.8         | Second approach: general block diagram of the NOL                                                             |          |

|             | unit                                                                                                          | 47       |

| 4.9         | Second approach: example of the NOL unit listing pro-                                                         |          |

|             | Cess                                                                                                          | 48       |

| 4.10        | Second approach: general block diagram of the FSR unit                                                        | 48       |

|             | Second approach: general block diagram of the Pro-                                                            |          |

|             | cessing Element (PE)                                                                                          | 49       |

| 4.12        | Second approach: example of the pipeline processing                                                           |          |

|             | during the FSR-FP                                                                                             | 50       |

| 4.13        | Second approach: example of the pipeline processing                                                           |          |

|             | during the FSR-SP                                                                                             | 52       |

| 4.14        | Second approach: example of the pipeline processing                                                           |          |

|             | during the FSR-RE                                                                                             | 53       |

| 4.15        | Second approach: execution flow of the proposed hard-                                                         |          |

|             | ware architecture                                                                                             | 54       |

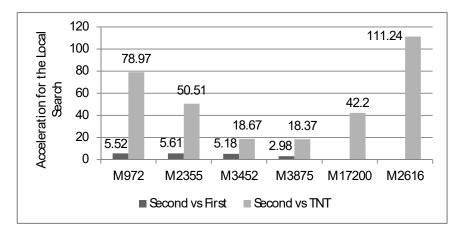

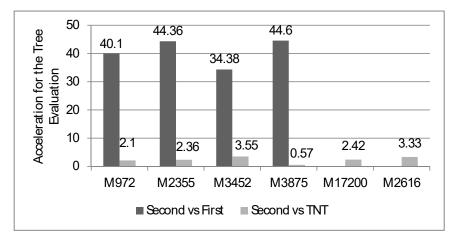

| 4.16        | Second approach: acceleration rate for the local search.                                                      | 56       |

|             | Second approach: acceleration rate for the tree evalu-                                                        |          |

|             | ation                                                                                                         | 56       |

| 5.1         | Third approach, mamany data structure                                                                         | 61       |

| 5.1<br>5.2  | Third approach: memory data structure                                                                         | 61       |

| 3.2         | Third approach: general block diagram of the proposed hardware architecture                                   | 62       |

| 5.3         | Third approach: general block diagram of the TTU unit                                                         | 62<br>63 |

| 5.3<br>5.4  | Third approach: general block diagram of the TTO unit<br>Third approach: example of the nodes modified by the | 05       |

| 5.4         |                                                                                                               | 64       |

| 5.5         | pruning process                                                                                               | 04       |

| 5.5         |                                                                                                               | 65       |

| <b>F</b> (  | reinsertion process                                                                                           |          |

| 5.6         | Third approach: general block diagram of the PNL unit                                                         | 65       |

| 5.7         | Third approach: example of the PNL listing                                                                    | 66<br>67 |

| 5.8<br>5.0  | Third approach: general block diagram of the NOL unit                                                         | 67       |

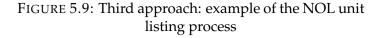

| 5.9<br>5.10 | Third approach: example of the NOL unit listing process                                                       | 68<br>60 |

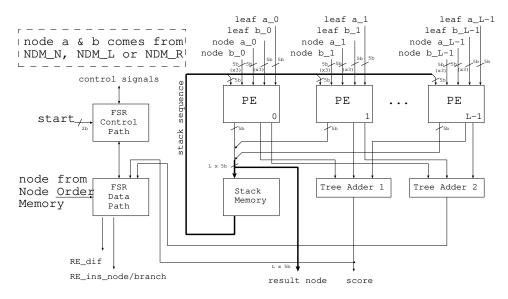

| 5.10        | Third approach: general block diagram of the FSR unit                                                         | 69       |

| 5.11        | Third approach: general block diagram of the Process-                                                         | 70       |

| E 10        | ing Element (PE)                                                                                              | 70       |

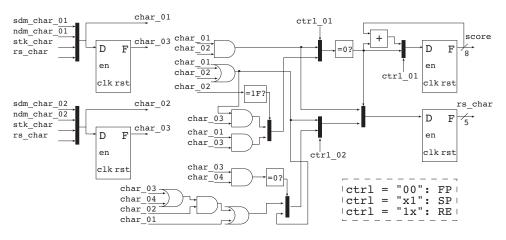

| 3.12        | Third approach: example of the pipeline processing                                                            | 71       |

| E 10        | during the FSR-FP                                                                                             | 71       |

| 5.15        | Third approach: example of the pipeline processing                                                            | 70       |

| E 1 4       | during the FSR-ASP                                                                                            | 72       |

| 5.14        | Third approach: example of the pipeline processing                                                            | 70       |

| E 1 E       | during the FSR-RE                                                                                             | 73       |

| 5.15        | Third approach: execution flow of the proposed hard-                                                          | -7 A     |

| E 17        | ware architecture                                                                                             | 74       |

| 5.16        | Third approach: acceleration rate for the local search .                                                      | 77       |

| 5.17       | Third approach: acceleration rate for the tree evaluation                                 | 77  |

|------------|-------------------------------------------------------------------------------------------|-----|

| 6.1<br>6.2 | Fourth approach: memory data structure Fourth approach: general block diagram of the pro- | 81  |

|            | posed hardware architecture                                                               | 82  |

| 6.3        | Fourth approach: general block diagram of the TTU unit                                    | 83  |

| 6.4        | Fourth approach: example of the nodes modified by                                         | 0.4 |

| 65         | the pruning process                                                                       | 84  |

| 6.5        | Fourth approach: example of the nodes modified by the reinsertion process                 | 85  |

| 6.6        | Fourth approach: general block diagram of the NOL                                         | 00  |

| 0.0        | unit                                                                                      | 85  |

| 6.7        | Fourth approach: example of the NOL unit listing pro-                                     |     |

|            | cess                                                                                      | 86  |

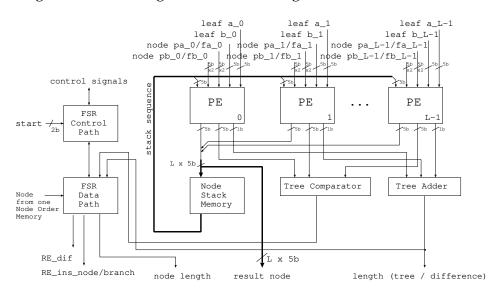

| 6.8        | Fourth approach: general block diagram of the FSR unit                                    | 87  |

| 6.9        | Fourth approach: general block diagram of the Pro-                                        | 00  |

| 6 10       | cessing Element (PE)                                                                      | 88  |

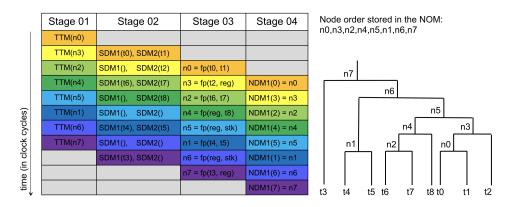

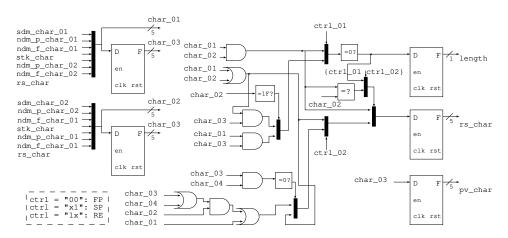

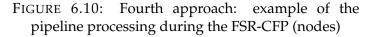

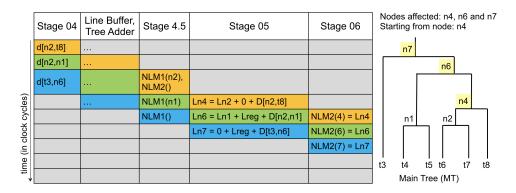

| 6.10       | Fourth approach: example of the pipeline processing during the FSR-CFP (nodes)            | 90  |

| 6.11       | Fourth approach: example of the pipeline processing                                       | 70  |

|            | during the FSR-CFP (lengths)                                                              | 90  |

| 6.12       | Fourth approach: example of the pipeline processing                                       |     |

|            | during the FSR-IFP (nodes)                                                                | 92  |

| 6.13       | Fourth approach: example of the pipeline processing                                       | ~~  |

| (14        | during the FSR-IFP (lengths)                                                              | 92  |

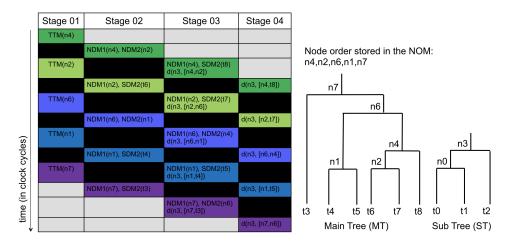

| 0.14       | Fourth approach: example of the pipeline processing during the FSR-CSP                    | 94  |

| 6.15       | Fourth approach: example of the pipeline processing                                       | 71  |

| 0.10       | during the FSR-RE                                                                         | 95  |

| 6.16       | Fourth approach: execution flow of the proposed hard-                                     |     |

|            | ware architecture                                                                         | 96  |

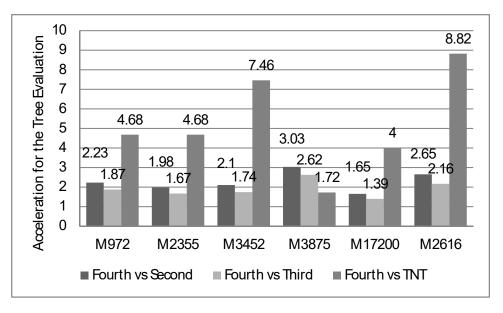

| 6.17       | Fourth approach: acceleration rate for the tree evalua-                                   | 00  |

| 6 10       | tion                                                                                      |     |

|            | Fifth approach: memory data structure                                                     | 105 |

| 0.17       | hardware architecture                                                                     | 104 |

| 6.20       | Fifth approach: general block diagram of the TTU unit                                     |     |

|            | Fifth approach: general block diagram of the FSR unit .                                   |     |

| 6.22       | Fifth approach: general block diagram of the Process-                                     |     |

|            | ing Element (PE)                                                                          | 107 |

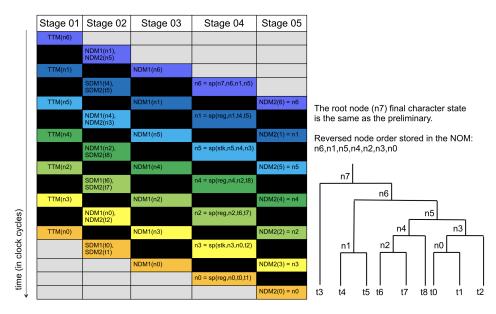

| 6.23       | Fifth approach: example of the pipeline processing dur-                                   | 110 |

| 6 24       | ing the FSR-IFP (nodes)                                                                   | 110 |

| 0.24       | Fifth approach: example of the pipeline processing dur-<br>ing the FSR-IFP (lengths)      | 110 |

| 6.25       | Fifth approach: example of the pipeline processing dur-                                   | 110 |

|            | ing the FSR-SP                                                                            | 112 |

| 6.26       | Fifth approach: example of the pipeline processing dur-                                   |     |

|            | ing the FSR-RE                                                                            | 113 |

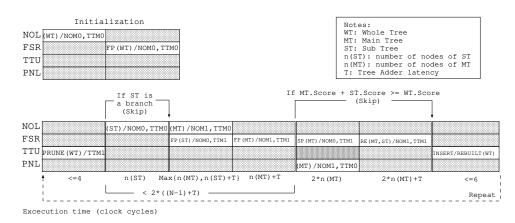

| Fifth approach: execution flow of the proposed hard-      |                   |

|-----------------------------------------------------------|-------------------|

| ware architecture                                         | 114               |

| Fifth approach: comparison of logical resources uti-      |                   |

| lization                                                  | 117               |

| Fifth approach: acceleration rate for the tree evaluation | 119               |

|                                                           | ware architecture |

# **List of Tables**

| 3.1<br>3.2 | First approach: 3-bit representation for DNA characters<br>First approach: example of the memory listing (1'b0 = | 24       |

|------------|------------------------------------------------------------------------------------------------------------------|----------|

| 3.3        | invalid, 1'b1 = valid)                                                                                           | 27       |

| 0.0        | sentation for DNA characters                                                                                     | 32       |

| 3.4        | First approach: datasets used [45]                                                                               | 34       |

| 3.5        | First approach: implementation results on a Kintex-7                                                             |          |

|            | FPGA                                                                                                             | 35       |

| 3.6        | First approach: results for the local search                                                                     | 36       |

| 4.1        | Second approach: 5-bit representation for DNA char-                                                              | 10       |

| 4.0        | acters [44]                                                                                                      | 40<br>54 |

| 4.2<br>4.3 | Second approach: datasets used [45]                                                                              | 54       |

| 4.5        | 7 FPGA                                                                                                           | 55       |

| 4.4        | Second approach: results for the local search                                                                    | 55       |

| 5.1        | Third approach: 5-bit representation for DNA charac-                                                             |          |

| 5.1        | ters $[44]$                                                                                                      | 60       |

| 5.2        | Third approach: datasets used [45]                                                                               | 74       |

| 5.3        | Third approach: implementation results on a Virtex-7                                                             |          |

|            | FPGA                                                                                                             | 75       |

| 5.4        | Third approach: results for the local search                                                                     | 76       |

| 6.1        | Fourth approach: 5-bit representation for DNA char-                                                              |          |

|            | acters [44]                                                                                                      | 80       |

| 6.2        | Fourth approach: datasets used [45]                                                                              | 97       |

| 6.3        | Fourth approach: implementation results on a Virtex-                                                             |          |

|            | 7 FPGA                                                                                                           | 97       |

| 6.4        | Fourth approach: results for the local search                                                                    | 98       |

| 6.5        | Fifth approach: datasets used [45]                                                                               | 115      |

| 6.6        | Fifth approach: implementation results on a Virtex-7FPGA                                                         | 115      |

| 6.7        | Fourth approach: implementation results on a Virtex-                                                             | 115      |

| 0.7        | 7 FPGA for $N = 1,024$ and $L = 829$                                                                             | 116      |

| 6.8        | Fifth approach: implementation results on a Virtex-7                                                             |          |

|            | FPGA for $N = 1,024$ and $L = 829$                                                                               | 116      |

| 6.9        | Fifth approach: results for the local search                                                                     |          |

This work is dedicated to my beloved family, who has constantly encouraged me to pursue my dreams, and who in spite of the long distance separating us has given me their unconditional support since I came to Japan. Thanks for always loving me.

# Chapter 1 Introduction

Thanks to rapid advancements in technology during the past years, DNA sequencing has become a more easy, quick and inexpensive process. Today, molecular sequence data obtained from DNA sequencing is used as the most reliable material to study living organisms. As a result, molecular phylogenetics, which studies how living organisms have evolved through the years, is now a growing field with many applications in biology, medicine and bioinformatics.

Many software algorithms and tools have already been developed for phylogenetics. However, molecular phylogenetics involves computational-intensive operations that can difficult obtaining solutions in reasonable amounts of time. For this reason, new software algorithms and hardware approaches are being proposed to ease and accelerate molecular phylogenetic analysis.

In this regard, hardware platforms such as FPGAs offer great potential for accelerating the different computational-intensive operations involved. Therefore, it is necessary to propose efficient hardware approaches that can be implemented on FPGAs. This will contribute to the growing field of phylogenetics and its applications.

## 1.1 Phylogenetics

Phylogenetics is the field that studies and attempts to reconstruct the evolutionary relationships among biological entities. These entities, which are commonly referred as taxa (singular: taxon), can be species, genomes, genes, regions of a gene, protein sequences, molecule sequences, etc. [1] [2].

#### 1.1.1 Phylogenetic Trees

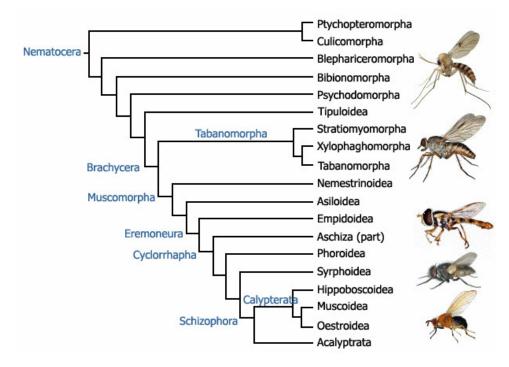

The evolutionary relationships among the taxa are graphically represented on a binary tree as ancestor-descendant relationships in a branching pattern. The tree starts from a common ancestor, known as the root of the tree, and branches into distinct lineages that descend to the taxa that are being analyzed. An example of a phylogenetic tree for the True Flies (Diptera) is shown in figure 1.1.

FIGURE 1.1: Phylogeny of True Flies (Diptera) [3]

As can be seen from figure 1.1, the current species of true flies descend from a common ancestor called *Nematocera*. This common ancestor evolved into distinct species of true flies, some of which are intermediate ancestors, others of which are the current species.

### 1.1.2 Phylogenetic Tree Inference Methods

There are different methods used to infer phylogenetic trees, but they can be classified into three main categories: Parsimony, Distance, and Likelihood methods [4]:

- Parsimony methods are based on the principle of Occam's Razor. This principle states that without any other information, the simplest explanation should be chosen. For phylogenetics, this means that the most likely tree to represent the true history of the taxa is the one that requires the fewest number of evolutionary changes. This is known as the maximum parsimony criterion, and the optimal tree as the most parsimonious tree.

- Distance methods are based on the assumption that it should be possible to infer a phylogenetic tree from the patterns of similarity among organisms. In other words, organisms that share a recent common ancestor should be more similar to each other than organisms whose last common ancestor was more ancient. The optimal tree is generated by using a distance matrix that contains the estimated evolutionary distances between all pairs of sequences.

Likelihood methods are based on statistics. They resemble parsimony methods in that different trees are compared and given a score. However, the score is not based on the number of evolutionary changes, but on how likely the taxa evolved on the tree given a model of amino acid substitution probabilities. The optimal tree is the one that has the highest probability among all trees.

There is no strict consent on which method is better or preferred, since each has its advantages and disadvantages. However, there are several criteria used to evaluate the methods themselves and the results they produce. For example, two criteria that are always taken into consideration are the efficiency of the method (i.e. how fast it performs) and its consistency (i.e. how reliable it is to generate the correct tree) are [4].

In this research, we are concerned with phylogenetic tree reconstruction of molecular DNA sequence data using the maximum parsimony criterion. We chose this criterion not only because of its widely acceptance and use, but also because of its simplicity when calculating the score of a tree, which makes it more suitable for a hardware implementation on FPGA.

#### 1.1.3 The Maximum Parsimony Criterion

As mentioned in section 1.1.2, the maximum parsimony criterion is based on the assumption that the most likely tree is the one that requires the fewest number of evolutionary changes to explain the given data [4]. Theoretically, this means that all possible trees have to be examined and evaluated [5]. However, this is not possible in practice, because they are too many trees, as shown in figure 1.2.

| Taxa | Rooted Trees <sup>a</sup> | Unrooted Trees <sup>b</sup> |

|------|---------------------------|-----------------------------|

|      |                           |                             |

| 3    | 3                         | 1                           |

| 4    | 15                        | 3                           |

| 5    | 105                       | 15                          |

| 6    | 945                       | 105                         |

| 7    | 10,395                    | 945                         |

| 8    | 135,135                   | 10,395                      |

| 9    | 2,027,025                 | 135,135                     |

| 10   | 34,459,425                | 2,027,025                   |

FIGURE 1.2: Number of possible trees versus number of taxa [4]

As can be seen from figure 1.2, as the number of taxa increases, the number of possible trees (either rooted or unrooted trees) grows exponentially. For this reason, phylogenetic tree reconstruction using maximum parsimony has been proven to be an NP-complete problem [6] [7].

For the above reason, heuristic methods are used in practice [8]. The aim of these approximate methods is to find a sub-optimal solution without having to evaluate all trees in the search space. Some examples include local search, genetic and memetic algorithms [9]. In this research, we focus on algorithms using local search.

#### 1.1.4 Relevance of Molecular Sequence Data

Even though there are different methods to infer phylogenetic trees, today almost all of them use molecular sequence data [10]. This is mainly because of the following three reasons [11]:

- DNA is the inherited material;

- Genetic material can now be sequenced easily, quickly, inexpensively and reliably;

- Sequences are highly specific and are often rich in information.

#### **1.1.5** Applications of Phylogenetics

The importance of Phylogenetics relies not only in the fact that it allows us to understand how species (molecular sequences in particular) evolved, but also in that it allows us to learn the general principles that enable us to predict how they will change in the future. This is very useful for many applications in areas such as biology, medicine and others. For example, some of the applications listed by The European Bioinformatics Institute (EMBL-EBI) can be summarized as following [12]:

- Classification: Phylogenetics using molecular sequences provides accurate descriptions of patterns of relatedness. Thanks to this, new species can be classified.

- Forensics: Phylogenetics is used to assess DNA evidence presented in court cases. This can clarify situations where someone has committed a crime, when food is contaminated, or where the father of a child is unknown.

- Identifying pathogens: Phylogenetics can be used to learn more about a new pathogen outbreak by finding out about which species the pathogen is related to and the likely source of transmission.

- Conservation: Phylogenetics can help conservation biologists in deciding which species they should try to prevent from becoming extinct.

- Bioinformatics: Many of the algorithms developed for phylogenetics have been used to develop software in other fields.

These applications are illustrated in figure 1.3.

FIGURE 1.3: A summary of some applications of phylogenetics [12]

As can be seen from figure 1.3, the applications of phylogenetics are diverse and of great utility to our society. This makes phylogenetics an important field of study and application that certainly will continue to grow in the near future.

## 1.2 Background

#### 1.2.1 FPGAs

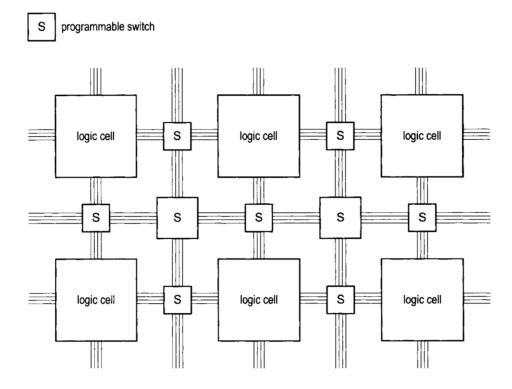

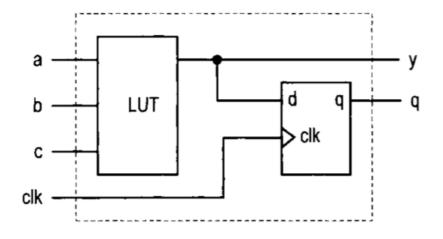

Field Programmable Gate Arrays (FPGAs) are semiconductor devices that are based around a matrix of configurable logic blocks connected via programmable interconnects. Unlike Application Specific Integrated Circuits (ASICs), FPGAs can be reprogrammed after manufacturing [13]. To better understand the concept of an FPGA, we will use the simplified structure shown in figure 1.4.

FIGURE 1.4: Conceptual structure of an FPGA [14]

As can be seen in figure 1.4, an FPGA is a two-dimensional array of logic cells and programmable switches. Logic cells can be configured to perform a specific function. They contain a combinational circuit such as a look-up table (LUT) and a sequential circuit such as a D-type flip-flop (D-FF). An n-input LUT can implement any ninput combinational function, and a D-FF can implement a one-bit sequential circuit synchronous to a clock signal [14]. An example of a logic cell is shown in figure 1.5.

In addition, FPGAs usually contain other cells known as macro blocks. These cells provide other complementary functions such as memory blocks, multipliers, clock management circuits, I/O interface circuits and even processor cores. A specific design of a digital circuit or system can then be implemented by specifying the function of each logic cell and macro cell, and connecting them through the programmable switches [14].

FIGURE 1.5: Conceptual diagram of a logic cell [14]

Because FPGAs are very versatile, they are used in numerous applications. Some examples include the following areas [13]:

- ASIC Prototyping

- High Performance Computing and Data Storage

- Industrial and Consumer Electronics

- Video and Image Processing

- Wired and Wireless Communications

#### 1.2.2 Hardware Acceleration

Besides FPGAs, there are other hardware platforms used for the acceleration of software algorithms and applications. One accelerator that is frequently used like FPGAs are GPUs. Both FPGAs and GPUs can achieve better performance than CPUs on certain tasks. On one hand, FPGAs are highly customizable, while, on the other hand, GPUs provide massive parallel execution resources and high memory bandwidth [15].

In this research, we propose an approach targeted at an FPGA rather than at a GPU or other many-core accelerators, because the algorithm under consideration, as we will see in section X, involves detailed low-level hardware control operations and a lot of memory accesses that are not suit for high-level languages. In addition, GPUs or other many-core accelerators impose a fixed programming model, whereas FPGAs do not; thus, they allow a higher level of customization [15]. This means that we can aim to obtain a higher performance by designing a specific circuit that best suits the phylogenetic tree reconstruction algorithm under consideration.

#### **1.2.3** Software Solutions for Phylogenetics

There are many programs available for phylogenetics, some of which are free to use, others of which are not. Of the extensive list available [16], some frequently-used free programs that include phylogenetic tree reconstruction under maximum parsimony are PHYLIP (Phylogeny Inference Package) [17], PAUP (Phylogenetic Analysis Using Parsimony) [18], MEGA (Molecular Evolution Genetic Analysis) [19] and TNT (Tree analysis using New Technology) [20].

From the above mentioned programs, TNT is known to be the fastest available parsimony program [21] [22]. Since we are interested in assessing how much acceleration our approach can provide with respect to a software implementation, we compare our results with the ones obtained from TNT.

#### **1.2.4 Hardware Solutions for Phylogenetics**

There have been several implementions of phylogenetic algorithms in different parallel hardware architectures that include not only FP-GAs, but also GPUs, multi-core processors and supercomputer systems [23]. Most of these implementations are for phylogenetic tree reconstruction under maximum likelihood, while only a few have been for the maximum parsimony problem [24]. In this research, we are concerned with FPGA-hardware acceleration of phylogenetic tree reconstruction under maximum parsimony.

From the few FPGA implementations proposed for the maximum parsimony problem, particularly worth mentioning are the ones in [25], [26] and [27].

First, in [25], an approach for whole-genome phylogenetic reconstruction under maximum parsimony was proposed. It covered both the generation of the tree by exploring the search space, and the tree scoring by performing median computations over the internal vertices of the tree. Results reported high acceleration rates against a software implementation. However, given that the method used is not based on heuristics and is highly computational-intensive, the execution time would grow considerably with the number of taxa.

Second, in [26], an approach for phylogenetic analysis under maximum parsimony was proposed. In this case, the approach consisted of a linear systolic array composed of 20 processing elements each of which scores a different tree topology in parallel. Again, results reported high acceleration rates against a software implementation. However, given that the proposed array computes the scores of all theoretically possible trees, the approach is limited to a small number of taxa.

Finally, in [26], an approach for computing the parsimony function on evolutionary trees for any number of taxa was proposed. The approach was compared against a software implementation by the same authors, and results reported acceleration rates not so high.

#### 1.2.5 Problem Statement

Even if heuristics or other approximate methods are used for phylogenetic tree reconstruction under maximum parsimony, a software approach can still require a considerable amount of time for larger phylogenetic problems.

As we saw in section 1.2.4, some FPGA hardware approaches have been proposed to deal with this problem, but they are still limited or not efficient enough to compete with the best software solutions available. In [25] and [26], the proposed approaches are not based on a heuristic method, but on the direct evaluation of all possible tress. As a result, they are limited to a small number of taxa. In [27], the approach is not restricted by the number of taxa, but it only addresses the computation of the parsimony function, and does not involve the search algorithm. In addition, it was only evaluated and compared against a software solution by the same authors.

In general, none of the current hardware approaches provides a solution for phylogenetic tree reconstruction under maximum parsimony that covers any number of taxa and implements the whole search algorithm. In addition, the approaches were not evaluated against the fastest available parsimony program, TNT (Tree analysis using New Technology) [20].

### **1.3 Purpose of this Research**

The main purpose of this research is to propose an approach for the hardware acceleration of a phylogenetic tree reconstruction with maximum parsimony algorithm using an FPGA. The approach has to be faster than current hardware and software approaches. Furthermore, it has to be a general approach that can work for large phylogenetic problems consisting of hundreds of taxa, each of them having a sequence of hundreds or thousands of DNA nucleotides.

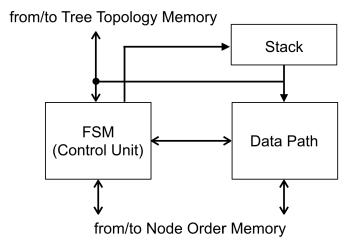

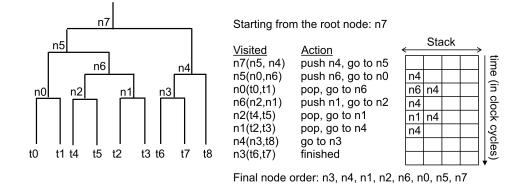

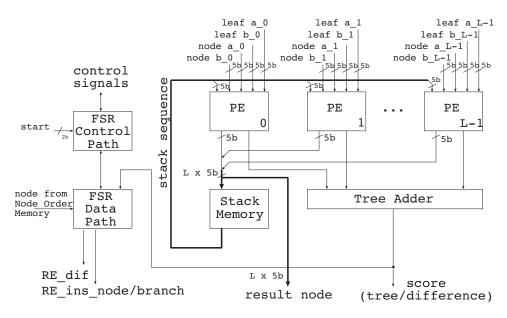

To achieve this purpose, we consider the following design requirements. First, the hardware architecture has to be modular. This is desirable not only to ease the design process, but to allow the different modules (units) to work in parallel. Second, the hardware architecture has to maximize the level of parallelism while minimizing the use of logical hardware resources. This means that it is necessary to take into account that tasks, which cannot be executed at the same time (i.e. in parallel), have to share as much as possible the same logical resources. Third, the hardware architecture has to be portable. This is important so it can be easily implemented on any FPGA without having to modify the source code. Last, but not least, all tasks that involve computational-intensive calculations have to work using pipeline processing to maximize the throughput of the hardware architecture. Our design goal is to ultimately obtain a throughput of one node per clock cycle. Taking into consideration all of the before mentioned requirements, we propose, design and implement five hardware architecture approaches based on the different software algorithms that we explore. We evaluate our implementations by comparing them to the phylogenetic software TNT [20] for several real-world biological datasets, each of them consisting of hundreds of taxa and sequences.

### **1.4 Thesis Outline**

This thesis is organized as follows. In chapter 2, we introduce the algorithms and methods that we researched for phylogenetic tree reconstruction under maximum parsimony. These algorithms are the base for all our hardware approaches that are detailed starting from chapter 3 through the end of chapter 6. In chapter 3, we present our first approach. In chapter 4, we present our second approach. In chapter 5, we present our third approach. In chapter 6, we present our fourth and fith approach. Finally, in chapter 7 we summarize all the results achieved and discuss about them. Following this, in chapter 8, we mention the overall conclusions and talk about the future work.

Parts of this thesis have already been published. Most of the first approach from chapter 3 has been published as a conference paper in [28]. Most of the second approach from chapter 4 has been published as a conference paper in [29] and as a journal paper in [30]. Most of the third approach from chapter 5 has been published as a conference paper in [31]. Finally, most of the fifth approach from section 6.2 of chapter 6 has been published as a conference paper in [32].

## Chapter 2

# Algorithms for Phylogenetic Tree Reconstruction

### 2.1 Phylogenetic Tree Reconstruction

#### 2.1.1 Stochastic Local Search

In section 1.1.3, we saw the need for using heuristic methods for phylogenetic tree reconstruction. The idea of these approximate methods is to find a near-optimal solution without having to evaluate all possible trees. The most well-known heuristic methods are based on stochastic local search. Stochastic local search algorithms are among the most successful methods for solving computationally difficult problems in many areas of computer science [33].

Stochastic local search uses iterative improvements to find better solutions. In general, every local search algorithm includes the following four parts [9]:

- A search space composed of the candidate solutions.

- An evaluation function of a solution, also known as the score function.

- A neighborhood function used to obtain a new solution by slightly modifying the current solution.

- A transition strategy to accept or reject a neighboring solution.

In this research, we examine four algorithms that are a variant of a basic stochastic local search algorithm. In simple terms, the algorithm is based on the iterative descent, which is guided by the length of the tree as the score function [34]. The length of the tree is equivalent to the number of evolutionary changes in the tree. It starts from a randomly generated tree in the search space, and tries to improve it on each iteration. A neighbor tree is obtained by rearranging the current tree by cutting a part of it and reinserting it elsewhere on the tree. This is known as Subtree Pruning and Regrafting (SPR). Then, the neighbor tree replaces the current one if it has a lower score (i.e. if the score is better). The algorithm stops when there is no better neighbor tree or when the maximum number of iterations of the algorithm has been reached.

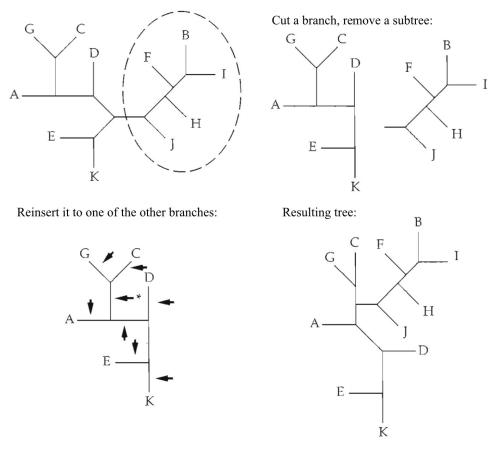

#### 2.1.2 Subtree Pruning and Regrafting (SPR)

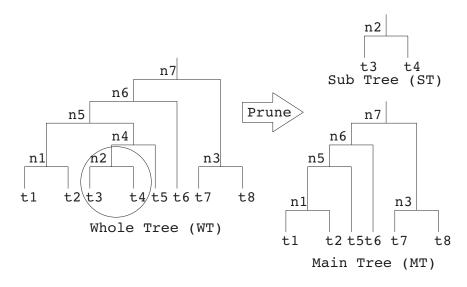

Subtree Pruning and Regrafting (SPR) is a rearrangement technique used to obtain a new tree by slightly modifying the current one. It consists of cutting a branch from the tree with a subtree attached to it, and reinserting it into the remaining tree in all possible places. Each reinsertion of the subtree creates a node into a branch of the remaining tree [35]. An example of SPR-rearrangement for an unrooted tree with 11 taxa is shown in figure 2.1.

FIGURE 2.1: Example of Subtree Pruning and Regrafting (SPR) [35]

As can be seen from figure 2.1, a 5-taxa subtree is pruned from the original tree, and it is inserted into the remaining tree of 6 taxa, in one of the 9 possible places. If a tree of n1 + n2 species has a subtree of n2 species pruned from it, there will be 2n1 - 3 possible places to reinsert it. One of these is the original location [35].

The advantage of SPR is that it can produce drastic changes in the tree topology. The resulting tree can have a greater variation from the starting tree than in other simpler techniques such as Nearest-Neighbor Interchange (NNI) [36], which consists in exchanging two adjacent branches of the tree. This helps in finding the globally optimal or near-optimal solution in the space of all trees [37].

#### 2.1.3 Tree Optimization

The tree optimization process consists of two phases. The first phase is called the first-pass optimization. The second phase is called the second-pass optimization. Both phases described here refer to a complete optimization of all the nodes in the tree.

The first-pass optimization is used to obtain:

- the preliminary character states (DNA sequences) of the nodes,

- the lengths of the nodes, and the total length (score) of the tree.

The second-pass optimization is used to obtain:

• the final character states (DNA sequences) of the nodes.

#### 2.1.3.1 First-pass Optimization

The first-pass optimization is the phase where the preliminary character states (the preliminary DNA sequences) of the nodes, along with their lengths (scores) are found. There are two widely used methods that depend on the algorithm applied: Fitch's algorithm [38] and Sankoff's algorithm [39]. Here, we use Fitch's, because it is less complex to implement in hardware.

The first-pass optimization proceeds from the tips of the tree (taxa) by formulating a character state (DNA sequence) for each node in the tree, working backwards, until the character state for the most distant node (root) has been formulated. In addition, each time an evolutionary change (a change in the DNA sequence) takes place in a node, its length is increased by one. A node character state, along with its length, is inferred by using the algorithm in figure 2.2 for each of the characters in the node. This algorithm is based on Fitch's algorithm [38].

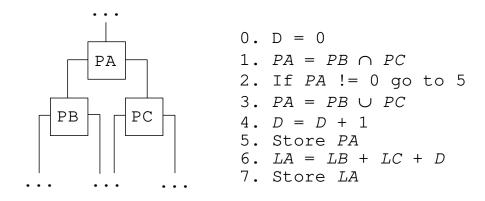

FIGURE 2.2: First-pass optimization algorithm [40]

*PA* refers to the preliminary character state of the current node, and *PB* and *PC* to that of its descendant nodes. *D* refers to the score difference between *PB* and *PC*. *LA* refers to the length of node *A*, *LB* to the length of node *B*, and *LC* to the length of node *C*. As can be noted, the length of a node is obtained by summing up the individual lengths of the descendant nodes and the score difference between those nodes. Finally, the length of the tree is equivalent to the length of the root node. An example of the first-pass optimization is shown in figure 2.3 for a tree with 5 taxa. *TL* refers to the length of the tree.

FIGURE 2.3: Example of the first-pass optimization

#### 2.1.3.2 Second-pass Optimization

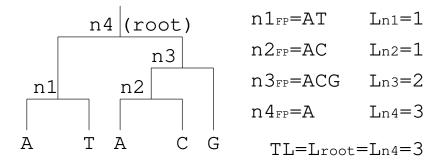

The second-pass optimization is the phase where the final character states (final DNA sequences) of the nodes are found. This pass proceeds in the reversed order, from the root to the tips of the tree. The final character state of a node is obtained by applying the algorithm in figure 2.4 for each of the characters in the node. This algorithm is based on Fitch's algorithm [38].

FIGURE 2.4: Second-pass optimization algorithm [40]

*FA* refers to the final character state of the current node *PA*, *FD* to that of its parent node, and *PB* and *PC* to the preliminary character

states of its descendants. For the root of the tree, *FA* is the same as *PA*, because the root has no parent node. An example of the second-pass optimization is shown in figure 2.5.

FIGURE 2.5: Example of the second-pass optimization

As can be observed from figure 2.5, the final character states of the nodes are not necessarily the same as the preliminary character states.

### 2.2 Software Algorithms

In this research, we examine four algorithms for phylogenetic tree reconstruction under maximum parsimony that are used to improve the consistency and the efficiency of the local search. In the following sections, we describe each one of them.

#### 2.2.1 Progressive Tree Neighborhood

The Progressive Tree Neighborhood aims to combine the properties of large and small neighborhoods by changing its size as the search progresses. It starts with a large neighborhood and ends with a small neighborhood. Starting the search with a large neighborhood allows examining more neighbors, and ensures a more global search. Then, as the search progresses the neighborhood gets reduced, so the changes applied to the tree topology are more restricted [41].

A simple progressive tree neighborhood uses Subtree Pruning and Regrafting (SPR) as the large neighborhood and Nearest-Neighbor Interchange (NNI) as the small neighborhood. To change the size of the neighborhood during the search, a distance parameter is used to constrain the distance between the pruned branch and the branch where it is reinserted [41]. The progressive tree neighborhood that uses SPR and NNI can be described by Equations 2.1 and 2.2 [41].

$$\begin{array}{l}

N_{d_{init}}^{SPR} \equiv N^{SPR} \\

N_{d_{final}}^{SPR} \equiv N^{NNI} \end{array} \rightarrow \begin{pmatrix} d_{init} \\ d_{final} \end{pmatrix} = \begin{pmatrix} max\delta(v_i, v_j) \\ 1 \end{pmatrix} \tag{2.1}$$

where  $v_i$  is the node at which the branch is pruned,  $v_j$  is the node at which the pruned branch is reinserted, and  $\delta(v_i, v_j)$  is the distance between these two nodes. It is given by

$$d = d_{init}(1 - \frac{i}{M}), \qquad i < M \tag{2.2}$$

where *i* is the  $i_{th}$  local search iteration and *M* is the maximum number of local search iterations. The distance parameter starts at  $d_{init}$  and ends at a value close to 1.

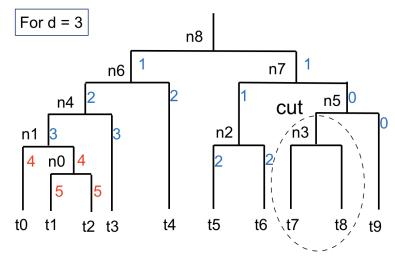

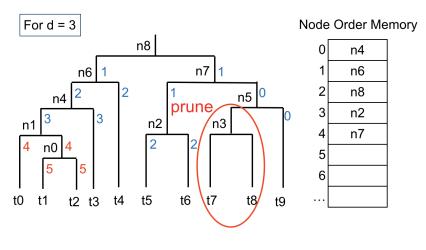

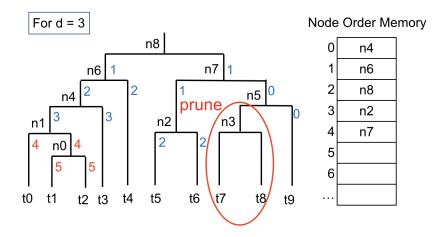

An example of how the distance parameter of the progressive tree neighborhood is used when a branch of the tree is pruned is given in figure 2.6. The distance parameter is equal to 3.

FIGURE 2.6: Example of the progressive tree neighborhood

Figure 2.6 shows a tree with 10 taxa and 9 internal nodes. In this example, the left branch of node n5, i.e. n3, is pruned from the tree, as indicated by the dashed circle in figure 2.6. Then, all branches in the remaining tree are given a value that corresponds to the distance between the respective branch and the pruned branch. In other words, branches that are further away from the pruned branch have a higher value than those which are closer. Finally, only those branches that have a value equal or lower than the current value of the distance parameter are chosen as candidates for reinserting the subtree in the remaining tree. In this example, the distance parameter has a current value of 3, so branches with a value of 4 or higher are considered to be out of the neighborhood, and; thus, not chosen.

#### 2.2.2 Indirect Calculation of Tree Lengths

The Indirect Calculation of Tree Lengths (ICTL) is a method used to evaluate all possible neighbor tree rearrangements after a branch has been pruned from the tree during the Subtree Pruning and Regrafting step [42]. The ICTL method allows to evaluate all rearrangements without having to actually reinsert the subtree in the remaining tree. Thus, there is no need to do a first-pass optimization on every single rearrangement to know the score of it. According to this method, the score of a neighbor tree rearrangement can easily be calculated by following Equation 2.3.

$$S_{nt} = S_{mt} + S_{st} + D.Score \tag{2.3}$$

where  $S_{nt}$  is the score of the neighbor tree rearrangement being evaluated,  $S_{mt}$  is that of the main tree (i.e. the remaining tree),  $S_{st}$  is that of the subtree, and D.Score is that of the difference between the subtree's root and the insertion branch in the main tree.

Equation 2.3 means that for each rearrangement the only value that has to be calculated independently is D.Score, since  $S_{mt}$  and  $S_{st}$  are common to all rearrangements.

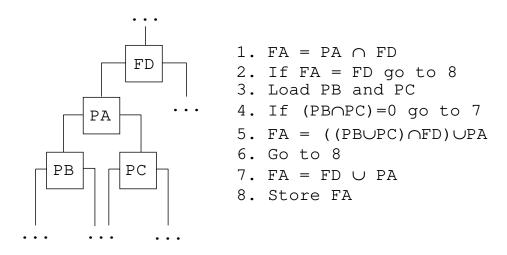

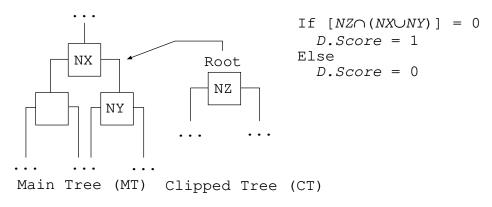

Then, the difference score *D.Score* can be calculated as shown in figure 2.7, where *NZ* is the final character state of the root of the subtree, *NX* is the final character state of a node in the main tree, and *NY* is that of its descendant. In other words, *NX* and *NY* form the branch where *NZ* could be reinserted. This process is done for each of the characters in the DNA sequence, and then the individual differences are sum up together to get the overall difference score.

FIGURE 2.7: Difference Score Calculation [42]

To better understand the idea of how the Indirect Calculation of Tree Lengths method is used, an example for evaluating all neighbor tree rearrangements for a subtree with 3 taxa and a main tree with 7 taxa is shown in figure 2.8.

FIGURE 2.8: Example of the rearrangement evaluation process

Figure 2.8 shows a main tree and a subtree resulting from pruning a branch from the original tree with the subtree attached to it. The main tree has 12 possible branches where the subtree can be reinserted. For each of these branches, the score of the neighbor tree rearrangement for that branch is calculated by using Equation 2.3, and the *D.Score* is calculated as indicated in figure 2.8. Finally, once the score of all possible neighbor tree rearrangements has been calculated, the branch that produces the rearrangement with the lowest score can be chosen as the candidate branch for reinserting the subtree into the main tree.

The ICTL method provides a fast technique to evaluate all tree rearrangements. In general, a first-pass optimization for a tree with Ttaxa requires visiting each one of the T - 1 internal nodes. Thus, the time required increases with T. On the other hand, the ICTL method allows to evaluate all rearrangements that can be constructed after pruning the tree without having to visit each one of them. The time required is approximately 1/T, which does not increase with T. In addition, this method is exact, i.e. it will always produce the right score. However, it requires a second-pass optimization on top of the first-pass optimization every time the tree is pruned, because the final character states of all nodes are required [42].

#### 2.2.3 Alternative Second-pass Optimization

In section 2.2.2 we mentioned that the Indirect Calculation of Tree Lengths (ICTL) required a second-pass optimization on top of the first-pass optimization, because the final character states of all the nodes are required to calculate the difference score *D.Score* for a neighbor tree rearrangement. Furthermore, as we saw in section 2.1.3.2, doing a second-pass optimization involves an algorithm that is more complex than the algorithm for the first-pass optimization. If the final character states are not needed during the search, then performing a second-pass optimization might not be desirable due to

the computational complexity. In this regard, the alternative secondpass optimization is a method that allows to use the ICTL without having to do a second-pass optimization as described in section 2.1.3.2 [43].

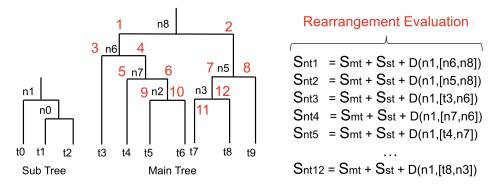

Fitch's algorithm [38] examines the evolution of only one DNA character on the tree at a time. This means that each character evolves independently; thus, the character states are reversible. As a consequence of reversibility of character states, the tree may be rooted at any point with no change in the tree length. An example of how a tree can be rerooted with no change in its total length is shown in figure 2.9.

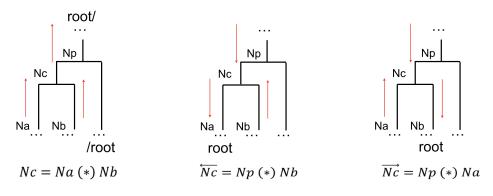

FIGURE 2.9: Example of rerooting the tree

Figure 2.9 shows three rooted trees with 5 taxa and 4 internal nodes each. The original tree is the one on the left. The tree in the middle has been obtained by rerooting the original tree in the branch formed by  $n^2$  and  $n^3$ , as indicated by the arrow with a number 2 inside a box. Similarly, the tree on the right has been obtained by rerooting the original tree in the branch formed by *G* and  $n^3$ , as indicated by the arrow with a number 2 inside a box. Similarly, the tree on the right has been obtained by rerooting the original tree in the branch formed by *G* and  $n^3$ , as indicated by the arrow with a number 3 inside a box. Both trees have the same length as the original one. In general, no matter where the tree is rooted, it will have the same length.

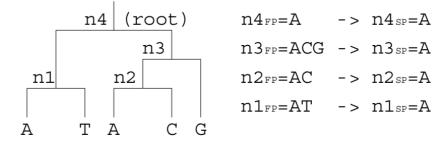

As we saw in section 2.2.2, the ICTL method uses the final character states of two nodes: NX and NY (see figure 2.7). Instead, we can reroot the tree at N(X,Y) as illustrated in figure 2.10.

FIGURE 2.10: Rerooting the tree for the ICTL

Then we can do a first-pass optimization, and use the preliminary character states of *NX* and *NY*, and *NZ* to calculate the score difference *D*.*Score*, because the final character states are the same as the preliminary character states for the root of the tree, as we saw in section 2.1.3.2.

Rerooting the tree means changing the order in which the original tree is traversed. In other words, there is no need to actually change the root of the tree and the tree topology every time the ICTL method is used. We only need to traverse the tree in all three possible ways, as shown in figure 2.11.

FIGURE 2.11: Traversing the tree in all three different ways

The (\*) symbol in figure 2.11 represents the operation used to calculate the character state of a node during the first-pass optimization. For each node, there are three node character states. The "normalpath" character state, assuming that the root is above the node; the "left-path" character state, assuming that the root is below on the left side; and the "right-path" character state, assuming that the root is below on the right side. The "normal-path" character state is calculated during the first-pass optimization, and the "left-path" and "right-path" character states are calculated during this alternative optimization. In this way, the complexity of performing a complete second-pass optimization is reduced to that of performing two firstpass optimization for all nodes in the tree as indicated in figure 2.11.

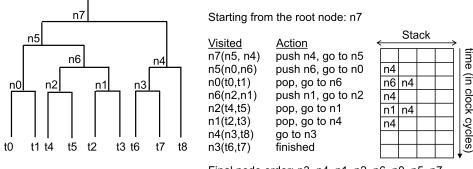

### 2.2.4 Incremental Tree Optimization

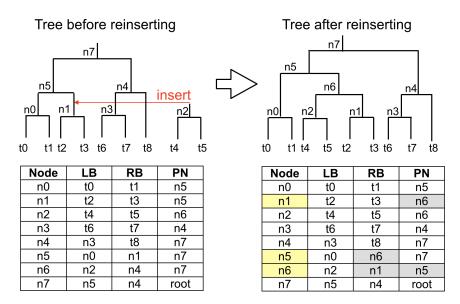

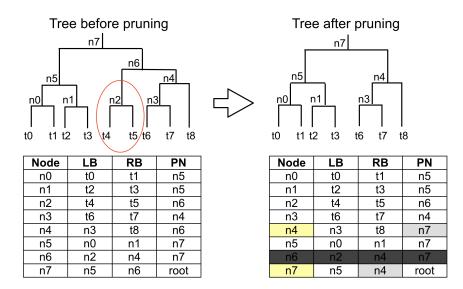

The Incremental Tree Optimization consists on optimizing only those nodes that were affected by the pruning or reinsertion of a branch during the Subtree Pruning and Regrafting (SPR). In other words, only those nodes that might have changed character state (DNA sequence) and length (score) have to be recalculated. As a result, the number of nodes that has to be updated during an incremental tree optimization is much lower than during a complete tree optimization.

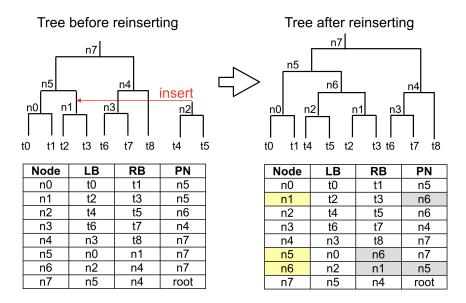

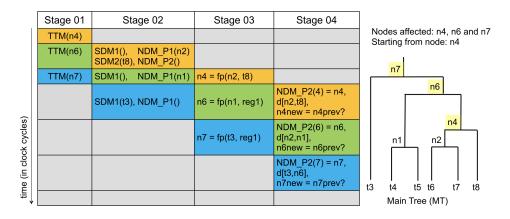

In a similar way to the complete tree optimization (explained in section 2.1.3), the incremental tree optimization consists of two phases: the incremental first-pass optimization and the incremental second-pass optimization. Here we describe both of them as we have applied them in our algorithm in section Y.Y.Y. For a more detail and complete version of the Incremental Tree Optimization method, please refer to the work in [42].

#### 2.2.4.1 Incremental First-pass Optimization

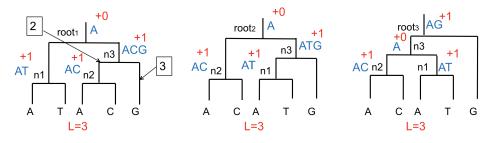

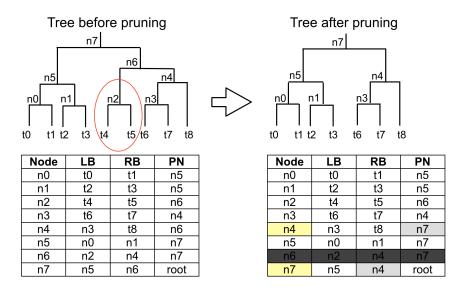

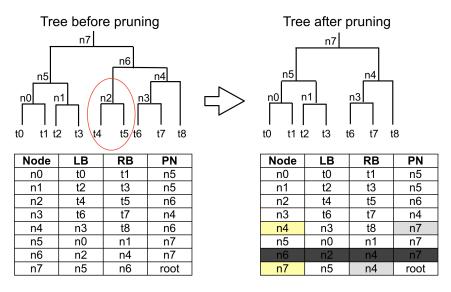

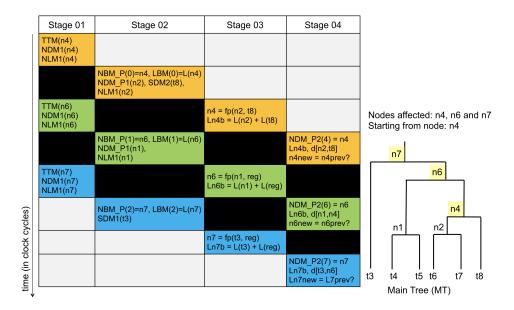

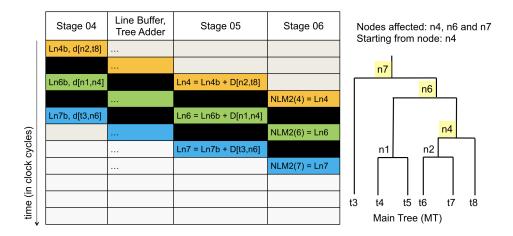

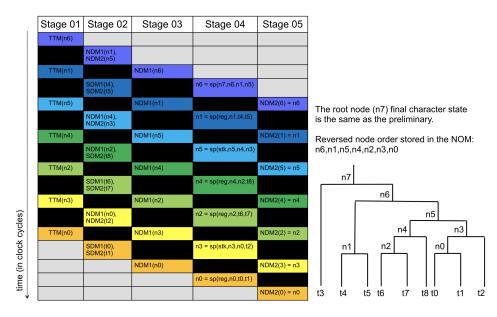

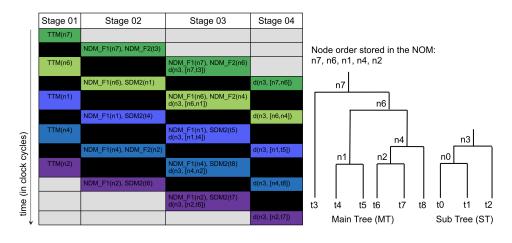

The incremental first-pass optimization consists on recalculating preliminary character states and node lengths only for those nodes that were affected by the pruning or reinsertion process [42]. The character state of a node is still calculated with the same algorithm used during the complete first-pass optimization (refer to figure 2.2). To better understand how the incremental first-pass optimization works, we show in figure 2.12 a simple example of how it is performed after the pruning process for a tree with 7 nodes.

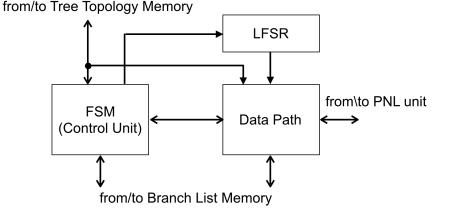

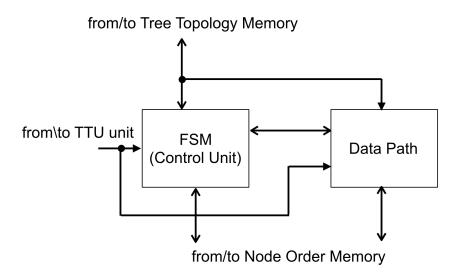

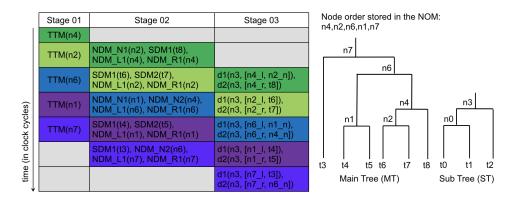

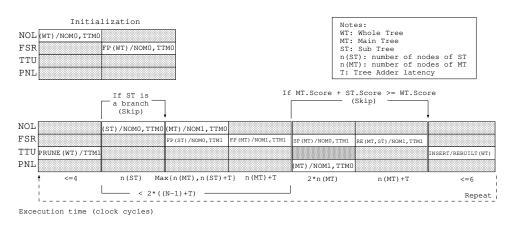

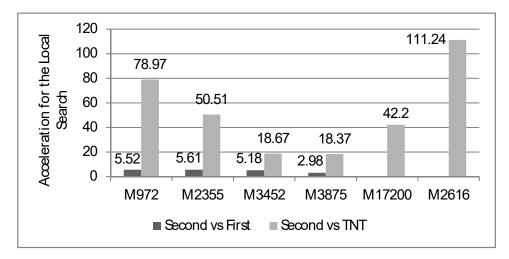

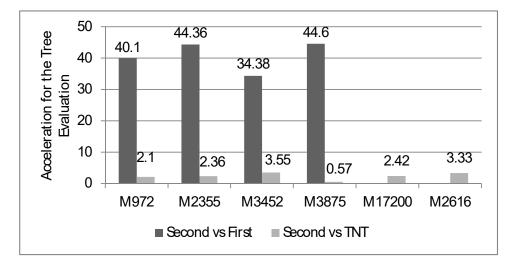

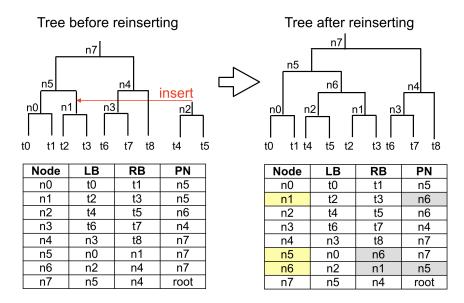

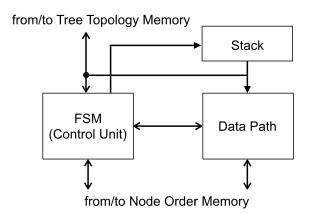

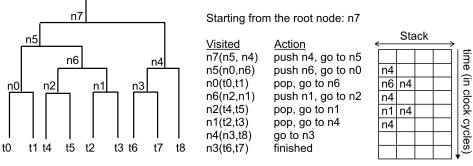

FIGURE 2.12: Example of the incremental first-pass optimization