# 演算加速機構を持つ並列システム向け PGAS 言語コンパイラの研究

2018年3月

田渕 晶大

# 演算加速機構を持つ並列システム向け PGAS 言語コンパイラの研究

## 田渕 晶大

システム情報工学研究科 筑波大学

2018年3月

i 概要

## 概要

ハイパフォーマンスコンピューティングの分野では、性能および消費電力あたりの性能を向上させるために演算加速機構(アクセラレータ)を搭載した並列システムが増加している。本研究ではアクセラレータを搭載した並列システム向けのプログラムの記述を簡易にして生産性を向上すると共に高性能を達成することを目的とする。アクセラレータは多数の演算器と高バンド幅のメモリにより高性能と省電力を実現しているが、CUDAや OpenCLを用いてアクセラレータ向け並列カーネルコードの記述やホストと独立したメモリの利用が必要でプログラミングが複雑である。そこで簡易な記述として指示文によるプログラミングモデルが提案されており、特に OpenACC は最初の標準仕様である。他方で、並列システムの分散メモリ環境におけるプログラミングには従来 MPI が用いられており、ユーザがデータや処理の分散と MPI による通信・同期をすべて記述しなければならないため、プログラミングが複雑である。そこでプログラミングを簡易にするため分散メモリ環境で仮想的な大域名前空間を提供する Partitioned Global Address Space (PGAS)モデルが提案されている。特に XcalableMP(XMP)では指示文や coarray による簡易な記述が可能である。アクセラレータを搭載した並列システムにおいては、従来のプログラミングではオフロードと分散並列をすべて直接記述するため非常に複雑なプログラミングが必要となる。そのうえ主な演算がアクセラレータ上で実行されるためアクセラレータメモリ上のデータ通信が必要であり、それを高速に行うためのハードウェア機能を利用することが重要となる。

研究目的を達成するため、筑波大と理研の共同で OpenACC と XMP を統合した PGAS 言語 XcalableACC (XACC) を提案した。XACC では新たにアクセラレータ間通信の記述に対応することで XMP と OpenACC を単に組み合わる場合よりも高速な通信を可能としており、本研究では特に coarray による片側通信を提案した。XACC の生産性や性能を評価するため、NVIDIA GPU と PEZY-SC クラスタにむけてコンパイラを設計・実装した。XACC で利用する OpenACC に関して、2012 年当初はオープンソースのコンパイラ研究基盤がなく、商用コンパイラも GPU 等の一般的なアクセラレータのみの対応でかつ最適化が十分でなかったうえ、PEZY-SC には対応していなかった。そこで性能を向上させるためNVIDIA GPU 向けに、また対応コンパイラがなかったため PEZY-SC 向けに OpenACC コンパイラを設計・実装し最適化を行った。ベンチマークによる評価において NVIDIA GPU では既存の OpenACC コンパイラの最大 2.8 倍の性能を,PEZY-SC では直接記述する場合の 90% 以上の性能を達成した。またXACC のコンパイラを設計・実装し、実装した OpenACC コンパイラをだックエンドに用いてベンチマークやアプリケーションで評価を行なった。グローバルビューモデルでは逐次コードに指示文を加える形で簡易に記述でき、ローカルビューモデルは coarray による配列代入文で簡易に柔軟な通信を記述できた。NVIDIA GPU クラスタでは、グリッド分散と袖交換通信を行う Himeno benchmark はグローバルビュー

モデルによる記述で MPI+OpenACC による記述の 97% 以上の性能を達成した。複雑な通信を必要とする NPB-CG は、ローカルビューモデルにより MPI+OpenACC の 97% 以上の性能が得られた。PEZY-SC クラスタでは、Himeno benchmark はグローバルビューにより MPI+PZCL の 96% 以上の性能を達成した。 NVIDIA GPU クラスタにおいて、MPI+CUDA 実装と比べて XACC グローバルビューモデルによる記述で流体力学ミニアプリケーション CloverLeaf は 87% 以上、格子 QCD ミニアプリケーションは 95% 以上の性能が得られ、簡易な記述でありながら従来の記述に近い性能が得られた。

**iii** 目次

# 目次

| 概要  |                                           | i  |

|-----|-------------------------------------------|----|

| 第1章 | 序論                                        | 1  |

| 1.1 | 研究背景                                      | 1  |

| 1.2 | 研究目的                                      | 3  |

| 1.3 | 構成                                        | 4  |

| 第2章 | 研究の背景                                     | 5  |

| 2.1 | NVIDIA GPU                                | 5  |

| 2.2 | CUDA                                      | 6  |

|     | 2.2.1 ホストコード                              | 6  |

|     | 2.2.2 デバイスコード                             | 7  |

| 2.3 | PEZY-SC                                   | 8  |

| 2.4 | PZCL                                      | 9  |

|     | 2.4.1 ホストコード                              | 9  |

|     | 2.4.2 デバイスコード                             | 10 |

| 2.5 | OpenACC                                   | 11 |

|     | 2.5.1 実行モデル                               | 11 |

|     | 2.5.2 メモリモデル                              | 13 |

|     | 2.5.3 プログラム例                              | 13 |

| 2.6 | XcalableMP                                | 13 |

|     | 2.6.1 グローバルビューモデル                         | 14 |

|     | 2.6.2 ローカルビューモデル                          | 15 |

| 第3章 | 演算加速機構を持つ並列クラスタ向け PGAS 言語 XcalableACC の提案 | 19 |

| 3.1 | 概要                                        | 19 |

| 3.2 | グローバルビューモデル                               | 19 |

| 3.3 | ローカルビューモデル                                | 21 |

| 3.4 | 関連研究                                      | 22 |

| 第4章                 | OpenACC コンパイラの設計・実装                 | 25       |

|---------------------|-------------------------------------|----------|

| 4.1                 | NVIDIA GPU 向け OpenACC コンパイラ         | 25       |

| 7.1                 | 4.1.1 設計                            | 25       |

|                     | 4.1.2 data 構文の実装                    | 26       |

|                     | 4.1.3 parallel 構文の実装                | 27       |

|                     | 4.1.4 loop 構文の実装                    | 28       |

|                     | 4.1.5 評価                            | 30       |

| 4.2                 | PEZY-SC 向け OpenACC コンパイラ            | 37       |

|                     | 4.2.1 NVIDIA GPU 向け実装からの変更点         | 37       |

|                     | 4.2.2 最適化                           | 38       |

|                     | 4.2.3 評価                            | 39       |

| 4.3                 | 関連研究                                | 44       |

| <i>⇔</i> <b>.</b> → | VI-I-I- AOO> 18 / - 0-7             | 47       |

| 第5章                 | XcalableACC コンパイラの設計・実装             | 47       |

| 5.1                 | 設計                                  | 47       |

| 5.2                 | 実装                                  | 48       |

|                     | 5.2.1 reflect 指示文                   | 48       |

|                     | 5.2.2 reduction 指示文                 | 48       |

|                     | 5.2.3 gmove 指示文                     | 49       |

| 5.3                 | 5.2.4 coarray 機能                    | 50<br>53 |

| 3.3                 | 5.3.1 Himeno Benchmark              | 53       |

|                     | 5.3.2 NAS Parallel Benchmarks CG    | 57       |

| 5.4                 | NVIDIA GPU クラスタにおけるローカルビューモデルの性能評価  | 62       |

| 3.4                 | 5.4.1 Himeno benchmark              | 65       |

|                     | 5.4.2 NAS Parallel Benchmarks CG    | 68       |

| 5.5                 | PEZY-SC クラスタにおけるグローバルビューモデルの性能評価    | 69       |

| 5.6                 | 生産性評価                               | 73       |

| 5.0                 | 5.6.1 グローバルビューモデル                   | 73       |

|                     | 5.6.2 ローカルビューモデル                    | 75<br>75 |

| 5.7                 | 考察                                  | 76       |

| 5.8                 | 関連研究                                | 70<br>77 |

| 3.0                 | 因是明儿                                | , ,      |

| 第6章                 | アプリケーションを用いた XcalableACC の性能と生産性の評価 | 79       |

| 6.1                 | 流体力学ミニアプリケーション CloverLeaf           | 79       |

|                     | 6.1.1 XACC による実装                    | 80       |

|                     | 6.1.2 評価                            | 84       |

|                     | 6.1.3 考察                            | 93       |

| v    |                   | 目次  |

|------|-------------------|-----|

| 6.2  | 格子 QCD ミニアプリケーション | 94  |

|      | 6.2.1 性能評価        | 95  |

| 6.3  | 関連研究              | 96  |

| 第7章  | 結論<br>結論          | 99  |

| 7.1  | まとめ               | 99  |

| 7.2  | 今後の課題             | 100 |

| 謝辞   |                   | 103 |

| 参考文献 |                   | 105 |

| 付録 A | 公表論文リスト           | 111 |

**vii** 図目次

# 図目次

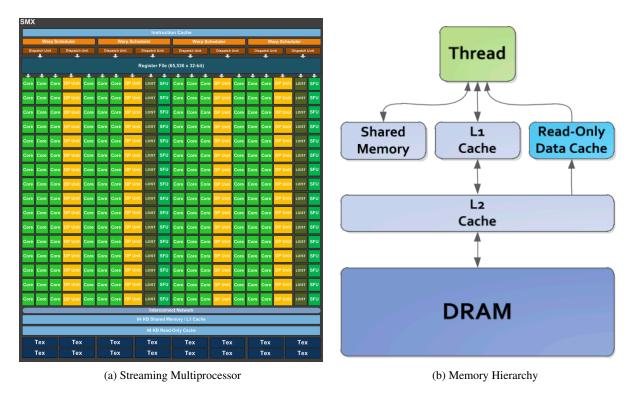

| 2.1  | Kepler アーキテクチャ (NVIDIA Kepler GK110 Architecture Whitepaper[1] より引用) 6 |

|------|------------------------------------------------------------------------|

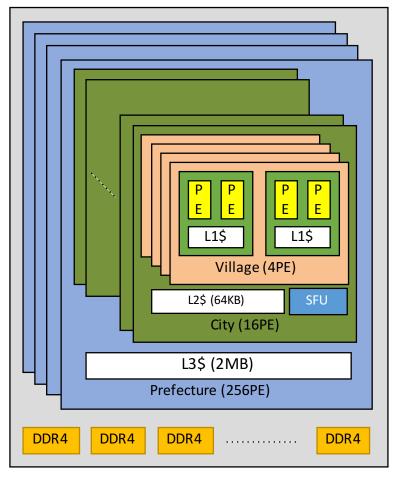

| 2.2  | PEZY-SC プロセッサの構成 8                                                     |

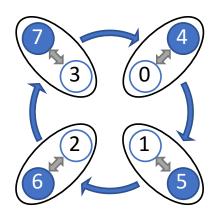

| 2.3  | PEZY-SC プロセッサのスレッドの動作モデル9                                              |

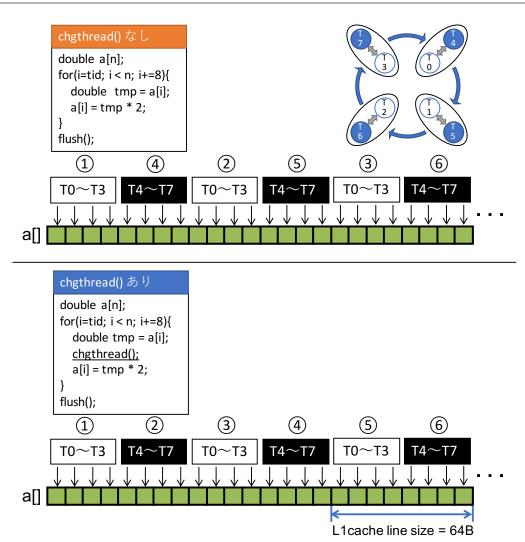

| 2.4  | PEZY-SC プロセッサにおける明示的スレッド切り替えの有無による違い 12                                |

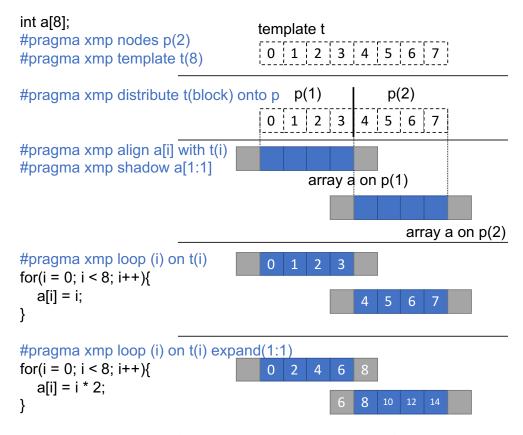

| 2.5  | XMP グローバルビューモデルによるプログラム例                                               |

| 2.6  | shadow と reflect 指示文の例                                                 |

| 2.7  | gmove 指示文の例                                                            |

| 2.8  | XMP/C における coarray の文法                                                 |

| 2.9  | post/wait 指示文の構文                                                       |

| 2.10 | XMP ローカルビューモデルによるプログラム例18                                              |

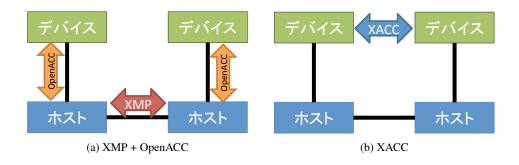

| 3.1  | デバイス間通信の記述方法                                                           |

| 3.2  | XACC グローバルビューモデルのコード例 21                                               |

| 3.3  | XACC ローカルビューモデルのコード例 22                                                |

| 4.1  | Omni OpenACC compiler のコンパイルの流れ                                        |

| 4.2  | OpenACC の並列性の CUDA へのマッピング                                             |

| 4.3  | shuffle 命令を用いたバタフライリダクション                                              |

| 4.4  | $2^{20}$ 要素のリダクションの実行時間                                                |

| 4.5  | 最適化による $2^{20}$ 要素のリダクション時間の変化                                         |

| 4.6  | CG の性能                                                                 |

| 4.7  | EP の性能                                                                 |

| 4.8  | IS の性能                                                                 |

| 4.9  | FT の性能                                                                 |

| 4.10 | MG の性能                                                                 |

| 4.11 | yield, sync, flush 指示文の構文                                              |

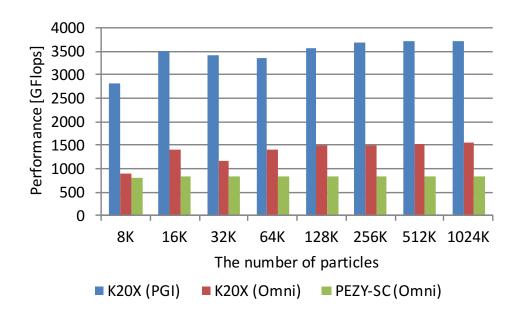

| 4.12 | PEZY-SC における N-body ベンチマークの性能                                          |

| 4.13 | PEZY-SC における NPB-CG ベンチマークの性能                                          |

| 4.14 | PEZY-SC における NPB-CG ベンチマークの性能 (OpenACC に最適化を追加) 42                     |

| 4.15 | K20X と PEZY-SC における OpenACC 版 N-body ベンチマークの性能 43                      |

| 4.16 | K20X と PEZY-SC における OpenACC 版 NPB-CG ベンチマークの性能 43         |

|------|-----------------------------------------------------------|

| 5.1  | Omni XACC compiler におけるコンパイル処理の流れ 47                      |

| 5.2  | NPB CG にて用いられる gmove (4 ノード)                              |

| 5.3  | NPB-CG の gmove の改善前 (8 ノード)                               |

| 5.4  | NPB-CG の gmove の改善後 (8 ノード)                               |

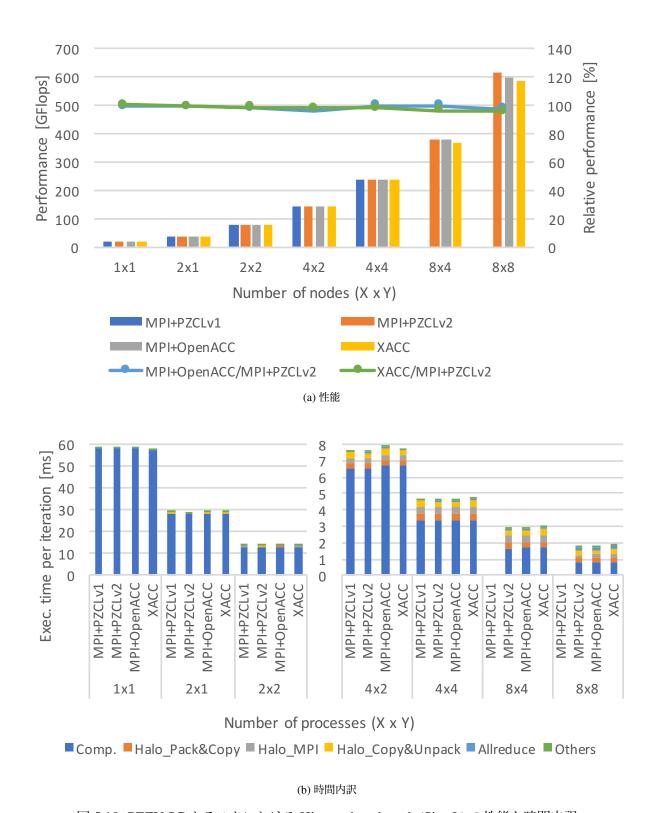

| 5.5  | Himeno Benchmark の性能                                      |

| 5.6  | Himeno Benchmark の 1 反復の実行時間の内訳                           |

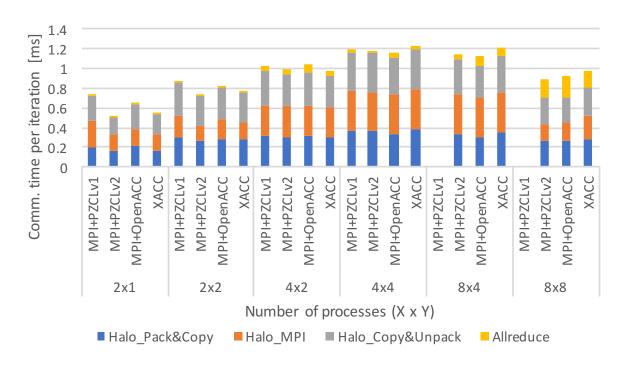

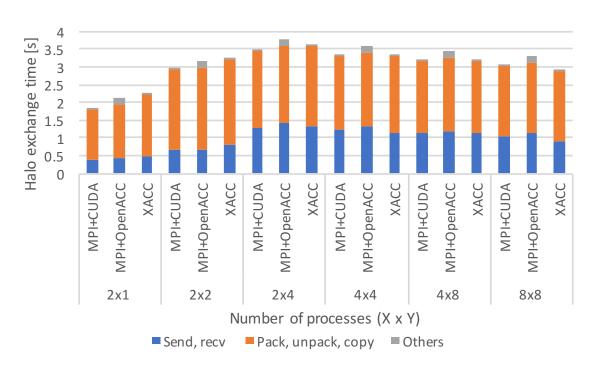

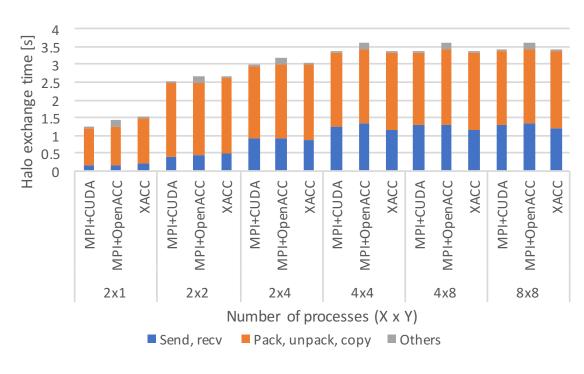

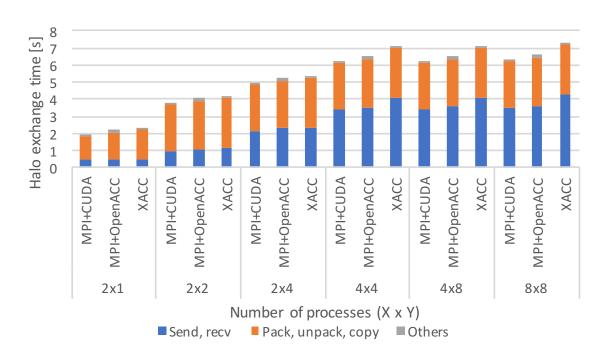

| 5.7  | Himeno Benchmark の袖通信 1 回の実行時間                            |

| 5.8  | NPB CG の性能                                                |

| 5.9  | conj_grad 関数の 1 回の実行時間の内訳                                 |

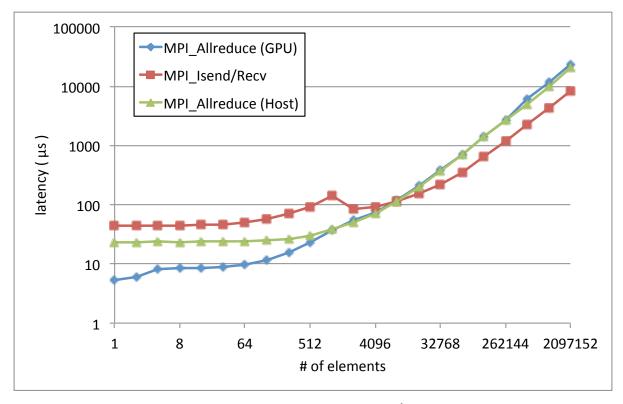

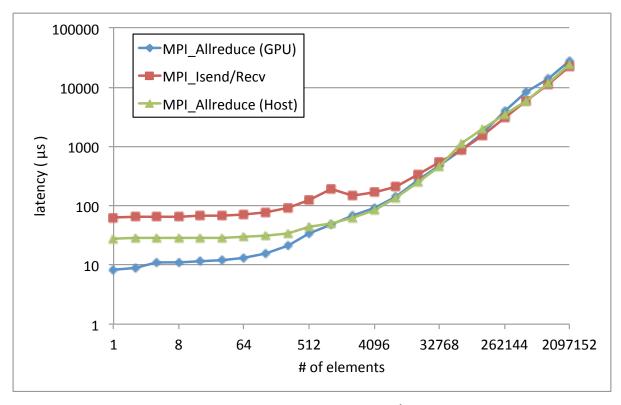

| 5.10 | Allreduce のレイテンシ (2 プロセス)                                 |

| 5.11 | Allreduce のレイテンシ (4 プロセス)                                 |

| 5.12 | Allreduce のレイテンシ (8 プロセス)                                 |

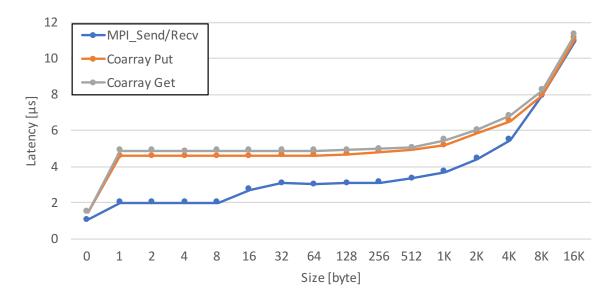

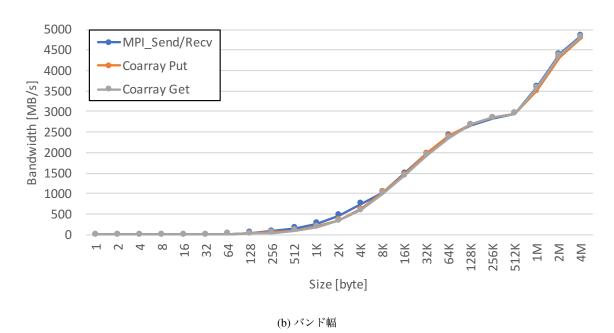

| 5.13 | MPI_Send/Recv() と coarray put/get の Ping-pong ベンチマーク性能 64 |

| 5.14 | Himeno benchmark の性能と時間内訳 (size M)                        |

| 5.15 | Himeno benchmark の性能と時間内訳 (size L)                        |

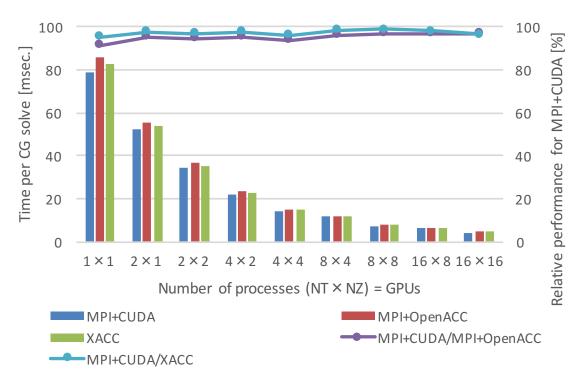

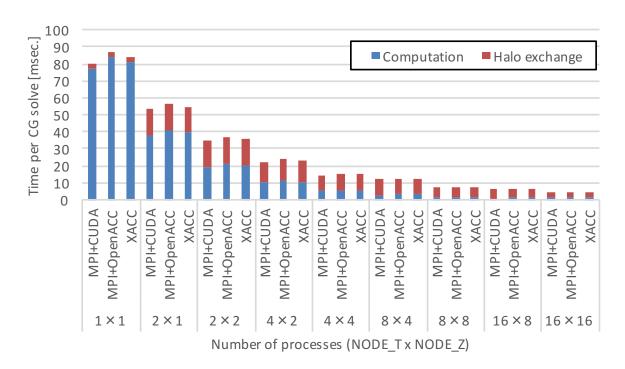

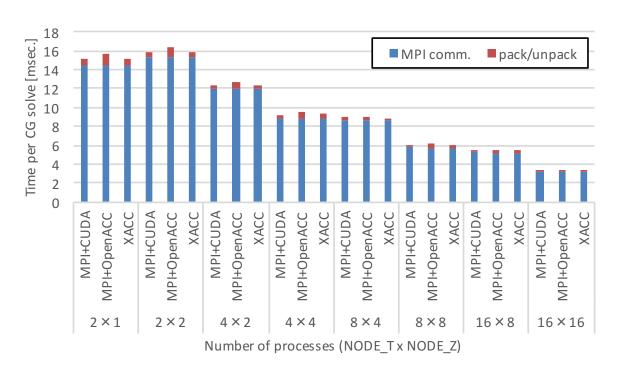

| 5.16 | NPB CG (Class C) の性能と時間内訳                                 |

| 5.17 | NPB CG (Class D) の性能と時間内訳                                 |

| 5.18 | PEZY-SC クラスタにおける Himeno benchmark (Size L) の性能と時間内訳 72    |

| 5.19 | PEZY-SC クラスタにおける Himeno benchmark (Size L) の通信時間内訳 73     |

| 5.20 | nonblock, wait_nonblock 指示文のシンタックス                        |

| 6.1  | CloverLeaf におけるスタッガード格子配置                                 |

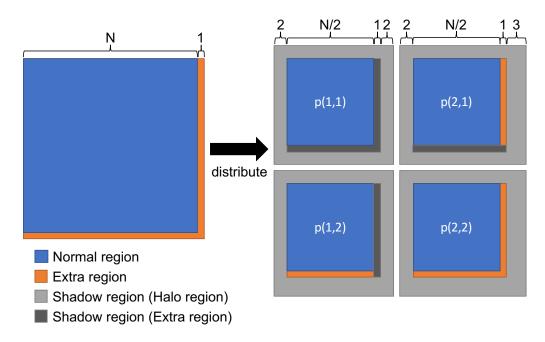

| 6.2  | CloverLeaf の XACC 実装におけるセル中心の配列の分散 81                     |

| 6.3  | CloverLeaf の XACC 実装におけるセル頂点の配列の分散 82                     |

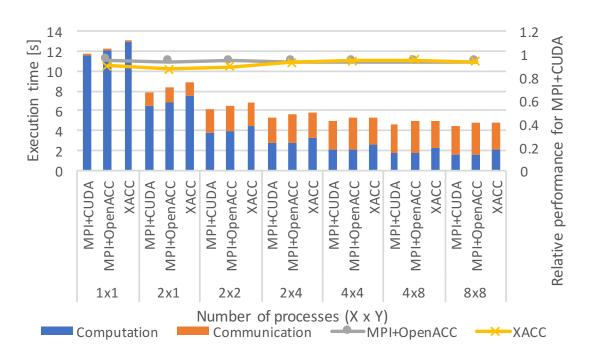

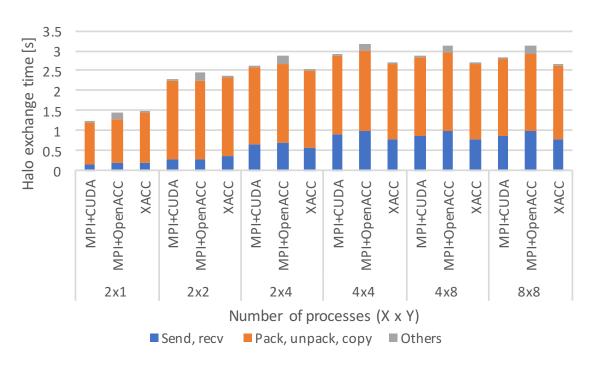

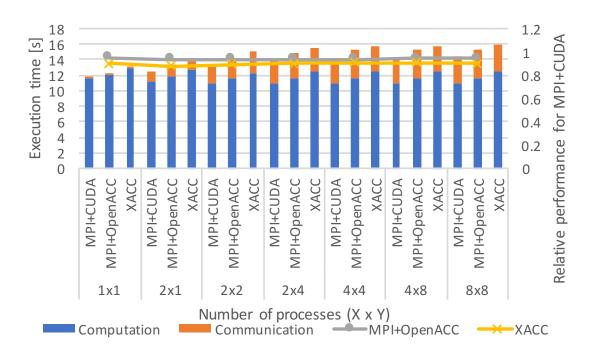

| 6.4  | $960^2$ セルのストロングスケーリングにおける実行時間                            |

| 6.5  | $3840^2$ セルのストロングスケーリングにおける実行時間                           |

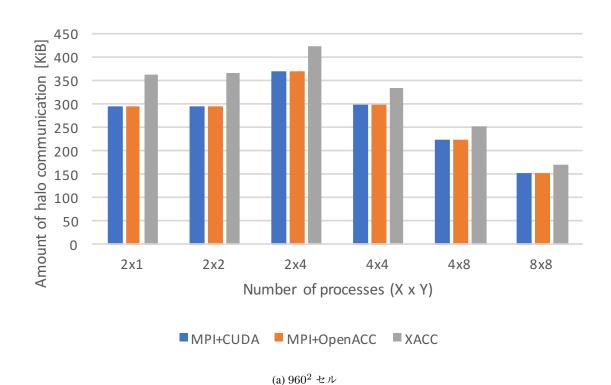

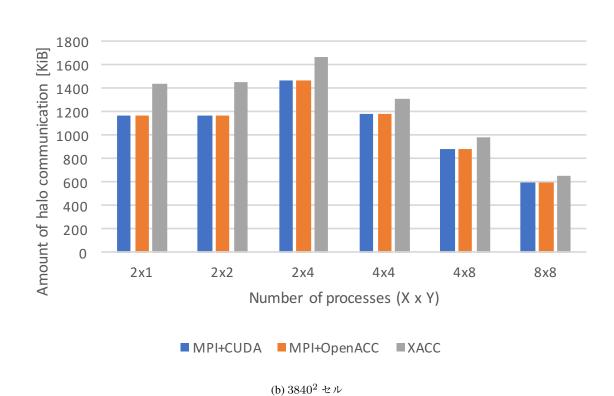

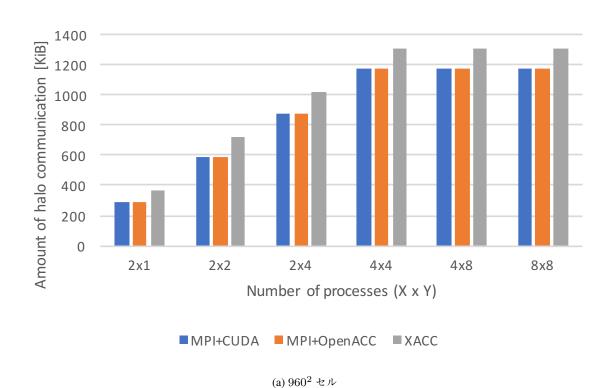

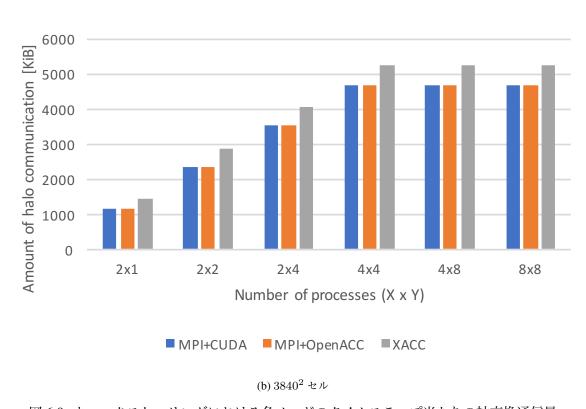

| 6.6  | ストロングスケーリングにおける各ノードのタイムステップ当たりの袖交換通信量 88                  |

| 6.7  | $960^2$ セルのウィークスケーリングにおける実行時間                             |

| 6.8  | $3840^2$ セルのウィークスケーリングにおける実行時間 91                         |

| 6.9  | ウィークスケーリングにおける各ノードのタイムステップ当たりの袖交換通信量 92                   |

| 6.10 | if 節の構文                                                   |

| 6.11 | edged-block 分散の構文                                         |

| 6.12 | reflect 指示文の offset 節の構文                                  |

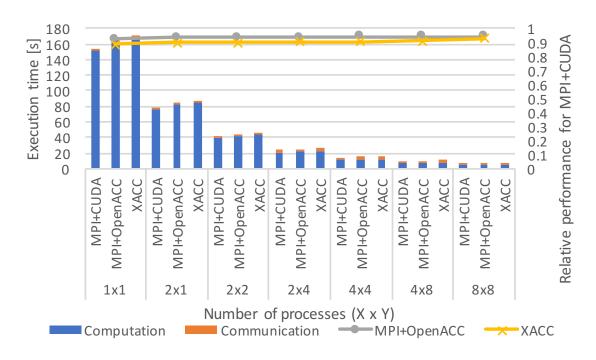

| 6.13 | 格子 QCD の CG 法 1 反復当たりの実行時間                                |

| 6.14 | 格子 QCD の CG 法 1 反復当たりの実行時間の内訳                             |

| 6.15 | -<br>格子 QCD の CG 法 1 反復当たりの袖交換時間                          |

**ix** 表目次

# 表目次

| 4.1  | NVIDIA GPU 向け OpenACC コンパイラの評価環境                | 31 |

|------|-------------------------------------------------|----|

| 4.2  | 青睡蓮のノード構成とソフトウェア                                | 40 |

| 4.3  | 青睡蓮のノード構成とソフトウェア                                | 41 |

| 4.4  | HA-PACS/TCA のノード構成とソフトウェア                       | 42 |

| 4.5  | N-Body と NPB-CG の SLOC. (内数は指示文の行数)             | 44 |

| 5.1  | HA-PACS/TCA におけるグローバルビューモデルの性能評価に用いたソフトウェアと環境変数 | 53 |

| 5.2  | Himeno Benchmark のカーネルによる占有率や性能の違い              | 56 |

| 5.3  | Himeno Benchmark の袖通信の要素数                       | 57 |

| 5.4  | CG の Class D における配列 w の長さ                       | 62 |

| 5.5  | HA-PACS/TCA におけるローカルビューモデルの性能評価に用いたソフトウェア       | 63 |

| 5.6  | 青睡蓮におけるグローバルビューモデルの性能評価に用いたソフトウェア               | 69 |

| 5.7  | Himeno Benchmark のコード行数 (内数は通信関連の行数)            | 74 |

| 5.8  | Himeno Benchmark の逐次コードへの変更行数 (指示文は除く)          | 74 |

| 5.9  | NPB CG のコード行数 (内数は通信関連の行数)                      | 75 |

| 5.10 | NPB CG の逐次コードへの変更行数 (指示文は除く)                    | 75 |

| 5.11 | Himeno benchmark と NPB CG の SLOC                | 76 |

| 6.1  | HA-PACS/TCA における CloverLeaf の性能評価に用いたソフトウェア     | 84 |

| 6.2  | CloverLeaf の各コードの SLOC と DSLOC                  | 89 |

| 6.3  | 格子 OCD の評価に使用したソフトウェア                           | 95 |

**xi** ソースコード目次

# ソースコード目次

| 2.1 | CUDA によるホストコード例                                    | 7  |

|-----|----------------------------------------------------|----|

| 2.2 | CUDA によるデバイスコード例                                   | 7  |

| 2.3 | PZCL カーネルの例                                        | 10 |

| 2.4 | OpenACC のコード例                                      | 13 |

| 4.1 | data 構文の例                                          | 26 |

| 4.2 | data 構文の変換例                                        | 26 |

| 4.3 | parallel 構文の例                                      | 28 |

| 4.4 | parallel 構文の変換例                                    | 28 |

| 4.5 | loop 構文の例                                          | 30 |

| 4.6 | loop 構文の変換例                                        | 30 |

| 5.1 | アクセラレータ上の coarray 宣言                               | 51 |

| 5.2 | アクセラレータ上の coarray 宣言を変換したコード                       | 51 |

| 5.3 | coarray によるアクセラレータメモリ間の put 通信                     | 52 |

| 5.4 | coarray によるアクセラレータメモリ間の put 通信を変換したコード             | 52 |

| 5.5 | XACC で記述した Himeno Benchmark                        | 54 |

| 5.6 | XACC による NPB CG のコード                               | 58 |

| 5.7 | XACC ローカルビューモデルにおける Himeno benchmark の袖交換 (ik 平面)  | 65 |

| 5.8 | NPB CG の XACC ローカルビューモデルによる通信                      | 68 |

| 6.1 | CloverLeaf の XACC 実装における宣言・確保                      | 80 |

| 6.2 | CloverLeaf の XACC 実装における計算                         | 82 |

| 63  | ソースコード 6.2 の XACC コードを Omni XACC compiler が変換したコード | 84 |

1 第1章 序論

## 第1章

# 序論

#### 1.1 研究背景

ハイパフォーマンスコンピューティング (HPC) の分野において、スーパーコンピュータの性能は年々向 上しており、すでにペタスケールが達成され、次のマイルストーンであるエクサスケールの達成に向けて 世界各国で研究・開発が進められている。その際に性能の向上に加えて、スーパーコンピュータに対する 現実的な電力供給量には限りがあるため消費電力あたりの性能も向上させる必要がある.現在,この目標 を達成するために演算加速機構 (アクセラレータ) の活用が盛んに行われている.CPU は少数の性能の高 いコアを持つ一方で,アクセラレータは数十から数千個の性能の低いコアと高バンド幅のメモリを持つこ とで、より高い性能と省電力を実現している。スーパーコンピュータの性能ランキングである Top500[2] をみると 2017 年 11 月では,第 2 位の Tianhe-2 はカード型の Intel Xeon Phi,第 3 位の Piz Daint と第 5位の Titan は NVIDIA Tesla, 第4位の Gyoukou は PEZY-SC をアクセラレータとして搭載している. Top500 のシステムのうち約 20% の 102 システムにおいてアクセラレータが用いられており, NVIDIA GPU を搭載したシステムがそのうちの 85% と高いシェアを占める。またスーパーコンピュータの省電力 ランキングである Green500 においては,上位 10 システムのうち 4 システムが PEZY-SC,残り 6 システ ムが NVIDIA Tesla を搭載している。特に上位 3 システムは全て PEZY-SC を搭載しており、高い電力性 能比を達成している.2018 年に稼働予定の産業技術総合研究所の人工知能処理向け大規模・省電力クラ ウド基盤 (AI Bridging Cloud Infrastructure, ABCI) やオークリッジ国立研究所の Summit もアクセラレー タとして NVIDIA Tesla を搭載すると発表されており,今後も同様のシステムは増加する見込みである. アクセラレータのプログラミング方法を見てみると, NVIDIA GPU に対しては同社が提供する専用 の開発環境 Compute Unified Device Architecture(CUDA)[3] が広く普及している。NVIDIA GPU のアー キテクチャに合わせた記述と成熟したコンパイラにより,高性能なプログラム開発が可能である.ま たアクセラレータを含むヘテロジニアス環境向けの並列計算フレームワークである Open Computing Language(OpenCL)[4] もその汎用性から多様なアクセラレータで用いられている。これら2つのプログ ラミング方法では,どちらもアクセラレータを用いて計算をするのに必要なアクセラレータ上のメモリの 確保やデータ転送などの事前・事後処理を API 関数で記述し、実際にアクセラレータ上の多数のコアで 行う並列処理を拡張された C 言語で記述する必要があり、プログラミングが煩雑である. 加えて、CUDA

の記述は NVIDIA GPU でしか動作せず、また OpenCL も各アクセラレータに適切な記述が異なるため実

1.1 研究背景 2

際の可搬性は高くない。近年でも PEZY-SC が新たなアクセラレータとして登場しており今後も様々なアクセラレータが登場することを考えると、アクセラレータごとに大幅にプログラムを書き換えなければならないこれらの記述は可搬性の低さの面で問題がある。そこで、これらの問題の解決のために指示文ベースのプログラミングモデルがいくつか提案されている。研究では OpenMPC や hiCUDA、商用コンパイラでは CAPS の HMPP、PGI の PGI Accelerator Programming Model などがある。逐次コードに指示文を追加する形でアクセラレータへの処理のオフロードを記述するため、逐次コードをベースに簡易に記述できるうえ、高いレベルでの記述であるため特定のアクセラレータへの依存が低く可搬性が高いという特徴がある。その中でも 2011 年に CAPS・Cray・NVIDIA・PGI が策定した OpenACC[5] は、アクセラレータ向け指示文としては初の標準仕様であり、CAPS・Cray・PGI コンパイラがこれをサポートしたことによって HPC 分野において広く認知された。しかしながら、OpenACC の登場当初はオープンソースのコンパイラ研究基盤がなく、商用コンパイラでも GPU のような一般的なアクセラレータのみの対応で最適化も不十分であった。なお、OpenACC だけでなく 2013 年には OpenMP[6] でも仕様 4.0 でアクセラレータプログラミングが導入されたため、指示文によるアクセラレータプログラミングは今後より一般的になると考えられる。

スーパーコンピュータやクラスタのような複数ノードを用いる分散メモリ環境におけるプログラミングでは、従来 Message Passing Interface (MPI) が通信や同期に用いられている。逐次コードと比較して、データや処理の分散と通信が必要であるため非常に多くの処理を記述しなければならない。そこで MPI に代わるプログラミングモデルとして Partitioned Global Address Space (PGAS) モデルが提案されている。PGAS モデルは分散メモリ環境において仮想的な大域名前空間をユーザに提供するモデルで、データに統一的にアクセスできるため記述が容易である。プログラミング言語で PGAS モデルを採用している代表例として既存言語の拡張である UPC, X10, Coarray Fortran, XcalableMP[7]、独自言語の Chapel がある。特に XMP では逐次コードへ指示文を追加するモデルと、coarray を用いて通信を記述するモデルの2種類の記述が可能である。またライブラリによる実装としては OpenSHMEM が代表的である。

演算加速機構を持つ並列システム向けのアプリケーション開発では、分散メモリプログラミングに加えてアクセラレータプログラミングも行う必要がある。従来の CUDA もしくは OpenCL と MPI の組み合わせによるプログラミング方法では複雑さがさらに増し、開発期間の増加やメンテナンス性の低下といった課題がある。加えて、主な演算をアクセラレータで実行するので通信するデータがアクセラレータ上にあることが多く、アクセラレータ間の通信が重要となる。例えば NVIDIA GPU では GPUDirect RDMA(GDR)[8] により PCI Express 経由で直接 NIC にデータを転送することで低レイテンシの通信が可能である。そのようなアクセラレータ独自の高速な通信機能の利用が大規模な並列プログラムにおけるスケーラビリティの点で重要となるが、特別な通信ライブラリの使用が必要な場合がありプログラミングはさらに煩雑になる。より簡易で可搬性の高い記述として、分散メモリプログラミングに PGAS を、アクセラレータプログラミングに指示文を用いることが考えられる。しかしながら、先に挙げた XMP と OpenACC により記述を行う場合にはアクセラレータ間の通信を記述する方法がなく、ハードウェアの機能を活かせず性能が低下する可能性がある。

第1章 序論

#### 1.2 研究目的

本研究の目的は演算加速機構を持つ並列システムを活用するために、プログラミングを容易にして生産性を向上させるとともに高性能を達成できるプログラミング環境を提案することである。この目的の達成のため、筑波大学と理化学研究所の共同で PGAS 言語 XcalableACC (XACC) [9] を提案する。XACCは XMPと OpenACCの統合であり、XMPと OpenACCによって高い生産性と可搬性を実現すると同時に、新たにアクセラレータ間の通信の記述を提供することで XMPと OpenACCを単に組み合わる場合よりも高速な通信を可能とする。XACCの生産性や性能を評価するため、対象システムとして最も普及している NVIDIA GPU クラスタと高電力効率の PEZY-SC クラスタを用いる。XACCで利用する OpenACCのコンパイラに関して、NVIDIA GPU において高い性能を達成するため OpenACC コンパイラの設計・実装および最適化を行い、ベンチマークを用いて既存の OpenACC コンパイラを設計・実装および最適化を行い、ベンチマークを用いて既存の OpenACC コンパイラを設計・実装および最適化を行い、ベンチマークを用いて PEZY-SC 向けに直接記述する場合と性能・生産性を比較する。そしてXACCのコンパイラを設計・実装し、ベンチマークやアプリケーションを用いて従来の記述と比較して性能・生産性を評価する。本研究の貢献を以下に示す。

- オープンソースの source-to-source OpenACC コンパイラを設計・実装した。NVIDIA GPU 向け実装ではループ並列化以外は元のコードを維持して変換することで CUDA コンパイラによる最適化が十分に働き、さらにメモリプールの利用や Kepler アーキテクチャ向けにリードオンリーキャッシュやリダクションに shuffle や atomic 命令を利用することで、商用コンパイラの最大 2.8 倍の性能を達成した。PEZY-SC 向け実装では kernels 指示文を単一カーネルに変換することでカーネル起動コストを削減でき、またスレッド切り替えや同期やフラッシュ用の拡張指示文を追加することでユーザによるチューニングを可能とし、PZCL による記述と同等の性能を達成した。加えてPEZY-SC 向けの初の OpenACC コンパイラであり、既存 OpenACC プログラムの利用や PZCL よりも簡易な記述を可能にしたことにより生産性の向上に寄与した。

- XACC ローカルビューモデルにおけるアクセラレータメモリ上の coarray の宣言とそれに対する 通信の記述方法,および同期削減の指示文を提案した。そして XACC グローバルビューモデルを NVIDIA GPU と PEZY-SC クラスタ向けに,ローカルビューモデルを NVIDIA GPU クラスタ向け に実装した。Himeno benchmark と NAS Parallel Benchmarks (NPB) CG による評価から,グローバルビューモデルは逐次コードに指示文の追加,ローカルビューモデルは coarray の配列代入文形式の通信により簡易に記述可能であり,MPI+OpenACC と同等の性能が得られることを示した。また,Himeno benchmark においては NVIDIA GPU と PEZY-SC クラスタ向けに XACC でほぼ同様に記述できることを示した.

- 流体力学と格子 QCD のミニアプリケーションを用いた評価により XACC グローバルビューモデルが実アプリケーションにおいても逐次コードをベースに簡易に記述でき、NVIDIA GPU クラスタにおいて従来の MPI+CUDA や MPI+OpenACC による記述と近い性能を得られることを示した.

1.3 構成 4

#### 1.3 構成

本稿の続きは次に示す構成となっている。2章では研究の背景として対象とするアクセラレータのアーキテクチャや開発環境、提案する PGAS 言語 XACC のベースとなる OpenACC および XMP について紹介する。3章では演算加速機構を持つ並列システム向けに提案する PGAS 言語 XACC の説明をする。4章では XACC のベースとして用いる OpenACC のコンパイラの設計と実装を解説し、ベンチマークを用いて評価を行う。5章では XACC のコンパイラの設計と実装を解説し、ベンチマークによる性能・生産性の評価を行う。6章ではアプリケーションを用いて XACC の生産性や性能の評価を行う。7章では結論と今後の課題を述べる。

第2章 研究の背景

## 第2章

# 研究の背景

本章では、本研究で開発や評価の対象としたアクセラレータである NVIDIA GPU と PEZY-SC のアーキテクチャ、およびそれらの開発環境である CUDA と PZCL によるプログラミング方法を説明し、PGAS 言語 XACC のベースとなる OpenACC および XMP のモデルや記述について解説する.

#### 2.1 NVIDIA GPU

NVIDIA GPU の HPC 向け製品である Tesla シリーズのアーキテクチャは Tesla・Fermi・Kepler・Maxwell・Pascal そして最新の Volta へと変遷している。ここでは本研究で実装・評価に用いた Kepler アーキテクチャについて解説する。GPU チップ内は複数のストリーミング・マルチプロセッサ (SMX) により構成されている。SMX の数は同世代でも製品によって異なるが Kepler では最大 15 個の SMX が 搭載されている。Kepler アーキテクチャでは図 2.1a に示すように SMX 内に 192 個の CUDA コアがあり,各 CUDA コアには整数演算ユニット (ALU) がある。また同様に SMX 内には 64 個の浮動小数点演算ユニット (FPU) と 32 個の特殊関数ユニット (SFU) がある。Kepler では単精度と倍精度の両方で Fused Multiply-Add (FMA) 命令に対応している。FMA とは浮動小数数の乗算と加算  $(a+b\times c)$  を一度に行う命令であり,丸め処理が一度であるため精度が高くかつ高速に演算が可能である。スレッドの実行は 32 スレッドをまとめたワープという単位で実行され,ワープ内の 32 スレッドは同時に同じ命令を実行する。Kepler では SMX 内にワープスケジューラが 4 つあるため,同時に 4 つのワープを実行できる。また各スケジューラには 2 つの命令ディスパッチユニットがあり,1 ワープの命令を最大で 2 つ同時に実行可能である。

図 2.1bに Kepler アーキテクチャにおけるメモリ階層を示す。GPU ではキャッシュや Shared メモリを利用することでデータアクセスのレイテンシ,スループットを向上させることができる。Shared メモリは SMX 上にあるオンチップメモリで SMX 内のスレッドが共有して使えるメモリである。Shared メモリと L1 キャッシュは各 SMX に合わせて 64 KB あり,16 KB / 48 KB,32 KB / 32 KB,48 KB / 16 KB の3 通りの設定がある。Shared メモリを多用するカーネルでは Shared メモリを多く,そうでない場合は L1 キャッシュを増やしてキャッシュヒット率を高めるというようにカーネルによって設定を変えることでリソースを有効利用できる。また Kepler では新たに各 SMX に 48 KB の Read-Only Data Cache が導入された。Fermi 世代ではテクスチャデータのキャッシュとしてテクスチャユニットからしかアクセスできな

2.2 CUDA 6

図 2.1: Kepler アーキテクチャ (NVIDIA Kepler GK110 Architecture Whitepaper[1] より引用)

かったが、Kepler では通常のデータでも利用できるようになったため、以前よりも利用が容易になった。 L1 キャッシュや Read-Only Data Cache と DRAM の間には  $1.5\,\mathrm{MB}$  の L2 キャッシュも用意されている.

#### 2.2 CUDA

CUDA は NVIDIA が提供している NVIDIA GPU 用の開発環境である。CUDA による GPU プログラミングでは主にホスト側から GPU を操作するためのホストコードと GPU 側で実行するデバイスコードの 2 つを記述する必要がある。

#### 2.2.1 ホストコード

CUDA によるホストコード例をソースコード 2.1 に示す。GPU は独自に高バンド幅のメモリ (GDDR や HBM) を持っているため、基本的には GPU メモリ上のデータに対して処理を行う。そのために GPU で処理を行う準備として GPU メモリの確保と必要データの転送を行う。その後 GPU の処理を記述したカーネルを起動し、その処理の完了を待機する。最後に、処理結果を GPU メモリからホストメモリに転送し、GPU メモリを解放する。これらのメモリ操作は CUDA が提供する Runtime API を通して行うことができ、GPU メモリの確保・解放には cudaMalloc() と cudaFree() を、メモリコピーには cudaMemcpy()を用いる。GPU による処理は後述するデバイスコードで記述しておき、任意のスレッド数を指定して起動すると GPU 上で実行される。CUDA では多数のスレッドを管理するために 3 次元のグリッドやブロッ

クによる階層モデルが用意されている。グリッドはブロックの集まりで最大の大きさは Kepler アーキテクチャでは  $(2^{31}-1)\times 65535\times 65535$  である。ブロックはスレッドの集まりで Kepler アーキテクチャでは最大 1024 スレッドまでのスレッドブロックが実行できる。各スレッドからは属するグリッドやブロックのインデックスを取得可能で,カーネル関数ではそれらを用いてスレッドごとに異なる処理を実行するよう記述する。カーネルを起動するには "func-name <<< gridDim, blockDim >>> (arg0, arg1, ...)" として関数呼び出しにグリッドサイズとブロックサイズ指定を加えて呼び出す。ソースコード 2.1 では 12 行目で  $128\times 1\times 1$  の大きさのスレッドブロックを総スレッド数が配列サイズ以上となるグリッド数でカーネルを起動している。

#### 2.2.2 デバイスコード

CUDA では GPU 上で実行するプログラムをカーネルと呼び、ソースコード 2.2 に示すように関数として記述する. 修飾子\_global\_により通常の関数とは区別される. このカーネルをホストスレッドから起動することで、デバイス上で多数のスレッドで実行される. カーネルではスレッドブロック中のスレッド番号 (threadIdx)、グリッド中のブロック番号 (gridIdx)、スレッドブロックのサイズ (blockDim) からそのスレッドで処理すべきインデックスを求めて配列に値を代入する

#### ソースコード 2.1: CUDA によるホストコード例

```

1 void func(int *host_a, int n)

2 {

3 int *device_a;

4 // allocate device memory

5 cudaMalloc((void**)&device_a, n * sizeof(int));

6 // copy host memory to device memory

7

cudaMemcpy(device_a, host_a, n * sizeof(int), cudaMemcpyHostToDevice);

8

9 int num_threads = 128;

dim3 grid((n-1)/num threads+1, 1, 1), block(num threads, 1, 1);

10

11

// launch kernel

12 kernel<<<grid, block>>>(device_a, n);

13

14 // copy device memory to host memory

15

cudaMemcpy(host_a, device_a, n * sizeof(int), cudaMemcpyDeviceToHost);

16

// free device memory

17

cudaFree(device_a);

18 }

```

#### ソースコード 2.2: CUDA によるデバイスコード例

```

1 __global__

2 void kernel(int *a, int n)

3 {

4   int i = blockDim.x * blockIdx.x + threadIdx.x;

5   if(i < n) {

6    a[i] = i * i;</pre>

```

2.3 PEZY-SC **8**

図 2.2: PEZY-SC プロセッサの構成

#### 2.3 PEZY-SC

PEZY-SC は PEZY Computing が開発したメニーコアプロセッサである。2017 年には第 2 世代の PEZY-SC2 が登場しているが、ここでは本研究で使用した第 1 世代の PEZY-SC について解説する。図 2.2 にプロセッサの構成を示す。1 つのプロセッサには 1024 個の Processing Element (PE) があり、1PE では8 スレッドを実行することができる。したがって、1 プロセッサで最大 8192 スレッドを同時に実行することが可能である。また GPU とは異なり各スレッドは MIMD で動作するという特徴があり、GPUでは各スレッドで条件分岐先が異なると性能低下が起きるが PEZY-SC では問題がない。

マルチプロセッサの構成は階層的な構造になっており、小さい順に PE, Village, City, Prefecture と呼ばれる. 1 つの PE には 8 スレッド分のレジスタ、16 KB のローカルメモリ、2 つの ALU、2 つの FPU 等が含まれる。Village は 4 つの PE および 2 PE 毎の 2 KB L1 キャッシュで構成される。City は 4 つの Village と 1 つの SFU、1 つの 64 KB L2 キャッシュで構成され、プログラム実行時には City の単位でス

9 第2章 研究の背景

図 2.3: PEZY-SC プロセッサのスレッドの動作モデル

レッドを実行する必要がある。Prefecture は 16 個の City と 2 MB L3 キャッシュからなる。1 つのプロセッサには 4 つの Prefecture があり、全体で 1024 個の PE が含まれる。スレッドは全体同期もしくは各階層における細粒度の同期が可能である。また L1–L3 キャッシュではコヒーレンシがとられないため、あるスレッドが書き込んだデータを他のスレッドが読む場合には適切な階層レベルでキャッシュされたデータをフラッシュする必要がある。またチップ上に 8 チャネルの DDR4 メモリが接続されている。

1 つの PE で実行される 8 スレッドは図 2.3 に示すように、実際には 4 組のスレッドペアとなっている。 はじめは各ペアのどちらか片側のスレッドだけがラウンドロビンで実行され、同期命令もしくはスレッド 切り替え命令によって反対側のスレッドが実行されるようになる。

#### 2.4 PZCL

PZCL は PEZY Computing が提供している PEZY-SC プロセッサ用のプログラミング環境である. OpenCL の方言であり、ホストコードは通常の OpenCL と同様であるが、デバイスコードは OpenCL C でなく通常の C++ が用いられる.

#### 2.4.1 ホストコード

ホストコードは OpenCL と同様に C 言語の API により記述する。現在の PZCL では OpenCL 1.1 相当の機能が提供されており、既存の OpenCL コードの大部分はそのまま使用することができる。通常の OpenCL コードと異なる点について以下に述べる。多くの OpenCL コードでは実行時にカーネルコードをコンパイルするオンラインコンパイルを用いるが、PZCL では事前にカーネルコードをコンパイルしておくオフラインコンパイルのみに対応しているため、カーネルファイルの読み込みの箇所の書き換えが必要になる場合がある。次にカーネル起動時にいくつかの制限がある。実行する全スレッド数である global\_work\_size は 128 の倍数でなければならず、これは City の単位でスレッドを実行するためである。また OpenCL の work-group に相当するのが PE であるため、local\_work\_size は各 PE 内のスレッド数である 8 で固定である。加えて、OpenCL では work item の形状は少なくとも 3 次元まで指定可能であるが、PZCL では 1 次元しか指定できない。最後に、global\_work\_size の上限は特に決められていないが、

2.4 PZCL 10

全スレッド数の8192を超えて指定した場合にはカーネルが複数回起動することになるため、8192以下にすることが推奨されている。

#### 2.4.2 デバイスコード

デバイスコードは C/C++ を用いて、OpenCL C とは異なる方法で記述する。ソースコード 2.3 に PZCL によりベクトル加算を行うコードの例を示す。

#### ソースコード 2.3: PZCL カーネルの例

```

1 void pzc_vector_add(int n, int *a, int *b, int *c)

2 {

int g_work_size = get_maxpid() * get_maxtid();

4

int g_work_id = get_pid() * get_maxtid() + get_tid();

5

6

for(int i = g_work_size; i < n; i += g_work_id) {</pre>

7

c[i] = a[i] + b[i];

8

chgthread();

9

10

11

flush();

12 }

```

ホストから起動するカーネルは OpenCL や CUDA と同様に関数として定義する。関数名のプレフィックスを "pzc\_" とすることでカーネル関数であることを指定する。例ではカーネル関数名を "pzc\_vector\_add" としている。OpenCL ではカーネルパラメータに--global や--local の指定が必要になるが、PZCL では必要ない。パラメータのポインタはグローバルメモリのポインタとして扱われる。例では,a,b,c はグローバルメモリのポインタで,n は値として渡される。また work-group 内で共有するメモリ (OpenCL で言うところのローカルメモリ) を定義するインタフェースはない。

カーネル関数内では、PE やスレッドの ID を用いて処理を並列に行う。PE の ID は get\_pid() により、PE 内のスレッドの ID は get\_tid() により取得できる。これらは OpenCL における get\_group\_id(0) や get\_local\_id(0) に相当する。また PE 数は get\_maxpid() により、PE 内のスレッド数は get\_maxtid() により取得できる。これらは OpenCL における get\_num\_groups(0) や get\_local\_size(0) に相当する。

PZCL では PEZY-SC 用にいくつかの組み込み関数を提供している。まず、chgthread() は実行をスレッドのペアの逆側に切り替える命令である。sync() はプロセッサ内のすべてのスレッドで同期する。また、細粒度な同期として sync L1()、sync L2()、sync L3() がそれぞれ Village、City、Prefecture 内の同期として提供されている。"L1"-"L3" はそのキャッシュを共有するレベルで同期するという意味である。さらに、flush() は全スレッド同期と全キャッシュフラッシュを行う。こちらも同様に細粒度のフラッシュとして、flush L1()、flush L2()、flush L3() が提供されている。コード例ではカーネルの最後に flush() を実行することで、キャッシュされている配列 c の値をメモリにフラッシュする。これを行わないとカーネル実行後にデバイスメモリ上に結果が残らず、正しく結果が得られない。PZCL においてはこれらの組み込み関数によって高速化することが重要になる。ここでは本研究で用いた 2 つの最適化について説明する。

第2章 研究の背景

#### カーネルマージ

CUDA のスレッドブロック間もしくは OpenCL の work-group 間ではカーネル実行中に同期を取ることができない。したがって全体同期が必要な部分ではカーネルを分割してカーネルを一度終了させることで全体同期を実現するが、カーネルを起動するオーバーヘッドの増加が問題となる。PZCL では起動する global\_work\_size を 8192 以下にした場合には sync() 命令によりスレッド全体での同期が可能であるためカーネルを分割しないで済む。

#### 明示的スレッド切り替え

コード例のようにループ中で chgthread() により明示的に実行を逆側のスレッドに切り替えることにより 2 つの効果がある.

- 1. メモリアクセスなど時間のかかる命令のレイテンシ隠蔽. 逆側のスレッドに実行を移すことでストール時間を短くする.

- 2. キャッシュヒット率の向上. ペアのスレッドはメモリ上の近い位置をアクセスすることが多いため、両側のスレッドが同じように動作することでキャッシュの利用率を高めることができる。

図 2.4 にスレッド切り替えの有無による動作の違いを示す.図の上側が明示的なスレッド切り替えなし、下側がありの場合を示している.図中の丸付き数字は実行される順番を示している.明示的なスレッド切り替えなしの場合では,最初はスレッド 0-3 のみがループの本体を実行する.その後,ループを抜けて flush() に到達した際に,暗黙的にスレッド切り替えが発生する.そしてスレッド 4-7 がループを実行して flush() に到達して処理が終了する.この場合メモリアクセスは double型 4要素,つまり 32byte ごとに飛び飛びのアクセスになり,L1 キャッシュは読み込んでもその半分しか利用されない.次に切り替え命令ありの場合では,はじめにスレッド 0-3 が配列 a[] にアクセスするがその後にスレッドが切り替わり,スレッド 4-7 が配列にアクセスする.これをループが終わるまで繰り返して,全スレッドがほぼ同時に flush() に到達する.表と裏のスレッドがほぼ同時に処理が進むことでキャッシュが有効に利用できるうえ,メモリロード後にスレッド切り替えを入れることでメモリアクセスによるストールが軽減できる.

### 2.5 OpenACC

OpenACC は C・C++・Fortran コードの一部をアクセラレータにオフロードするための指示文ベースのプログラミングモデルである。2011 年 11 月に CAPS・Cray・NVIDIA・PGI により策定され、最新の仕様は 2017 年 11 月に策定された version 2.6 である。データや演算のオフロードを指示文で簡易に記述できるため習得が容易で、既存の逐次コードをベースに開発できるため生産性が高い。またアクセラレータの種類に依存しない記述であるため、コードの可搬性も維持される。

#### 2.5.1 実行モデル

OpenACC ではホストから GPU のようなホストに接続されたアクセラレータに処理を行わせることが可能である. コード中の負荷の高い部分を parallel または kernels 指示文で指定すると, その

2.5 OpenACC

図 2.4: PEZY-SC プロセッサにおける明示的スレッド切り替えの有無による違い. 上側が明示的スレッド切り替え無し, 下側が有りの場合を示す. 丸付き数字は実行順序を示す.

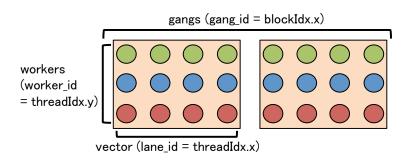

処理はアクセラレータでカーネルとして実行される。OpenACC では上位から gang, worker, vector の 3 段階の並列性が存在する。gang は粗粒度の並列性で完全に並列に動作し gang 間での同期は基本的にできない。worker は細粒度の並列性である。各 gang は 1 つ以上の worker を持ち,各 worker では vector を用いてベクトル演算を行うことができる。これら 3 つの並列性が実際のアクセラレータの演算器とどのように対応付けられるかはコンパイラ依存である。カーネル領域のプログラムは何も指定がなければ gang, worker, vector はそれぞれ gang-redundant,worker-single,vector-single モードで実行される。gang-redundant モードではすべての gang が同じ処理を重複して行う。worker-single 及び vector-single モードでは 1 つの worker,1 つの vector レーンのみが処理を実行する。並列化可能なループに対して 100p 指示文で並列化を指定した際には,gang-partitioned,worker-partitioned,vector-partitioned モードに移行し,並列実行を行う。

第2章 研究の背景

#### 2.5.2 メモリモデル

現在多くのアクセラレータでは物理的または仮想的にホストメモリとアクセラレータメモリが分かれている。OpenACCのモデルでは、ホストとアクセラレータのメモリ間のコピーはコンパイラによって暗黙に管理される。しかしながら、指示文によりメモリの管理をすることも可能で、data指示文などによってデータの生存期間を明示することで、不要なメモリ確保やデータ転送を削減することができる。アクセラレータが実際にホストメモリと別のメモリを持つ場合には、指定されたようにデータ確保を行い、アクセラレータとホストがメモリを共有している場合には確保や移動は行わない。

#### 2.5.3 プログラム例

OpenACC 指示文を追加した C 言語のコードをソースコード 2.4 に示す。4 行目では data 指示文を使用して 5-10 行目においてアクセラレータメモリに配列 a[] と b[] を確保するよう明示する。配列 a[] の値はデバイスで参照されるが更新はされないため,copyin 節を用いて領域の最初にホストメモリからアクセラレータメモリへコピーするよう指定している。他方で配列 b[] の値はデバイスで更新されるが参照はされないため,copyout 節を用いて領域の最後にアクセラレータメモリからホストメモリへコピーするよう指定している。6 行目では parallel loop 指示文を用いて変数 i に関するループをアクセラレータで並列実行するよう指定している。以上の指示文からコンパイラはこのループをアクセラレータで実行するよう適切に変換を行う。

#### ソースコード 2.4: OpenACC のコード例

```

1 #define N 1024

2 int main() {

3    int a[N], b[N];

4 #pragma acc data copyin(a) copyout(b)

5    {

6 #pragma acc parallel loop

7    for(int i = 0; i < N; i++) {

8        b[i] = a[i] + 1;

9    }

10    }

11 }</pre>

```

#### 2.6 XcalableMP

XcalableMP (XMP) は分散メモリシステム向けに C と Fortran を拡張した PGAS 言語であり、PC クラスタコンソーシアム [10] の XMP 規格部会により仕様が策定されている。XMP は 2 つのプログラミングモデルを提供しており、一つは逐次コードに指示文を追加することによりノード全体の動作を記述するグローバルビューモデルで、もう一つは MPI プログラミングのように各ノードの動作を記述するローカルビューモデルである。

2.6 XcalableMP

図 2.5: XMP グローバルビューモデルによるプログラム例

#### 2.6.1 グローバルビューモデル

グローバルビューモデルは High Performance Fortran (HPF)[11] の影響を受けた指示文ベースのプログラミングモデルである。逐次コードに XMP 指示文を追加することで分散メモリプログラムを記述する。 HPF ではユーザは指示文によってデータ分散の指定のみ行い,コンパイラが処理の並列化や通信を自動で行うのに対して,XMP はユーザがデータ分散・処理のマッピング・通信・同期を指示文で明示する必要があるため,HPF に比べて挙動が明確で性能チューニングがしやすいという特徴がある。

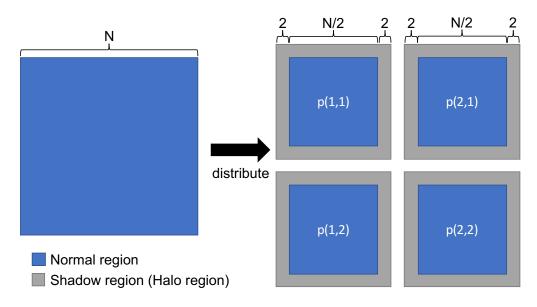

グローバルビューモデルのプログラミングを図 2.5 に示す. XMP における実行単位はノードであり、MPI におけるプロセスに対応するものである. はじめに、nodes 指示文によりノード集合を定義する. XMP ではインデックス空間を表す仮想的な配列であるテンプレートを用いて、データと処理のマッピングを行う. template 指示文はこのテンプレートを定義する. なおテンプレートを未定義サイズで指定しておき、後から template\_fix 指示文によりサイズを指定することも可能である. distribute 指示文はテンプレートをノード集合にどの方法で分散するかを指定する. 分散方法としては block、cyclic、gblock、もしくは\*(分散しない)がある. gblock 分散は "general block" 分散の略であり "gblock(blocksize-array)" と記述することで、各ノードのブロックサイズを blocksize-array で指定したブロックサイズにすることが可能である. align 指示文は分散されたテンプレートに沿って配列を

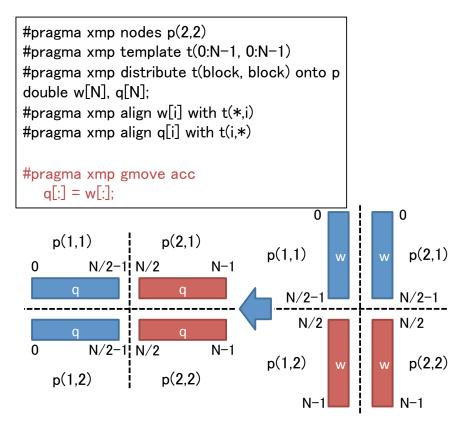

15 第 2 章 研究の背景

#pragma xmp shadow a[1:1] // [lower : upper]

#pragma xmp reflect (a)

図 2.6: shadow と reflect 指示文の例

分散する。また shadow 指示文はシャドウと呼ばれるいわゆる袖領域を分散配列に指定するもので、"(lower-width: upper-width)" という形式で下側・上側の袖幅を指定できる。100p 指示文は直後のループをテンプレートに沿って分散する指示文である。通常は割り当てられたループ範囲が自分のノードに割り当てられたテンプレートの範囲を超えることはないが、XMP 1.3 の仕様で追加された expand 節を用いると、ローカルのループ範囲を拡張することが可能である。図では最後のループに expand 節を指定したことで、p(1) ではループ範囲が 0-4 に、p(2) では 3-7 に拡大されている。次に XMP の通信指示文について解説する。最も特徴的なのはステンシル計算において袖交換を行う reflect 指示文である。図 2.6 は reflect 指示文の例である。配列 a[1] は 4 ノードに分散されており、幅が 1 要素のシャドウ領域を持っている。reflect 指示文により隣接ノードが持っている実際の領域の値でシャドウ領域を更新する。width 節を用いると更新する幅を指定でき、もし指定がなければシャドウ領域すべてが更新される。reduction 指示文は変数や配列の値をノード間で集計する指示文である。演算子には OpenMP と同様に +,\*, min, max 等を指定できる。gmove 指示文は変数や分散配列に対する様々な代入処理を行うことが可能な指示文である。代表的な 3 種類の通信を図 2.7 に示す。(a) は分散配列から分散配列への代入でこの例では send-recv の通信となる。(b) は分散配列からローカル配列への代入で,この例では broadcast の通信となる。(c) は分散配列から分散配列への転置で、all-to-all の通信となる。

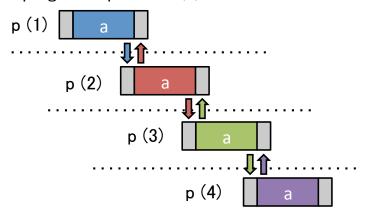

#### 2.6.2 ローカルビューモデル

ローカルビューモデルは coarray という他のノードからもアクセスが可能な配列を通信に用いるプログラミングモデルである。 coarray は Coarray Fortran [12] として提案され,Fortran 2008 から正式に導入された機能である。 XMP Fortran (XMP/F) は Fortran 2008 との互換性があり,XMP C (XMP/C) は C の文法を拡張することで coarray に対応している。データや処理の分散は MPI と同様にユーザが行う必要があるが,coarray では配列の次元のようにノードを扱えるため,通信を配列代入文で簡易に記述できる利点がある。

2.6 XcalableMP

図 2.7: gmove 指示文の例

```

coarray の宣言

data-type variable: codimensions

where codimensions is

[[int-expr]...][*]

coarray の参照

variable: [int-expr]...

```

図 2.8: XMP/C における coarray の文法

図 2.8 は XMP/C における coarray の文法である。coarray では実行単位をイメージと呼び、これは XMP グローバルビューモデルにおけるノードに相当する。coarray は通常の変数宣言の最後に codimensions を 追加することで宣言する。イメージ集合の形状は多次元で指定することが可能であり、データを多次元分散する際に役立つ。他のイメージの coarray にアクセスする場合には、通常の変数参照に加えて co-indices を指定する。もし co-indices が指定されなければ、通常の変数と同じ扱いになるため自分のイメージで

#pragma xmp post(nodes-ref, tag)

#pragma xmp wait [(nodes-ref [, tag])]

図 2.9: post/wait 指示文の構文

のローカルアクセスとなる。リモートの coarray に対しての代入は PUT 通信、参照は GET 通信となる。 Fortran では配列アクセスで範囲を指定可能であるが、C では要素ごとのアクセスしか対応していない。 XMP/C では言語拡張で配列アクセスにおける範囲記述に対応しており、"[lower[:length[:stride]]]"の形式で記述できる。coarray を用いた通信では、要素ごとのアクセスはオーバーヘッドが大きいため、配列の範囲を用いて記述することで効率良く通信することが可能である。

次に coarray における同期方法について説明する. XMP/F においては Fortran 2008 と同様に、sync memory, sync image, sync images, sync all が文として定義されており、XMP/C においては関数として xmp\_sync\_memory(), xmp\_sync\_image(), xmp\_sync\_images(), xmp\_sync\_all() が定義されている. sync memory はこれより前の coarray 操作がローカルで完了するまで待機する. sync image / sync images は 自身と指定した image 間での coarray 操作が完了するまで待機する. sync all はすべてのイメージ間での coarray 操作が完了するまで待機する.

XMP/C では追加機能として、同期のためのシグナルを送受信する post と wait 指示文を提供している。図 2.9 は post/wait 指示文の構文である。 nodes-ref はグローバルビューモデルにおける XMP ノード集合の参照であるが、実質ローカルビューモデルにおけるイメージ番号と同じである。 post 指示文では tag を指定して同じノードからの複数のシグナルを区別することができ、wait 指示文では tag を指定した場合は対応するシグナルを待つが指定がなければ任意のタグのシグナルを待つ。 xmp\_sync\_memory() と post/wait 指示文を組み合わせることにより xmp\_sync\_image() と同等,もしくはより柔軟な同期を記述することが可能である。

図 2.10 は XMP ローカルビューモデルによるコード例である. a[4]:[\*] は codimension が指定されているため coarray である。各イメージはそれぞれ coarray a[] を重複して保持する。イメージ 1 は配列の範囲表記を用いて自イメージの a[2-3] をイメージ 2 の a[0-1] に代入 (put) する。xmp\_sync\_all() の呼び出しにより全イメージでの coarray 通信の完了を待機する。その後,イメージ 2 では a[0-1] に書き込まれた値を読むことが可能になる。

2.6 XcalableMP 18

図 2.10: XMP ローカルビューモデルによるプログラム例

## 第3章

# 演算加速機構を持つ並列クラスタ向け PGAS 言語 XcalableACC の提案

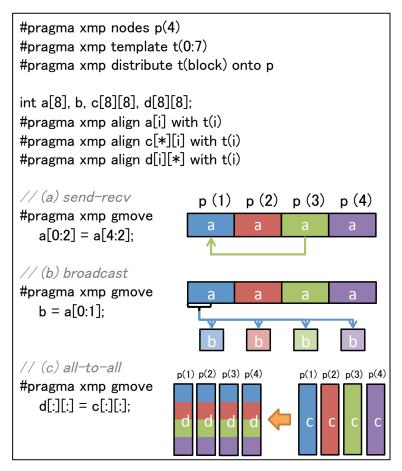

本章では演算加速機構を持つ並列システム向けの PGAS 言語 Xcalable ACC のプログラミングモデルや 記述方法について述べる。 XACC は筑波大学と理研が共同で提案している PGAS 言語で、既存の PGAS 言語 XMP とアクセラレータプログラミングモデル OpenACC を統合した言語である。現在、仕様の version 1.0 を公開している [9].

### 3.1 概要

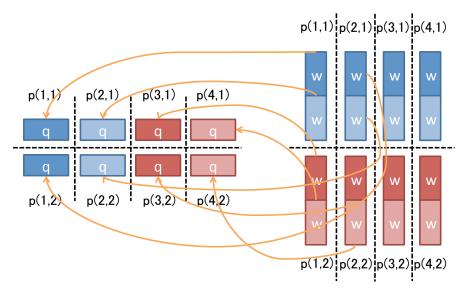

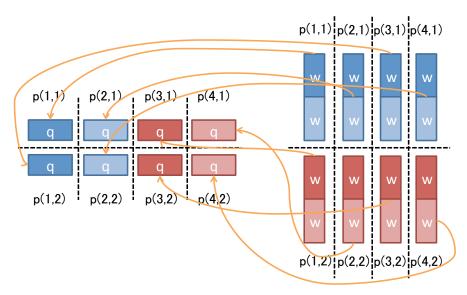

XACC は XMP と OpenACC を統合したプログラミングモデルであり、分散メモリ並列化を XMP で記述し、アクセラレータへのオフロードを OpenACC で記述する。XACC の特徴の一つはアクセラレータメモリ上のデータに対するノード間通信である。図 3.1 はアクセラレータ上のデータをノード間で通信する際の記述イメージを XMP と OpenACC の組み合わせと XACC とで比較したものである。単に XMPと OpenACC を組み合わせた際には、アクセラレータ間の通信を行う指示文が存在しないため図 3.1aのように OpenACC によるホストとアクセラレータ間の通信と XMP によるホスト間の通信が必要である。XACC では既存の XMP の通信指示文や coarray を拡張することで、図 3.1b のようにアクセラレータ間の通信を直に記述可能である。この機能により、(1) プログラマの意図することを簡潔かつ直接的に記述できる。(2) コンパイラ・ランタイムが実行環境ごとに適切な通信を行える、という利点がある。(2) の例として、NVIDIA GPU において GDR が利用可能な環境であればそれを利用して高速に通信をすることができる。XMP グローバルビューモデルをベースにした XACC グローバルビューモデルが中尾らにより提案されている [13]。本研究では XMP ローカルビューモデルをベースとした XACC ローカルビューモデルを新たに提案する。

### 3.2 グローバルビューモデル

XACC グローバルビューモデルでは基本的に XMP グローバルビューモデルにおける指示文ベースの 分散や通信の記述と OpenACC 指示文の組み合わせにより記述する. XMP 指示文により分散された配

図 3.1: デバイス間通信の記述方法

列およびループに対して OpenACC 指示文を指定する方法やアクセラレータ間の通信の記述方法とその動作について説明する. 分散配列をアクセラレータ上に確保およびコピーするには通常の変数と同様に OpenACC data, enter data, declare 指示文を用いる. 指定された分散配列の各ノードが保持する部分のみがそのノードが保持するアクセラレータに確保やコピーされる. また update 指示文を用いてホスト側とアクセラレータ側で分散配列の更新が可能である.

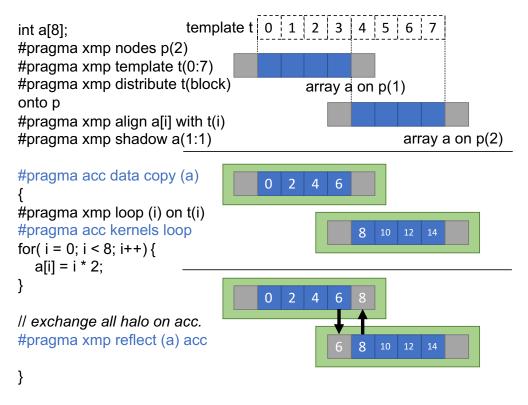

次に、XMP loop 指示文で分散されたループに対しては OpenACC parallel loop, kernels loop, loop 指示文が指定できる。OpenACC parallel loop, kernels loop 指示文では各ノードが担当するループ範囲をそのノードに接続されているアクセラレータで実行する。ただし OpenACC loop 指示文の場合は、その XMP loop 指示文のループの分散やループ範囲がカーネル領域の内で不変でなければならない、という制約がある。分散ループに loop 指示文のみ指定する場合は、すなわちそのループが parallel か kernels 指示文でアクセラレータでの実行対象として指定されているということである。実装の観点から、アクセラレータカーネル内でループの分散を行うのは非効率であるため、カーネルに入る前に分散の処理をできるよう制約を設けている。

アクセラレータ上のデータに対する通信は、XMP 通信指示文の最後に acc 節を加えることで指定する. この場合、アクセラレータ上のデータのみ対象となるためホスト上のデータは変化しない. また、XMP gmove 指示文においては "acc[(variable)]" として対象の変数名が指定できるようになっており、その場合には gmove の左辺もしくは右辺の指定された変数のみでアクセラレータ側のデータが用いられる.

図 3.2 は XACC グローバルビューモデルのプログラム例である。左側のコードは XMP コードをベースにした際に XACC で追加・変更した部分を青色で強調してある。この例ではまず,XMP 指示文により 2 ノードに配列 a[] をブロック分散してかつ上下端に袖領域を追加する。次に,分散配列 a[] をアクセラレータで処理するために OpenACC data 指示文によりアクセラレータメモリ上に確保・コピーを行う。この際,各ノードがローカルに持っている部分のみがアクセラレータに配置される。XMP で分散されたループにさらに OpenACC kernels loop 指示文を追加することで,そのループをアクセラレータで処理するよう指定する。XMP reflect 指示文の最後に acc 節を追加することにより,アクセラレータ上の分散配列 a[] に対して袖通信が実行される。この際,ホストメモリ上にある分散配列 a[] は変更されない。

図 3.2: XACC グローバルビューモデルのコード例

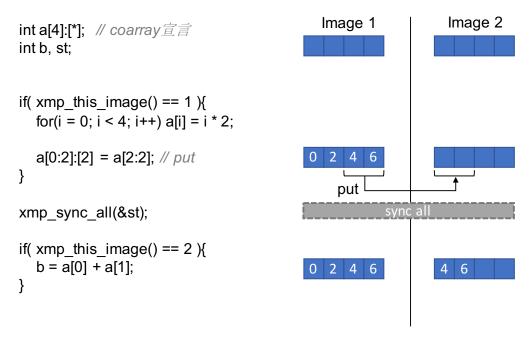

### 3.3 ローカルビューモデル

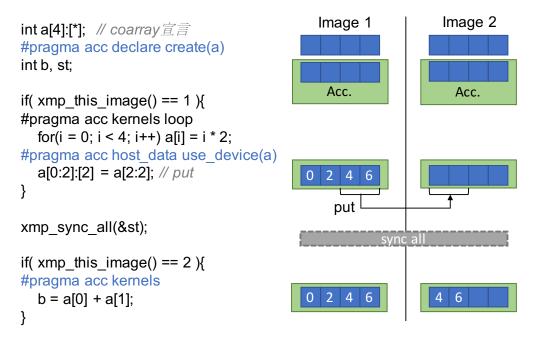

XMP ローカルビューモデルの coarray は Fortran2008 からの正式な仕様であるが、現在最新の OpenACC 2.6 においては coarray に対して OpenACC がどのように動作するかは定義されていない。そこで XACC では coarray をアクセラレー夕間の通信でも利用できるように、アクセラレータ上に coarray を宣言しそれを参照するための記述方法を提案する。 coarray をアクセラレータ上に確保するには OpenACC declare 指示文を用いる。 declare 指示文は指定した変数をそのスコープにおいてアクセラレータ上にも確保する指示文である。 coarray に対する declare 指示文の利用時にはコピーを伴わない create 節のみ指定できる。 通常のホストメモリ上の coarray 宣言の後に declare create でその coarray を指定すると、アクセラレータメモリ上にも同じ coarray が宣言される。 なお、 OpenACC にはアクセラレータ上にデータを確保する指示文として他に data と enter data が存在するが、いずれもアクセラレータにおけるデータの生存期間が動的であったり部分配列が指定可能であったりして自由度が高く、 coarray の宣言には適さないので許可していない。

アクセラレータ上にも coarray を宣言した場合でも特に指定がない場合はホストメモリ上の coarray に対するアクセスになる。アクセラレータ上の coarray をアクセスするには OpenACC host\_data 指示文を用いる。この指示文の use\_device 節にはアクセラレータ上にデータが確保されている変数を指定でき、その変数は直後のコード領域においてホストコードにおける変数アドレスがアクセラレータメモリ

3.4 関連研究 22

図 3.3: XACC ローカルビューモデルのコード例

側のアドレスに置きかわる.この指示文は主にアクセラレータ向けに書かれた外部ルーチンにアクセラレータメモリ側のアドレスを渡すために使用される.use\_device に,coarray を指定した場合にはそのcoarray のアクセスはアクセラレータ側に対して行われる.なお,リモートの coarray のみ use\_device で指定し,ローカルの coarray もしくは通常の変数には何も指定しなかった場合は,リモートのアクセラレータメモリとローカルのホストメモリでの通信が行われる.アクセラレータ上の coarray を用いた通信の同期はホスト側の coarray と同様に,sync all や sync image などで行う.アクセラレータ上の coarray は通常の変数と同じように parallel, kernels 領域中でアクセスしたり,update 指示文でホストとアクセラレータ間でコピーしたりすることが可能である.

XACC ローカルビューモデルのコード例を図 3.3 に示す。ホスト上に通常の coarray a[] を宣言した後に、OpenACC declare 指示文で a[] をアクセラレータメモリ上にも宣言する。まずイメージ 1 において、coarray a[] に値を代入し、その後 use\_device で coarray a を指定することでアクセラレータ上のa[2:2] の値をイメージ 2 の a[0:2] にリモートライトする。xmp\_sync\_all() で同期を行った後、イメージ 2 は書き込まれた a[0:2] のデータを用いて処理を行う。

### 3.4 関連研究

演算加速機構を持つ並列システム向けに XMP を拡張した XcalableMP acceleration device extension (XMP-dev) が李らにより提案されており、 XMP-dev から CUDA や OpenCL に変換するコンパイラが実装されている [14, 15, 16]. XMP にアクセラレータ上のデータ宣言、ホスト・アクセラレータ間のデータ転送、アクセラレータでの並列ループ実行、およびアクセラレータ間の通信を指定する指示文を追加することにより、 演算加速機構を持つ並列システムで利用できる記述能力と性能を有することを明らか

にした.特にノード間のアクセラレータメモリ上のデータ通信が性能向上に大きく貢献することを示した.XMP-dev はオフロードに独自の指示文を用いていたが,XACC は OpenACC が標準規格として提案されたことを受けて,XMP-dev を発展させ,オフロードを OpenACC に沿った指示文にすることにより OpenACC ユーザが分かりやすくなるようにした.また特にデータの管理に関して,XMP-dev ではアクセラレータ上にデータが有るか無いかに関わらずデータを確保することしかできなかったが,XACC ではオフロードについて OpenACC を取り入れることにより,すでにある場合には確保しないなど,十分な操作ができるようになった.さらに XMP-dev ではグローバルビューの通信にのみ対応していたが,XACC ではローカルビューモデルにも対応することでより柔軟な通信の記述を可能としている.性能の点では,XMP-dev は CUDA もしくは OpenCL に変換し,XACC は OpenACC に変換するという違いがあるが,OpenACC はさらに CUDA や OpenCL に変換(コンパイル)することができるので,同等な記述に関しては同等な性能が得られるはずである.ただし,OpenACC は CUDA 等よりも高レベルな記述であるため新規のプラットフォームに対応しやすいが,XMP-dev では開発当時のアクセラレータのアーキテクチャに合わせた CUDA コードや OpenCL コードになっており,現在主流のアーキテクチャには適さない可能性がある.

3.4 関連研究 24

# 第4章

# OpenACC コンパイラの設計・実装

本章では、XACC のベースとなるアクセラレータ向け指示文ベースプログラミングモデル OpenACC のコンパイラを設計・実装し、ベンチマークを用いて評価を行う。OpenACC は初の標準仕様であったが、当初はオープンソースのコンパイラがなく、商用コンパイラにおいても NVIDIA GPU のような一般的なアクセラレータのみの対応で、最適化が不十分であった。そこで、OpenACC から source-to-source 変換を行うコンパイラを設計し、NVIDIA GPU と PEZY-SC に向けて実装および最適化を行う。そしてベンチマークプログラムを用いて、NVIDIA GPU 向けにおいては既存の商用コンパイラとの性能比較を、PEZY-SC 向けにおいては PZCL コードとの性能・生産性の比較を行う。

# 4.1 NVIDIA GPU 向け OpenACC コンパイラ

NVIDIA GPU を対象に実装した Omni OpenACC compiler についてその設計と実装について述べる.

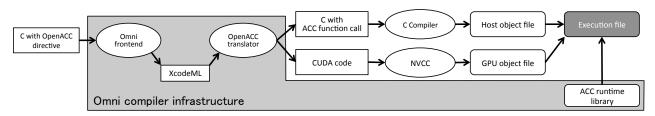

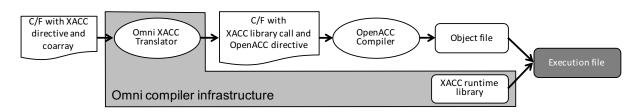

#### 4.1.1 設計

OpenACC は C・C++・Fortran に対応しているが、このコンパイラでは C 言語のみを対象とする. NVIDIA GPU のプログラミングには言語・コンパイラともに成熟している CUDA を用いる。本実装では CUDA のカーネルコードにおいてループ並列化以外はできる限り元のソースコードを維持することにより、NVIDIA CUDA compiler (NVCC) による最適化が十分に行われ、より高速な実行ファイルが生成されるように変換を行う。これを実現するためにコードの解析や元のコードを維持した変換が可能である Omni compiler infrastructure[17] を実装に用いる。これは C と Fortran95 をソースからソースへ変換するコンパイラ用のプログラムセットである。またホストコードにおいては多くの処理を実行時ライブラリの呼び出しに変換することでプログラムの可搬性を向上させる。コンパイルの流れを図 4.1 に示す。OpenACC 指示文の書かれた C 言語のコードをコンパイルする際には、まず Omni frontend で XML 形式の中間コードである XcodeML に変換する。それを OpenACC translator で読み込んでコード変換し、ホストコードと CUDA コードを出力する。その際 GPU で実行する部分はカーネル関数として分離しループの並列化を行うが、ループの内部は変更しない。また Kepler アーキテクチャ向けの最適化として、読み込みのみの配列に対して Read-only data cache が使われるよう指定したり、リダクションにおいて shuffle

図 4.1: Omni OpenACC compiler のコンパイルの流れ

命令や atomic 命令を用いたりする. 一方でホストコードでは指示文を実行時ライブラリ呼び出しに置き換える. ホストコードは一般的な C コンパイラでコンパイルし, CUDA コードは NVCC でコンパイルする. 最後にコンパイルされた 2 つのオブジェクトファイルを OpenACC runtime library とリンクして実行可能バイナリを生成する.

#### 4.1.2 data 構文の実装

データ指示文が指定された領域では指示節に基づいて、データ領域の最初にデバイスメモリの確保とホストメモリからデバイスメモリへの転送、データ領域の最後にデバイスメモリからホストメモリへの転送 とデバイスメモリの解放を行う。これらの操作はすべてライブラリ関数の呼び出しに変換する。

ソースコード 4.1 に data 構文例を、ソースコード 4.2 にその変換例を示す。この data 構文では領域内で配列 a[] と変数 b のためのデバイスメモリを確保する。また copy 節内で指定されている配列 a[] は領域の最初と最後で転送し、copyout 節内で指定されている変数 b は領域の最後でのみ転送する。デバイスメモリの確保にはライブラリ関数\_ACC\_init\_data() を用いる。この際、配列の場合には各次元の lower b length を指定する。DEV\_ADDR\_name はホスト上の b name に対応するデバイスメモリのポインタである。DESC\_name は b name のホストアドレス、デバイスアドレス、配列形状、要素サイズ等が格納された構造体へのポインタである。ホストメモリとデバイスメモリ間の転送はライブラリ関数\_ACC\_copy\_data()で行う。ライブラリ関数\_ACC\_finalize\_data()により最後にデバイスメモリの解放を行う。

#### ソースコード 4.1: data 構文の例

```

1 int a[100], b;

2 #pragma acc data copy(a) copyout(b)

3 {

4  /* some codes using a and b */

5 }

```

#### ソースコード 4.2: data 構文の変換例

```

1 int a[100], b;

2 {

3    void *DESC_a,*DEV_ADDR_a,*DESC_b,*DEV_ADDR_b;

4    unsigned long long _lower[] = {0};

5    unsigned long long _length[] = {100};

6    _ACC_init_data(&(DESC_a),&(DEV_ADDR_a),a,sizeof(int),1,_lower,length);

```

図 4.2: OpenACC の並列性の CUDA へのマッピング

```

8

_ACC_init_data(&(DESC_b),&(DEV_ADDR_b),&(b),sizeof(int),0,NULL, NULL);

9

_ACC_copy_data(DESC_a,_ACC_HOST_TO_DEVICE,_ACC_ASYNC_SYNC);

10

11

/* some codes using a and b */

12

13

_ACC_copy_data(DESC_a,_ACC_DEVICE_TO_HOST,_ACC_ASYNC_SYNC);

14

_ACC_copy_data(DESC_b,_ACC_DEVICE_TO_HOST,_ACC_ASYNC_SYNC);

15

_ACC_finalize_data(DESC_a);

16

_ACC_finalize_data(DESC_b);

17 }

```

### 4.1.3 parallel 構文の実装

parallel 指示文で指定されたコード領域を GPU で実行するには,GPU 上での処理を記述したカーネル関数を作成し,それをホストから起動する必要がある.CUDA ではカーネルは 3 次元のグリッドとスレッドブロックで実行され,各スレッドはそのインデックスを用いて並列に処理を行う.本実装における OpenACC の並列性の CUDA へのマッピングを図 4.2 に示す.gang,worker,vector をそれぞれ CUDA のグリッドの X 次元,スレッドブロックの Y 次元,スレッドブロックの X 次元に対応させ,その他の次元は 1 として利用しない.それぞれ CUDA の組み込み変数 blockIdx.x,threadIdx.y,threadIdx.x により識別できる.なお現在の実装では worker 数,すなわちスレッドブロックの Y 次元は必ず 1 としている.カーネル関数を起動する際の vector 長はデフォルトで 256 とし,gang 数は gang で並列化するループ長から決定する.ループを gang のみで並列化する場合はそのループ長に,gang と vector で並列化する場合はループ長を vector 長で割った数にする.加えて,カーネルが起動できるグリッドの X 次元のサイズは Fermi アーキテクチャでは 65535,Kepler アーキテクチャでは  $2^{31}$  — 1 という制限があるため gang 数の調整が必要となる.Kepler アーキテクチャにおいてもスレッドブロック数が増えるとオーバーヘッドが増加するため,Fermi アーキテクチャの制限に合わせて gang 数が 65535 個以下となるように  $numGangs' = \lceil numGangs/\lceil numGangs/65535\rceil$  とする.gang 数の整数倍がおよそループ長になる ため gang 間の負荷が均等になりやすい.

カーネル関数を起動する際には参照するデータのポインタ,もしくは値を直接渡す必要がある。コンパイラはカーネル領域内で使用されるデータを調べ、それらに対する GPU メモリのポインタをカーネル

関数の引数として渡す。ただし firstprivate 節で指定された変数に対しては値渡しにすることでその変数の初期化を実現している。さらに Kepler アーキテクチャ用にコンパイルする際にはリードのみのデータに対して Read-Only Data Cache を利用するようコードを生成する。カーネル関数の仮引数でのポインタの宣言に "const \_\_restrict\_\_" 修飾子を付けることで Read-Only Data Cache を介してロードするよう CUDA コンパイラにヒントを与える。GPU メモリの確保等については 4.1.2 節で述べる。

ソースコード 4.3 に parallel 構文例を,ソースコード 4.4 にその変換例を示す.関数\_ACC\_GPU\_FUNCO\_DEVICE() がカーネル関数である.gang 数が 4, vector 長が 64 なので 4 スレッドブロック,1 スレッドブロックあたり 64 スレッドとする.関数\_ACC\_GPU\_ADJUST\_GRID() でブロック数を 65535 以下になるように調整したのち,カーネル関数に変数 a の GPU メモリのポインタを渡して起動する.その後カーネル関数の終了を\_ACC\_wait() で待機する.

#### ソースコード 4.3: parallel 構文の例

```

1 #pragma acc parallel present(a) num_gangs(4) vector_length(64)

2 {

3  /* codes in parallel region */

4 }

```

#### ソースコード 4.4: parallel 構文の変換例

```

1 __global__ static

2 void ACC GPU FUNC 0 DEVICE (void *a...)

3 {

4

/* codes in parallel region */

5 }

6 extern "C"

7 void _ACC_GPU_FUNC_0 (void *DEV_ADDR_a, ...)

8 {

9

int block_x=(4), block_y=(1), block_z=(1);

10

int thread_x=(128), thread_y=(1), thread_z=(1);

11

_ACC_GPU_ADJUST_GRID(&block_x,&block_y,&block_z,65535);

12

dim3 DIM3_block(block_x, block_y, block_z);

13

dim3 DIM3_thread(thread_x, thread_y, thread_z);

14

15

_ACC_GPU_FUNC_0_DEVICE<<<DIM3_block,DIM3_thread,0,

16

_ACC_gpu_get_stream(_ACC_ASYNC_SYNC)>>>(DEV_ADDR_a, ...);

17

_ACC_wait(_ACC_ASYNC_SYNC);

18 }

```

### 4.1.4 loop 構文の実装

100p 指示文に続く for ループは GPU 上で並列に実行するように変換する. 並列化に用いる並列性 (gang, vector) が指定されていればそれを用い, 指定がない場合はコンパイラが自動で使用する並列性を決定する. ループ分割方法は gang の場合には空間局所性を高めるために block 分割を用い, vector の場合は隣接するスレッドが配列の隣接する要素にアクセスするコアレスドアクセスになりやすくするために

図 4.3: shuffle 命令を用いたバタフライリダクション (この図は8スレッド間で変数vの和を求める場合)

cyclic 分割を用いる. さらに loop 指示文に reduction 節が付記されている場合は指定された変数用にプライベート変数を用意し、ループの終わりにリダクションして元の変数に書き込むように変換する.

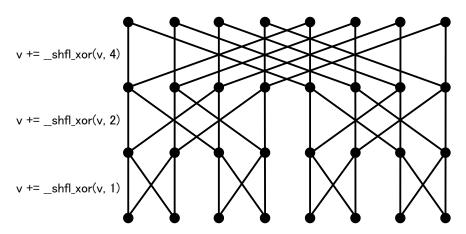

#### vector reduction

通常は Shared メモリのみを用いてスレッド間で値を共有し、並列にリダクションを行う。一方、Kepler アーキテクチャ向けにコンパイルする際には shuffle 命令も利用する。shuffle 命令により同一ワープ内のスレッド間で値の受け渡しが可能であり、そのうち\_shfl\_xor() を使うことで図 4.3 に示すようなワープ内のリダクションが実現できる [18]。なお Kepler アーキテクチャでは \_shfl\_xor() は int と float 型しか用意されてないため、double 型では上位 32bit と下位 32bit に分割して交換する関数を用意した。スレッド間でのリダクションの流れは、まず shuffle 命令を用いて各ワープ内でリダクションし、部分結果をShared メモリに書き込む。その後 1 ワープが部分結果を shuffle 命令でリダクションして全体の結果を求める。Kepler アーキテクチャでは 1 スレッドブロック当たりのワープ数は最大 32 個であるため部分結果のリダクションには 1 ワープ 32 スレッドで十分である。通常の Shared メモリのみを用いた方法に比べ、Shared メモリの読み書きとそれに伴うスレッド間同期が削減できるため、より高速なリダクションが可能となる

#### gang reduction

CUDA ではスレッドブロック間で同期を取ることができないため、通常はブロックごとの部分結果をバッファに格納しておき、最後に別のカーネルでその結果をリダクションする。しかしながらバッファの確保が必要、リダクション用のカーネル起動のコストがかかる、最後のリダクション用カーネルは1ブロックで実行するため部分結果の数が多い場合は性能が落ちるなど、多くの問題を抱えている。Kepler アーキテクチャの GPU では同じグローバルメモリアドレスに対する atomic 演算が1クロック当たり1演算実行可能となり、Fermi アーキテクチャと比べて9倍も高速化されている [1]。そこで Kepler アーキテクチャ用にコンパイルする際には atomic 演算が提供されている int 型と float 型の一部のリダクション演算 (+, min, max 等) は、各ブロックの部分結果を atomic 演算でリダクション変数に直接リダクションするように実装した。

また atomic 命令を利用できないリダクションにおいてバッファ確保・解放のオーバーへッドを削減するために、メモリプールを用いている。このメモリプールは OpenACC の async 節などで指定するキュー番号ごとに確保されている。カーネル起動の際にはそのカーネルを実行するキューに対応付けられたメモリプールの先頭から順にメモリを利用してゆき、カーネル実行後は何もする必要はない。キュー番号ごとに別のメモリプールを用いることで、同一のメモリプールを利用するカーネルは必ず 1 つだけとなるため、複雑な管理が不要となっている。またこのメモリプールはリダクション変数自体のデバイスメモリの確保にも利用できる。このメモリプールの大きさはデフォルトで 1 MB としている。スレッドブロック数は 65535 以下になるよう調整しているため double 型のリダクション変数 1 つあたり最大で、8 Byte × (1+65535)=512 KB 使用する。したがって double 型であれば最大 2 つのリダクション変数とそのバッファをメモリプールから確保できる。

ソースコード 4.5 に 100p 構文例を、ソースコード 4.6 にその変換例を示す。 \_ACC\_calc\_niter() でループ長を求め、\_ACC\_init\_thread\_iter() で、そのスレッドが担当するインデックスの範囲を求める。その後ループ内では\_ACC\_calc\_idx() により実際のループ変数の値を求め、ループ本体を実行する。またリダクション部分に関しては、始めに\_ACC\_init\_reduction\_var() によりスレッドローカル変数を初期化し、ループ実行後に\_ACC\_reduction\_thread() によりスレッド間でローカル変数の値をリダクションする。

#### ソースコード 4.5: loop 構文の例

```

1 /* inside parallel region */

2 #pragma acc loop vector reduction(+:sum)

3 for(i = 0; i < N; i++) {

4   a[i]++;

5   sum += a[i];

6 }</pre>

```

#### ソースコード 4.6: loop 構文の変換例

```

1 /* inside qpu kernel function */

2 int _niter_i, _idx, _init, _cond, _step, _red_sum;

3 _ACC_init_reduction_var(&_red_sum, 0);

4 _ACC_calc_niter(&_niter_i, 0, N, 1);

5 _ACC_init_thread_iter(&_init,&_cond,&_step,_niter_i);

6 for(_idx = _init; _idx < _cond; _idx += _step) {</pre>

7

int i;

8

_ACC_calc_idx(_idx, &i, 0, N, 1);

9

a[i]++:

10

_red_sum += a[i];

11 }

12 _ACC_reduction_thread(sum,_red_sum, 0);

```

#### 4.1.5 評価

NVIDIA GPU 向け OpenACC コンパイラの基礎評価としてリダクションのマイクロベンチマーク, および NAS Parallel Benchmarks (NPB) のうち 5 つのカーネルベンチマーク CG, EP, IS, FT, MG で評

|          | K20-Opteron (Cray XK6)             | K20-Xeon                                |

|----------|------------------------------------|-----------------------------------------|

| CPU      | AMD Opteron 6272 2.1 GHz (16 Core) | Intel Xeon E5-2609 2.4 GHz (4 Core)     |

| Memory   | DDR3-1600 32 GB                    | DDR3-1066 32 GB                         |

| GPU      | Tesla K20 (GDDR5 5 GB, ECC on)     | Tesla K20 (GDDR5 5 GB, ECC on)          |

| OS       | CNL (Compute Node Linux)           | CentOS 6.4                              |

| Compiler | CCE 8.3.0, CUDA 5.5                | GCC 4.4.7, PGI compiler 14.10, CUDA 5.5 |

表 4.1: NVIDIA GPU 向け OpenACC コンパイラの評価環境

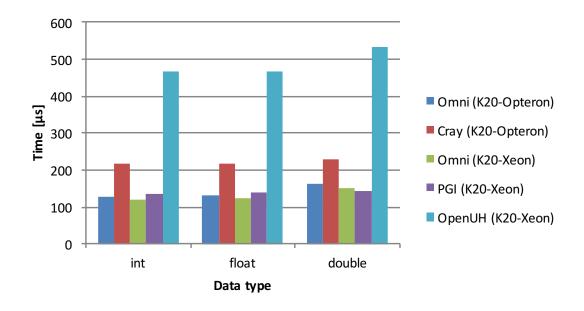

価を行った。NPB の C 言語 OpenACC 版はソウル大学校が公開している SNU NPB Suite[19] に含まれる NPB3.3-SER をベースに実装し、さらに高速化のためにコードの一部を変更した。実装した Omni OpenACC compiler と Cray compiler 8.3.0、PGI compiler 14.10、OpenUH-OpenACC[20](2014 年 5 月 5 日時点)の性能を比較した。なお OpenUH-OpenACC は parallel 指示文の async 節など実装されていない機能があり、同一条件で比較できなかったためリダクションの性能のみを載せる。また GPU カーネルのデフォルトのスレッドブロック数がコンパイラごとに異なるため、vector\_length 節で指定した。

評価環境を表 4.1 に示す。"K20-Opteron" は Cray XK6 であり Cray compiler が利用可能である。また "K20-Xeon" は通常の GPU クラスタで PGI compiler が利用可能である。本実装のコンパイルオプションには "-acc -O3" を指定し、nvcc に渡すオプションは "-O3 -arch=sm\_35" とした。また K20-Opteron で はホストコードのコンパイルに Cray compiler を、K20-Xeon では gcc 4.4.7 を使用した。Cray compiler を用いた OpenACC のコンパイルのオプションには "-O3 -h acc\_model=auto\_async\_none" を指定した。auto\_async\_none を指定することで非同期カーネル実行が自動で行われるのを抑止し、その際のオーバーヘッドを削減した。PGI compiler のコンパイルオプションには "-O3 -acc -ta=tesla:cc3+,cuda5.5,nordc -Msafeptr" を指定した。-Msafeptr によりポインタのエイリアスがないことをコンパイラに伝えている。OpenUH-OpenACC のコンパイラオプションには "-fopenacc" を用い、nvcc に渡すオプションは "-arch=sm\_35" とした。最適化オプションは使用するとコンパイラが異常終了するので指定できなかった。また本実装と異なり CUDA ソースファイルにはデバイスコードしか含まれないため nvcc のオプションに "-O3" は付けなくても問題は無い。

#### リダクションベンチマーク

このリダクションのベンチマークでは  $2^{20}$  要素の int, float, double 型配列の値の加算を行う時間を計測する. 配列要素のリダクションを行う 1 重ループに parallel loop 指示文を記述し, さらに各コンパイラでスレッド数などを同じにするため num\_gangs (4096) vector\_length (256) を指定した. 配列はあらかじめデバイスに確保し初期化しておき,リダクション変数の確保・解放とメモリコピーを含んだ処理時間を計測した。図 4.4 に  $2^{20}$  要素の配列のリダクションの実行時間を示す。K20-Opteron において,Cray compiler と比較して 1.42-1.68 倍の性能が得られた。Cray compiler における性能低下の原因として,parallel 領域をリダクションも含めて 1 カーネルで実行している点があげられる。Cray

図 4.4: 2<sup>20</sup> 要素のリダクションの実行時間

compiler におけるリダクションの方法は、(1) 各スレッドブロックは部分結果を一時配列の自分のスレッ ドブロックインデックスに書き込み、メモリフェンスにより書き込みの完了を保証する。(2)事前に0ク リアされたカウンタを atomic 演算でインクリメントし、インクリメント後の値が全スレッドブロック数 よりも小さければ最後のスレッドブロックではないので何もせず,等しければ最後のスレッドブロックな ので一時配列の部分結果をまとめて全体の結果を書き込む、となっていた. 書き込みを完了してからカウ ンタを増やすためにフェンスによる待機や atomic 演算が必要になるため,スレッドブロック数に比例し て実行時間が増加する。なお、リダクション変数やバッファの確保のためのメモリ確保は最初のカーネ ル実行でのみ行われていた。一方、Omni compiler においては部分結果のリダクションの部分は別のカー ネルとして実行する.カーネル起動オーバーヘッドがあるが,リダクション以外のメインのカーネルの 実行時間が長ければそのオーバーヘッドは隠蔽可能であり、定数時間であるためこちらのほうが実行時 間が短くなりやすい. K20-Xeon において、PGI compiler と比較し int, float 型では 1.14 倍, double 型で は 0.94 倍の性能が得られた。PGI compiler では Cray compiler と同じく一時結果を保持するためのメモ リはキャッシュをしており、毎回確保はされていなかった。Shared メモリを用いた一般的な処理を行っ ており,shuffle 命令や atomic 演算は使用していなかったため,本実装の方がより高い性能を得られた. なお 2018 年 1 月時点で最新の PGI 17.10 においても同様に shuffle や atomic は利用されていなかった. OpenUH-OpenACC は PGI compiler と同じく Shared メモリを用いたリダクションを行っていたが、カー ネル実行前後にバッファの確保・解放を行っていたため、時間が非常に増加している。

次に実装で行った最適化の効果を確認するために、K20-Xeon 上で最適化を順に適用した際の性能を図 4.5 に示す。"cache" は Read-Only Data Cache の利用,"mempool" はメモリプールの利用,"shuffle" は shuffle 命令の利用,"atomic" は atomic 演算の利用による最適化を表す。リダクションでは Read-Only Data Cache を使用すると逆に性能が低下した。リダクションでは同じデータは 1 度しか読まれずかつコ

図 4.5: 最適化による 2<sup>20</sup> 要素のリダクション時間の変化

アレスアクセスになるため、キャッシュする利点がなく逆にキャッシュするオーバーヘッドが増加したからである。次いでメモリプールの利用によりリダクション変数とバッファの確保時間が大幅に減少した。さらに shuffle 命令の利用ではすべての型で性能向上が確認できた。 atomic 演算は int と float 型でのみ利用するようにしており、それぞれ性能が向上した。

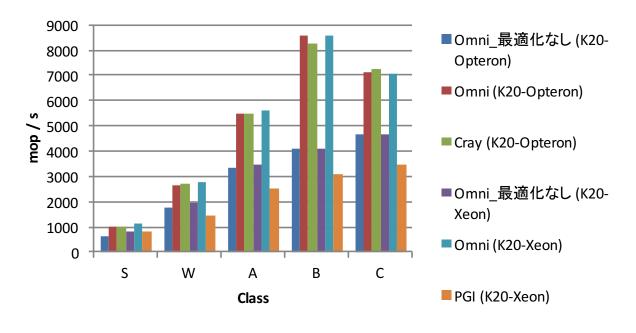

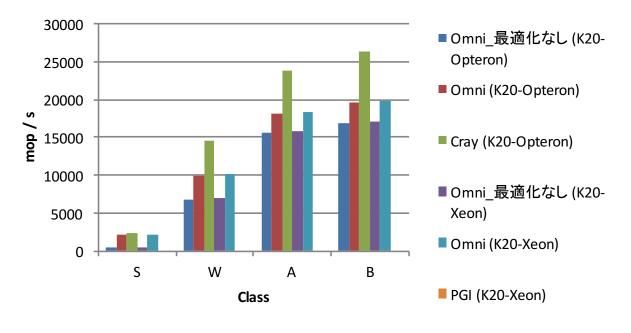

#### CG

CG ベンチマークの性能を図 4.6 に示す。まず本実装での Kepler アーキテクチャ向け最適化の有無により 1.38-2.11 倍の性能向上が確認できた。最適化ありの本実装の性能は Cray compiler と比較して 0.97-1.04 倍でほぼ同等であった。クラス B にて Cray compiler より高い性能が出た理由は Cray compiler ではスレッドブロックで並列化するループ長が 65535 を超えたときスレッドブロック数を 65535 個に設定していたのに対して、本実装では 65535 以下の数になるようにループ長を割った数にしており、それによりブロック数が減少しスレッドブロックを実行するオーバーヘッドが減少したからである。

K20-Xeon においては PGI compiler と比較して 1.34-2.80 倍の性能となった。 CG ベンチマークで最も時間のかかる疎行列ベクトル積のカーネルについて PGI compiler に "keep" オプションを付けて CUDA コードを出力したところ,const \_restrict\_修飾子や\_ldg() によるロードはなく,Read-Only Data Cache が使用されていないことが分かった。また使用レジスタ数も使用レジスタ数を調べたところ本実装では 24 個のところ PGI compiler では 35 個と多く,1SMX で実行できるブロック数が少ないため SMX の使用率が低下していた。加えて gang で並列化するループ長が 65535 以上のとき,PGI compiler でも Cray compiler と同様にスレッドブロック数を 65535 個に設定していた。加えて Kepler r-1中向け最適化なしの状態でも PGI compiler より高い性能が得られていることから,本実装の方が NVCC による最適化の効果が大きいと言える。

図 4.6: CG の性能

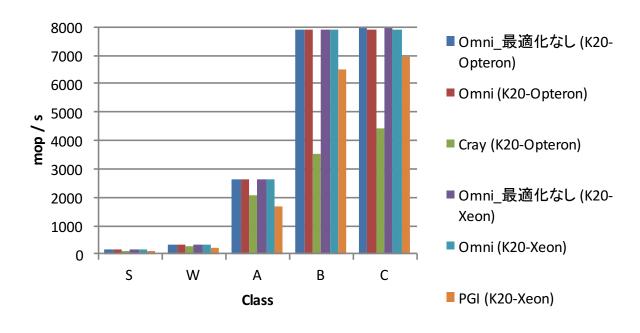

#### ΕP

EP ベンチマークの性能を図 4.7 に示す。本実装は Cray compiler と比較して 1.26–2.23 倍の性能が得られ、PGI compiler と比較すると 1.14–1.54 倍の性能が得られた。本実装ではすでにクラス B で性能が頭打ちになっているが、Cray compiler と PGI compiler ではクラス C まで性能が向上している。

Cray compiler での性能低下の原因を調査したところ,プロファイラの情報から Cray compiler でコンパイルしたバイナリでは倍精度演算数が 1.78 倍になっており,アセンブリをみると最内ループにおいて計算結果をレジスタに保持せず,同じ計算を 2 度実行している部分が多くあった.この差が起きた理由としては,本実装でコンパイルに用いる NVCC は内部ではコードを最適化した後,PTX と呼ばれる疑似アセンブリ言語に変換しそれを PTXAS (PTX optimizing assembler) で最終的に機械語に変換するのに対して,Cray compiler はコンパイラで最適化を行い直接 PTX コードを出力し,それを PTXAS で機械語に変換するため,PTX を出力する前までの最適化に違いがあるからである.この場合は CUDA コンパイラの方がよい最適化を行ったと言える.

また PGI compiler の場合は,実行された倍精度演算の命令数に大差はなかったが,プロファイラで調べると instruction per clock (IPC) が低下しており,クラス S では本実装の 0.69 倍,クラス B では 0.87 倍となっていた.本実装と PGI compiler の性能比はおおよそ IPC の比と近似することから IPC の差が性能に影響していると言える.特に命令間の依存によるストールの発生率が例えばクラス B で本実装は 49% なのに対して PGI compiler は 74% となっていた.PGI compiler は本実装と同じく CUDA コードへの変換を行い NVCC によるコンパイルを行っているが,最適化により元のコードから大きく変更されており NVCC が最適化を行いにくくなったと考えられる.

図 4.7: EP の性能

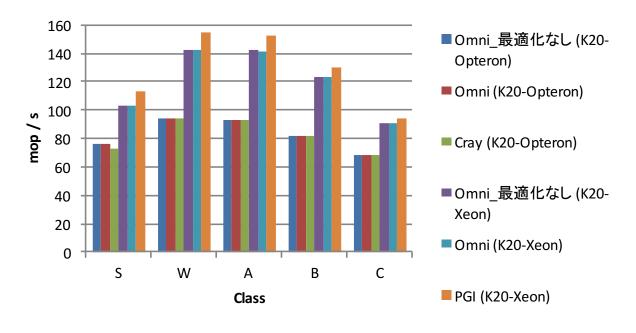

IS

IS ベンチマークの性能を図 4.8 に示す. 評価時点では OpenACC 2.0 の機能である atomic 指示文に 対応していなかったためヒストグラム計算は CPU で実行し、prefix sum のみオフロードするコードを用意した。そのため実行時間の 90% 以上が CPU での計算となり、全体的に他のベンチマークより性能が低下した。 K20-Opteron においては、Cray compiler と比較しクラス S では 1.05 倍の性能となったがそれ以外では同等の性能が得られた。 K20-Xeon においては、PGI compiler と比較し 0.90-0.97 倍の性能となった。 PGI compiler より性能が低下していた原因としてホストコードのコンパイラの違いが考えられる。 本実装は K20-Opteron 上ではホストコードのコンパイラに同じ Cray compiler を用いたが、 K20-Xeon 上では GCC を用いたことでホストコードの性能差が生まれ、それが直接性能に表れている。

#### FT

FT ベンチマークの性能を図 4.9 に示す。K20-Opteron においては、全てのクラスで Cray compiler の 0.66–0.86 倍であり低い性能となった。K20-Xeon においては、PGI compiler はクラス S のみ正しく動作し、それ以外はメモリアクセスエラーによりプログラムが終了した。こちらも同様に PGI compiler の 0.78 倍の性能しか得られなかった。FT における性能低下の原因は gang private 配列用のメモリ確保・解放と非効率なカーネルである。問題サイズが小さい時は前者が、問題サイズが大きい時は後者が主な原因となっていた。FT では FFT のカーネルに各 gang でプライベートに持つよう指定された配列がある。配列サイズが小さければ Shared メモリを利用することができるが、Shared メモリを超える大きさの場合にはグローバルメモリを代わりに使うことになる。FT の場合、クラス S においても各 gang に 67584 byte 必要になるため Shared メモリでは足りずグローバルメモリを使わなければいけない。Cray compiler では

図 4.8: IS の性能

各カーネルの最初の実行時に確保したグローバルメモリをその後の実行で再利用していたため頻繁な確保・解放は行われていなかった。一方本実装はカーネル実行毎に確保・解放を行っていたため、そのオーバーヘッドが発生した。

次に非効率なカーネルとなった原因であるが、CG、EP、ISではループのネストは単純な1重、2重ループであったのに対して、FFTのカーネルでは gang で並列化するループの内に複数の vector で並列化するループがありカーネル内で vector-single モードと vector-partitioned モードが切り替わる。本実装では vector-single モードをモデルと同じく1スレッドで実行するよう変換を行う。例えば vector-single モードにて変数が宣言されて値が代入される場合、Shared メモリ上に変数を確保し1スレッドのみがその変数へ書き込みを行う。そのため Shared メモリメモリへのアクセスが増え、モードの切り替え時にはスレッド間の同期が必要になる。一方で、Cray compiler では変数は各スレッドのローカルなレジスタとして保持しておき、vector-single モードにも関わらずすべてのスレッドで読み書きを行う。処理結果はこちらでも正しくなるため問題はなく、Shared メモリへのアクセスやスレッド間での同期が減少し性能が向上していると考えられる。

#### MG

MG ベンチマークの性能を図 4.10 に示す。K20-Opteron においては Cray compiler と比較し、0.68-0.90 倍の性能しか得られなかった。K20-Xeon においては、PGI compiler では結果不正が起きたため、評価できなかった。MG での性能低下の主な原因は gang private 配列の確保・解放にある。Cray compiler ではクラス S では Shared メモリを、それ以外ではグローバルメモリを使用していたが各カーネルの最初の実行時にのみ確保していた。そのため非同期カーネル実行を連続して行うことができた。一方本実装では毎回カーネル実行前後に確保・解放したため、GPU メモリを解放する cudaFree 関数で GPU との同期が発

図 4.9: FT の性能

生し,効果的にカーネルを起動できなかった.

# 4.2 PEZY-SC 向け OpenACC コンパイラ

NVIDIA GPU 向けの Omni OpenACC compiler を拡張し、アクセラレータとして PEZY-SC を利用可能 とした。PEZY-SC のプログラミングには PZCL を用いるため、トランスレータで出力するカーネルコードを PZCL 向けに変更し、ランタイムを PZCL で実装した。コンパイル処理は NVIDIA GPU 版 (図 4.1) における CUDA を PZCL で置きかえたものとなる。

#### 4.2.1 NVIDIA GPU 向け実装からの変更点

#### ホストコード

基本的にはホストコードから呼び出される Omni OpenACC runtime において CUDA で記述していた部分を OpenCL(PZCL) で記述することで対応した。またその際に、ランタイム内部で CUDA や OpenCL に依存しない部分を切り分けることで最小限の実装で CUDA と OpenCL のどちらでも対応可能としている。 PEZY-SC に向けて特に変更したのはカーネルの起動部分で、PEZY-SC では global\_work\_size を 128 の倍数かつ 8192 以下になるよう調整し、local\_work\_size は 8 で固定としている。

#### デバイスコード

OpenACC の並列性と PEZY-SC の並列性の対応関係は、現在の実装では gang を PE に、worker を 1 で固定し、vector を PE 内のスレッドに割り当てている。このマッピングは NVIDIA GPU 向けの実装を

図 4.10: MG の性能

ほぼそのまま使用できるという理由で用いているが、最適なマッピングについては検討の余地がある. PEZY-SC のプログラミングを行う上で NVIDIA GPU と最も異なる点が、階層的なキャッシュにコヒーレンシがなく、プログラマが適宜フラッシュを行わなければならない部分である。ループのワークシェアリングに関して考えると、gang すなわち PE での並列化を行った後に各 PE が書き込んだデータをすべての PE で同じように読み出すためにはすべての階層のキャッシュをフラッシュしなければならないため、flush() を実行する (flush() を実行すると同期も行われるため sync() は必要ない). vector すなわちスレッドでの並列化のあとに、PE 内の各スレッドが書き込んだデータを PE 内の 8 つすべてのスレッドで同じように読み出せるようにする必要があるが、1 PE 内の全スレッドは同じキャッシュを用いるためコヒーレンシに関して特に何もする必要はなく、スレッド間の同期のみで良い。またカーネル内で呼び出されるループのワークシェアリングする際の担当範囲計算やリダクションのための関数を PZCL の組み込み関数を用いるように書き換えている.

#### 4.2.2 最適化

PEZY-SC 向けに最適化するためコード生成の改善や拡張機能の実装を行った。1 つめはカーネルマージである。これは OpenACC kernels 指示文における最適化である。kernels 指示文は対象領域のコードをコンパイラが適宜分割していくつかのカーネルとして実行するものである。NVIDIA GPU 向けの実装ではカーネル実行中に全スレッドでの同期を取ることができないため、kernels のコードは gang すなわちスレッドブロック間での並列ループの単位で分割して複数のカーネルとして実行するようにしている。一方で、PEZY-SC ではプロセッサの全スレッドで同期をとる命令 (sync()) があるため、kernels の対象領域を1つのカーネルとして変換することが可能である。これによりカーネル起動のオーバーヘッ

```

#pragma acc yield

#pragma acc sync[(int-expr)]

#pragma acc flush[(int-expr)]

```

図 4.11: yield, sync, flush 指示文の構文

ドを最小限にすることができる.

2 つめは明示的なスレッド切り替え、同期、フラッシュのための指示文の追加である。追加した yield,sync,flush 指示文の構文を図 4.11 に示す。PEZY-SC では 1PE 内のスレッドは実際には 4 つの表裏のスレッドペアであり、通常は表裏のどちらかしか実行されず、同期命令やスレッド切り替え命令に 到達した際に反対側が実行される。明示的にスレッドの表裏を切り替えることにより、キャッシュ利用率 向上やメモリアクセスレイテンシの隠蔽が可能である。yield 指示文によりユーザがスレッドを切り替えるタイミングを指定できるようにした。また MIMD ではあるが同期をとって動作したほうが効率よく キャッシュを利用できることがあるのでユーザが任意のタイミングで同期を取れるように sync, flush 指示文を追加している。sync と flush には引数として整数値を指定可能で、同期・フラッシュ時のキャッシュレベルを指定するものである。例として "#pragma acc sync(2)" と指定した場合は L2 キャッシュがある City レベルでの同期 sync L2() が実行される。引数を指定しない場合は全体での同期・フラッシュとなる。

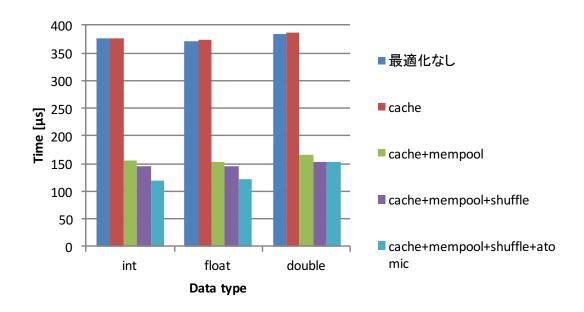

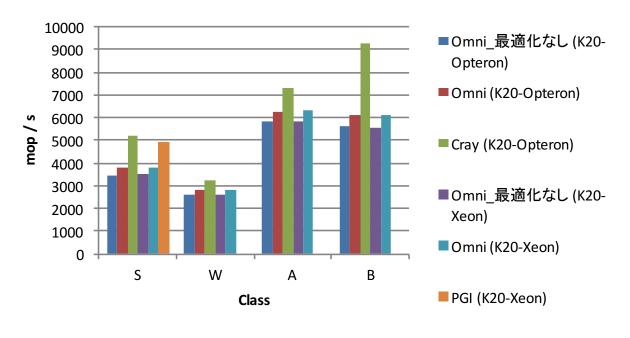

#### 4.2.3 評価

評価には N-body と NPB-CG ベンチマークを用いた。N-body は相互作用する粒子の動きをシミュレーションするもので、単精度浮動小数点を用いて全粒子ペアの相互作用を計算するナイーブな実装である。 NPB-CG は正値対称な大規模疎行列の最小固有値を共役勾配法で求めるベンチマークである。 PZCL 版と OpenACC 版を実装し、性能と生産性について比較する。

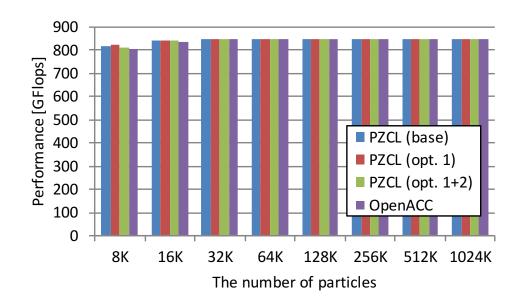

#### 性能評価

性能評価のために高エネルギー加速器研究機構 (KEK) の青睡蓮を利用した。そのノード構成とソフトウェアを表 4.2 に示す。PEZY-SC における N-body の性能を図 4.12 に示す。凡例の "PZCL (base)" は特に最適化をしていない PZCL コード,"PZCL (opt. 1)" はカーネルマージ (opt. 1) を加えた PZCL コード,"PZCL (opt. 1+2)" はさらに明示的スレッド切り替え (opt. 2) を加えたコード,"OpenACC (base)" は特に最適化を加えていない OpenACC コードである。性能の Flops は 1 相互作用計算に 38 FLOP を要すると仮定して算出している [21]。OpenACC 版の性能は PZCL 版の 97.8-100.0% であった。このベンチマークにおいては相互作用の計算時間が支配的であり,カーネルマージと明示的スレッド切り替えの効果はほぼなかった。

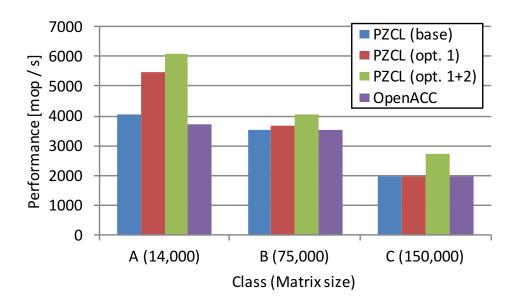

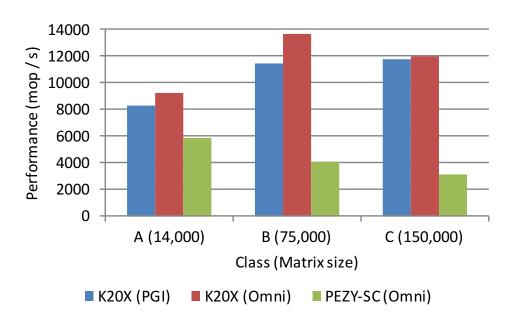

次に PEZY-SC における NPB-CG ベンチマークの性能を図 4.13 に示す。OpenACC 版の性能は PZCL(base) 版の 91.9% 以上であった。OpenACC 版ではループ分散やランタイムのオーバーヘッド および不必要なデータ転送があり特に Class A で性能が低下している。OpenACC ではリダクションの対

|             | 青睡蓮 (Suiren Blue)                       |  |

|-------------|-----------------------------------------|--|

| CPU         | Intel Xeon-E5 2618Lv3 2.3 GHz           |  |

| Memory      | DDR4 64 GB, 1866 MHz                    |  |

| Accelerator | PEZY-SC×4                               |  |

| Peak perf.  | SP: 3 TFlops, DP: 1.5 TFlops            |  |

| Memory      | DDR4 16 GB, 1333 MHz, 85.3 GB/s         |  |

| Compiler    | ICC 14.0.2, PZSDK 2.1,                  |  |

|             | Omni OpenACC compiler 0.9.3 for PEZY-SC |  |

表 4.2: 青睡蓮のノード構成とソフトウェア

図 4.12: PEZY-SC における N-body ベンチマークの性能

象の変数は最初にホストからデバイスに転送されるが、初期値がゼロの場合には実際には不必要であるためその部分でオーバーヘッドが生じている。カーネルマージによる最適化はカーネルオーバーヘッドの割合が大きくなる疎行列サイズが小さな時に特に効果が大きかった。明示的スレッド切り替えによる最適化は逆に行列サイズが大きな時に効果が大きかった。これはスレッドを切り替えることでキャッシュが追い出される前に逆側のスレッドがキャッシュを利用できたからである。最終的に PZCL(opt.1+2) 版と比べて OpenACC 版は 61.6–87.5% の性能であった。

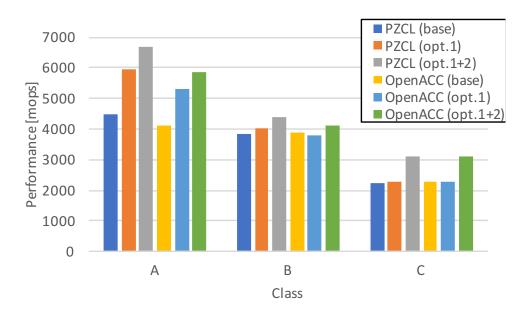

その後 OpenACC に kernels 指示文においてカーネルを 1 つにまとめる最適化 (opt.1 に相当),および拡張の yield 指示文 (opt.2 に相当) を導入して NPB-CG の評価を再度行った。なお青睡蓮の構成が変わったため,再度そのノード構成とソフトウェアを表 4.3 に示す。図 4.14 に再度評価した NPB-CG の性能を示す。凡例の "OpenACC (opt. 1)" が OpenACC コードにおいてコンパイラでカーネルマージを行ったもの,"OpenACC (opt. 1+2)" が OpenACC コードにおいてコンパイラでカーネルマージを行いか

図 4.13: PEZY-SC における NPB-CG ベンチマークの性能

|              | 青睡蓮 (Suiren Blue)                       |  |

|--------------|-----------------------------------------|--|

| CPU          | Intel Xeon-E5 2618Lv3 2.3 GHz           |  |

| Memory       | DDR4 64 GB, 1866 MHz                    |  |

| Accelerator  | PEZY-SCnp×4                             |  |

| Peak perf.   | SP: 3 TFlops, DP: 1.5 TFlops            |  |

| Memory       | DDR4 16 GB, 1333 MHz, 85.3 GB/s         |  |

| Interconnect | InfiniBand: Mellanox Connect-X3 FDR     |  |

| Compiler     | ICC 14.0.2, PZSDK 3.0,                  |  |

|              | Omni OpenACC compiler 1.1.2 for PEZY-SC |  |

表 4.3: 青睡蓮のノード構成とソフトウェア

つ yield 指示文でスレッド切り替えを指定したものである。Class A において、PZCL と OpenACC の それぞれのバージョンを比較すると OpenACC 版は 88–91% の性能であった。どのバージョンも同じように性能が落ちており、OpenACC の変換によるオーバーヘッド、余計なデータ転送で遅くなっていると 考えられる。しかしながら、Class C においては PZCL と OpenACC のどのバージョンも OpenACC 版で 99% 以上の性能が出ている。OpenACC においても PZCL と同様の最適化が適用されてかつ演算時間の 比率が高くオーバーヘッドが見えなくなっているからである。

また比較として NVIDIA Tesla K20X における OpenACC 版の性能を評価した. 評価は筑波大学計算科学研究センターの HA-PACS/TCA [22] で行った. 表 4.4 にノード構成とソフトウェアを示す. N-body, NPB-CG の OpenACC コードの K20X と PEZY-SC における性能を図 4.15 と 4.16 に示す (PEZY-SC の性能は OpenACC(opt.1+2) を再掲). K20X においては, PGI compiler と Omni OpenACC compiler の 2

図 4.14: PEZY-SC における NPB-CG ベンチマークの性能 (OpenACC に最適化を追加)

|                                             | HA-PACS/TCA                                           |

|---------------------------------------------|-------------------------------------------------------|

| CPU                                         | Intel Xeon-E5 2680v2 2.8GHz×2                         |

| Memory                                      | DDR3 128GB, 1866MHz                                   |

| Accelerator                                 | Tesla K20X×4                                          |

| Peak perf. SP: 3.95 TFlops, DP: 1.31 TFlops |                                                       |

| Memory                                      | GDDR5 6GB, 250 GB/s                                   |

| Interconnect                                | InfiniBand: Mellanox Connect-X3 FDR (PCIe Gen.2×8 接続) |

| Compiler                                    | PGI 15.10, CUDA 7.5,                                  |

|                                             | Omni OpenACC compiler 0.9.3                           |

表 4.4: HA-PACS/TCA のノード構成とソフトウェア

つを用いて計測した。N-body ベンチマークにおいて,K20X では Omni は PGI の半分以下の性能しか得られなかった。これは粒子データ (float 型 4 要素から成る構造体) を PGI では 128bit 長でベクトルとしてロードしていたのに対して,Omni では 32bit 長でスカラとしてロードしていたためである。PGI を用いた K20X の性能と比較すると,Omni を用いた PEZY-SC の性能は 23-29% しか出ていない。N-Body では粒子間の距離から相互作用の力を求める際に平方根の逆数の計算が必要となるが,SFU が K20X では全体で 448 個 (32 units/SMX × 14 SMX) あるのに対して PEZY-SC では 64 個 (1 unit/city × 64 city) しかないため,その部分で性能が律速されていると言える。NPB-CG ベンチマークにおいては,K20X では Omni のほうが PGI よりも高い性能が出ており,これは CUDA コンパイラの最適化によるものである。Omni を用いた K20X の性能と比較すると,Omni を用いた PEZY-SC の性能は 26-64% であった。PEZY-SC はデバイスメモリのバンド幅が低いのが原因と考えられる。

図 4.15: K20X と PEZY-SC における OpenACC 版 N-body ベンチマークの性能

図 4.16: K20X と PEZY-SC における OpenACC 版 NPB-CG ベンチマークの性能

#### 生産性評価

PZCL では OpenCL と同様にデバイスメモリの管理やカーネルの実行をプログラマが多くの複雑な API を用いて記述する必要があり、かつカーネルにおける並列処理は PZCL 独自の方法で書く必要がある。一方で、OpenACC ではプログラマは逐次コードに指示文を追加するのみで非常に簡易にアクセラレータにオフロードと並列化することを指定可能である。また OpenACC は標準仕様であり、対応するコンパイラ

4.3 関連研究 44

|                | N-Body  | NPB CG   |

|----------------|---------|----------|

| Serial         | 109     | 418      |

| PZCL (opt.1+2) | 240     | 1001     |

| OpenACC        | 114 (5) | 447 (25) |

表 4.5: N-Body と NPB-CG の SLOC. (内数は指示文の行数)

があれば他のアクセラレータでも実行可能である.

生産性を定量的に評価する指標の一つとして Source Lines Of Code (SLOC) を計測した。N-Body と NPB-CG の PZCL 版と OpenACC 版の SLOC を表 4.5 に示す。OpenACC 版の SLOC は PZCL 版に対して、N-Body で 48%、NPB-CG で 45% に抑えられており、かつ逐次版とほとんど差がない。逐次版からほぼ指示文の追加で記述できていることから OpenACC の生産性が PZCL よりも高いことは明らかである。

### 4.3 関連研究

CPU 向けの OpenMP から CUDA へ変換を行うコンパイラである OpenMPC[23] が提案されている. 既存の OpenMP コードをそのまま利用して NVIDIA GPU 上で動作させることが可能である. さらに独自の指示文を使ったチューニングや, パラメータ探索によるブロックサイズなどのチューニングが可能である. また独自の指示文により CUDA をプログラミングできる hiCUDA[24] が提案されている. hiCUDA はループの分散方法 (スレッドブロックに分散するかスレッドに分散するか) や, スレッドブロック数やスレッド数などを明示しなければならない. そのため CUDA のプログラミングに近く CUDA と同等の性能を得やすいが, CUDA に依存しており NVIDIA GPU 以外での利用は難しい.

OpenACC コンパイラでは accULL[25], OpenUH-OpenACC[26], OpenARC[27], RoseACC[28] がある.また GCC でも OpenACC への対応が進められている [29]。accULL は最初のオープンソース OpenACC コンパイラであり、Python ベースの YaCF というソース・プログラム変換を行うコンパイラフレームワークを用いてコードを最適化し C を CUDA または OpenCL コードに変換する。現在は単純なループにしか対応しておらず、コンパイルできるプログラムには制限がある。OpenUH-OpenACC はコンパイラフレームワーク OpenUH を用いた OpenACC コンパイラで C から CUDA コードへの変換を行う。CUDA のブロック及びスレッドへの柔軟なループのマッピングや NVIDIA GPU 向けのリダクションの汎用な実装に関して研究されている [30]。多くのプログラムをコンパイル可能であるが、公開されているものは GPU カーネルをホストと非同期に実行するための "async" 節に対応しておらず、プログラムの高速化が難しい。OpenACC はアクセラレータ向けコンパイラフレームワークであり、オープンソースでは初めて OpenACC1.0 の全機能をサポートしている。OpenACC の C/C++ コードを CUDA や OpenCL に変換する。Cetus compiler infrastructure を元に作られており、様々なコード解析や変換およびオートチューニング機能が備わっているしかしながら 2018 年 1 月現在においてもクローズドベータであり一般にはコードが公開されていない。RoseACC はオープンソースコンパイラである Rose Compiler ベースの OpenACC コンパイラで、C から OpenCL コードへの変換を行う。GCC では C/C++/Fortran から NVIDIA GPU 向

けに PTX に変換する実装が行われている。これら OpenACC コンパイラは本研究とほぼ同時期もしくは本研究より後に行われている。

本実装で評価に用いる NAS Parallel Benchmarks については、Seo らにより OpenCL による実装や最適 化が行われている [31]. OpenACC による実装が PathScale により行われたが、PGI compiler でコンパイルすると EP、SP 以外のベンチマークでコンパイル時エラーや実行時エラーが発生する [32]. また Xu らにより NPB のすべてのベンチマークが OpenACC で実装されている [33]. 本研究では独自に OpenACC で実装して評価に用いた.

OpenMP は version 4.0 からアクセラレータへのオフロードを target 指示文によりサポートしている。OpenMP と OpenACC のオフロードの指示文はよく似ているように見えるが、並列化の指定の仕方が大きく異なる。OpenMP はどこで並列領域を作りどのループをワークシェアリングするかをプログラマが記述し、その通り並列化される。明示的であるためプログラマが制御しやすいが、アクセラレータごとに並列数や並列性の階層が異なるため可搬性には難がある。OpenACC はどのループを並列化できるかを指定し、コンパイラがアクセラレータに適した並列化を行う。当然 gang,worker,vector のどれで並列化するかを指定可能だが必須ではなく、そもそもそれらがハードウェアにどう対応付けられるかはコンパイラ依存である。したがってアクセラレータの並列性に依存しないため可搬性は高まるが、コンパイラの実装によっては性能の低下がありうる。

4.3 関連研究 46

# 第5章

# XcalableACC コンパイラの設計・実装

本章では、演算加速機構を持つ並列システム向け PGAS 言語 XACC のコンパイラを設計・実装し、ベンチマークにより評価する。 グローバルビューモデルの通信指示文を NVIDIA GPU と PEZY-SC 向けに、ローカルビューモデルの coarray を NVIDIA GPU 向けに実装し、Himeno benchmark と NPB CG により性能と生産性を評価する。

### 5.1 設計

Omni XACC compiler は XACC コードから OpenACC コードへ変換する source-to-source コンパイラである。OpenACC コードに変換する理由は、アクセラレータコードの生成を OpenACC コンパイラに任せることで可搬性の向上と実装の簡略化が可能であるからである。Omni XACC compiler は理研 ACIS と 筑波大学で開発している XMP のリファレンス実装である Omni XMP compiler[17] の拡張であり、現在はグローバルビューモデルの指示文を C と Fortran で、ローカルビューモデルの coarray を C のみで対応している。

図 5.1 にそのコンパイル処理の流れを示す。XACC トランスレータは入力の XACC コードを XACC ランタイム呼び出しが含まれた OpenACC コードに変換する。グローバルビューモデルに対する変換では指示文で分散が指定された配列やループを変換し、通信指示文を通信コードに置き換える。この際、複雑な処理の多くは XACC のランタイム呼び出しに変換する。ローカルビューモデルに対する変換では、coarray を通常の配列に変換して通信部分を XACC ランタイムライブラリ呼び出しに置き換える。グローバルビューとローカルビューモデルの変換は基本的に独立して行われる。XACC コードに含まれる OpenACC 指示文は、変換に伴う変数のリネームや coarray 確保部分で変化はあるものの、基本的には元の

図 5.1: Omni XACC compiler におけるコンパイル処理の流れ

5.2 実装 48

コードと同じ OpenACC 指示文が出力される. 出力された OpenACC コードは OpenACC compiler (Omni OpenACC compiler, PGI compiler, Cray compiler, 等) でコンパイルし, Omni XACC ランタイムライブラ リとリンクする.XACC ランタイムライブラリには XMP および XACC のランタイムルーチンが含まれ る.XACC の通信ライブラリは NVIDIA GPU 向けと PEZY-SC 向けの 2 種類がある.NVIDIA GPU 向 けの実装は MPI と CUDA により記述している。GPU メモリの転送には基本的には CUDA メモリの転送 に対応した MPI の機能を利用している.CUDA に対応した MPI として MVAPICH2[34], OpenMPI[35] 等があり,これらの MPI 実装では MPI 関数の引数に GPU メモリアドレスを直接指定してホストメモリ と同じように通信することが可能であり、内部的にホストバッファ経由もしくは GPUDirect RDMA に よって直接通信を行う [36].なお reflect, reduction 指示文など一部の通信指示文は CUDA に対 応していない MPI でも利用できるようにホストメモリ経由で通信する実装もある.また不連続データ の通信に対しては CUDA カーネルによるパックやアンパックをして転送するようにしている. さらに, coarray 機能の実装には MPI 3.0 から導入されたリモートメモリアクセス (RMA) 機能を用いている. 現 在多くの MPI 実装では MPI 3.0 に対応しており,MVAPICH2, OpenMPI は GPU メモリに対してもこの 機能を利用可能である. PEZY-SC 向けの実装には MPI と PZCL を用いている.MPI には PEZY-SC の メモリ転送機能がないため,PZCL と MPI を組み合わせてホストメモリを経由して通信する.PEZY-SC 向けの実装は現在 reflect 指示文のみ対応している.

## 5.2 実装

#### 5.2.1 reflect 指示文

XACC の reflect 指示文では、ある分散配列の袖交換時に通信バッファの確保や MPI の persistent 通信の登録等を行い、次回以降同じ分散配列に対して同じ設定で実行される reflect 指示文があった際には登録された設定を使い回すようにしている。 XACC では加えて、通信の登録のみ行う reflect\_init 指示文と、登録された袖通信を行う reflect\_do 指示文に分けて記述することも可能であり、予期しない通信の再初期化や登録を防ぐことができる。 村井らによって XMP における reflect 指示文の効率的な実装が行われており、不連続となる次元の通信においても、通信はブロックストライド (ブロック長・ストライド長・個数で表現可能な不連続領域)として表現できることが示されている [37]。 本実装では、不連続な次元の送信時には XACC ランタイムライブラリ内の CUDA カーネルによりブロックストライドを GPU メモリ上でパックして連続領域を送受信するようにしている。 通信は MPI\_Send\_init/Recv\_init()により persistent 通信として登録を行い、MPI\_Startall()/Waitall() により登録された通信を実行する。PEZY-SC 向けの実装においては PEZY-SC 上でのカーネルによるパック・アンパックに加えてホストメモリのバッファを介した通信するようにしている。

#### 5.2.2 reduction 指示文

reduction 指示文の実装には XMP と同様に MPI\_Allreduce() を用いた. XMP および XACC の reduction 指示文では, あるアドレスのデータをリダクションした結果を同じアドレスに保存しな ければならないので, MPI\_Allreduce() を呼び出す際には送信バッファに MPI\_IN\_PLACE を指定する.

図 5.2: NPB CG にて用いられる gmove (4 ノード)

CUDA に対応した MPI を用いている場合には、既存の XMP のリダクション用ランタイムライブラリ に OpenACC host\_data 指示文により GPU のポインタを渡すように変更した。 MPI が CUDA に対応していない場合には、アクセラレータのデータをホストに確保したメモリにコピーし、そのデータに MPI\_Allreduce() を実行した後にアクセラレータへ書き戻すように実装した。

## 5.2.3 gmove 指示文

gmove 指示文は任意の通信を記述できるがすべてのパターンに対応するのは困難であるため、評価に用いる NPB CG で現れる 1 パターンについてのみ実装した。それは図 5.2 のように、2 次元テンプレートのある次元で分散された 1 次元配列を同一テンプレートの他の次元で分散された 1 次元配列に代入するパターンである。最初に XMP の gmove 指示文の実装の調査を行った。その結果、ノードの行数と列数が同じ場合には効率よく通信ができているが、ノードの行数と列数が異なる場合において非効率な通信が行われていた。例えば CG ではノードの列数が行数の 2 倍となることがあり、その際に図 5.3 に示す通信が行われていた。ノードの半分は 2 つのノードにデータを送る一方で、他の半分のノードはどこにもデータを送っていないためバランスが悪いうえに、同じノードで保持するデータも他のノードから送信しているので効率が悪い。そこで通信を図 5.4 に示すように全ノードが 1 つのノードに送るように改善した。さらに現在の実装では通信相手や送受信の範囲を求める計算部分が非常に複雑になっているため、通信相手と送受信の範囲をキャッシュすることで 2 度目以降は直ちに MPI 通信を開始できるようにしている。

5.2 実装 50

図 5.3: NPB-CG の gmove の改善前 (8 ノード)

図 5.4: NPB-CG の gmove の改善後 (8 ノード)

### 5.2.4 coarray 機能

XACC における coarray の MPI による実装方法について解説する。なお、現在は NVIDIA GPU のみで対応している。MPI では、プロセスは window を通してリモートメモリにアクセスする。Omni compiler ではすべての coarray をホストメモリ用の window とアクセラレータメモリ用の window の 2 つで管理する。これにより coarray の同期をまとめて行うことが可能である。XACC は初期化時に coarray 用のヒープメモリをホスト用と GPU 用に確保し、それに関連付けた window をそれぞれ作成する。ヒープメモリサイズは環境変数 "XMP\_ONESIDED\_HEAP\_SIZE" から指定が可能であり、すべての coarray のサイズの合計がこれを超えないように設定する必要がある。MPI の RMA は window のアクセスエポック内で

しか発行できない. そこで本実装では初期化の時に MPI\_Win\_lock\_all() によりアクセスエポックを開始し、MPI\_Win\_unlock\_all() により終了する. これによってユーザプログラム中では任意のタイミングでcoarray による通信が可能となる.

ソースコード 5.1 とソースコード 5.2 はアクセラレータ上の coarray 宣言とそれを変換したコードである.

#### ソースコード 5.1: アクセラレータ上の coarray 宣言

```

1 int A[64]:[*];

2 #pragma acc declare create(A)

```

#### ソースコード 5.2: アクセラレータ上の coarray 宣言を変換したコード

```

1 void * _XMP_COARRAY_DESC_A;

2 int * _XMP_COARRAY_ADDR_A;

3 int * _XMP_COARRAY_ADDR_DEV_A;

4

5 extern void xmpc_traverse_init_file_sample_pp()

6 {

7 _XMP_coarray_malloc_info_1(0x40, sizeof(int));

8 _XMP_coarray_malloc_image_info_1();

9 _XMP_coarray_malloc_do(&(_XMP_COARRAY_DESC_A),&(_XMP_COARRAY_ADDR_A));

10 _XMP_coarray_malloc_do_acc(&(_XMP_COARRAY_DESC_A),&(_XMP_COARRAY_ADDR_DEV_A));

11 acc_map_data(_XMP_COARRAY_ADDR_A,

12 __XMP_COARRAY_ADDR_DEV_A,

13 __XMP_coarray_get_total_elmts(_XMP_COARRAY_DESC_A)*sizeof(int));

14 }

```

coarray A[] が宣言されていてかつ declare 指示文で指定されているので、この coarray はホストメモリとアクセラレータメモリの両方に確保される。  $XMP\_COARRAY\_DESC\_A$  は coarray A[] のホストアドレス・アクセラレータアドレス・形状等を保持した構造体へのポインタである。  $XMP\_COARRAY\_ADDR\_A$  は coarray のホストアドレス,  $XMP\_COARRAY\_ADDR\_DEV\_A$  は coarray のアクセラレータアドレスでローカルの coarray アクセスに用いられる。この変換コードでは省略されているが,実際にはまず coarray 用のヒープ確保や window 作成が行われる。その後、このソースコードに示してある xmpc\\_traverse\_init\_file...() が呼び出される。この関数はコンパイルの翻訳単位における初期化関数で、Omni compiler でリンクする際にはすべてのファイルの初期化関数を呼ぶルーチンが作成される。関数内では coarray A[] のサイズやイメージの情報を設定したのちに, $XMP\_coarray\_malloc\_do()$  によりホスト側の coarray が、 $XMP\_coarray\_malloc\_do\_acc()$  によりアクセラレータ側の coarray がヒープメモリから確保される。最後に、OpenACC の acc $\_map\_data()$  を用いてホストメモリとアクセラレータメモリの対応付けを行うことでOpenACC から利用可能としている。

次に coarray による通信について述べる. coarray の put と get 操作は、それぞれ MPI\_Put() や MPI\_Get() により行われる。 それらの関数ではリモートの window とそのオフセットに対して、ローカルのポインタのデータを put またはそのポインタの場所に get する. coarray の代入文におけるリモートの coarray が use\_device 節で指定されているなら、アクセラレータ側の window を、そうでなければホスト側の

5.2 実装 52

window を使用する。ローカルの変数や配列や coarray が use\_device 節で指定されているなら,アクセラレータメモリのポインタを,そうでなければホストメモリのポインタを使用する。MPI\_Put/Get() は非同期関数で通信の完了までは保証しない。リモートの coarray やローカルの配列に対して安全に読み書きを行うため,本実装では MPI\_Put/Get() の直後に MPI\_Win\_flush() により通信の完了を待つようにしている。しかしながら,put/get ごとに完了待ちをすると依存のない通信を同時に発行できないという問題があるため,改善を検討している。現在の実装では,試験的に環境変数 "XMP\_PUT\_NB" や "XMP\_GET\_NB"を設定することで,通信をノンブロッキングにできるようにしている。なお,その際にはユーザ側が同期を行うまでの coarray 通信間で依存がないことを保証しなければならない。ソースコード 5.3 とソースコード 5.4 にアクセラレータ上の coarray 通信とその変換後のコードを示す。

#### ソースコード 5.3: coarray によるアクセラレータメモリ間の put 通信

```

1 //This statement puts array B on device to coarray A on device

2 #pragma acc host_data use_device(A, B)

3 A[:]:[2] = B[:];

```

#### ソースコード 5.4: coarray によるアクセラレータメモリ間の put 通信を変換したコード

この例では、coarray A[] と B[] はアクセラレータ上に確保されており、use\_device 節によりアクセラレータ側のデータを通信の対象としている。すなわちこの通信では自ノードのアクセラレータ上の B[] をイメージ 2 のアクセラレータ上の coarray A[] に put する。変換後のコードでは、まず同様に use\_device により配列 A[],B[] に対してアクセラレータアドレスを用いるようにする。  $XMP_coarray_rdma_...()$  では通信する coarray サイズ、配列サイズ、イメージ番号を設定したのち、 リモート window にアクセラレータ用の window を用いる  $XMP_coarray_rdma_do_acc()$  で通信を実行する。 なお通信先がホストの coarray の場合には  $XMP_coarray_rdma_do()$  を用いる。

同期に関しては、まず xmp\_sync\_memory() は MPI\_Win\_sync() によって window の同期を取りかつコンパイラ最適化などによる前後のコードの入れ替わりを防ぐ. もし put/get がノンブロッキングになるよう環境変数を指定していた場合は、MPI\_Win\_flush\_all() によって自プロセスが発行したすべての RMA の完了を待機する。xmp\_sync\_image() や xmp\_sync\_images() は MPI\_Send/Recv() による 1 対 1 同期の前後に xmp\_sync\_memory() を入れることにより実装しており、xmp\_sync\_all() は MPI\_Barrier() による全体同期の前後に xmp\_sync\_memory() を入れることにより実装している。

| -                    |                                      |  |

|----------------------|--------------------------------------|--|

| Compiler             | GCC 4.4.7, CUDA 6.5                  |  |

|                      | MVAPICH2-GDR 2.1a                    |  |

|                      | Omni OpenACC compiler 0.9.1          |  |

| Environment variable | MV2_ENABLE_AFFINITY=0                |  |

|                      | MV2_NUM_PORTS=2                      |  |

|                      | MV2_USE_CUDA=1, MV2_CUDA_IPC=0       |  |

|                      | MV2_USE_GPUDIRECT_GDRCOPY=1          |  |

|                      | MV2_USE_GPUDIRECT_RECEIVE_LIMIT=8192 |  |

表 5.1: HA-PACS/TCA におけるグローバルビューモデルの性能評価に用いたソフトウェアと環境変数

# 5.3 NVIDIA GPU クラスタにおけるグローバルビューモデルの性能 評価

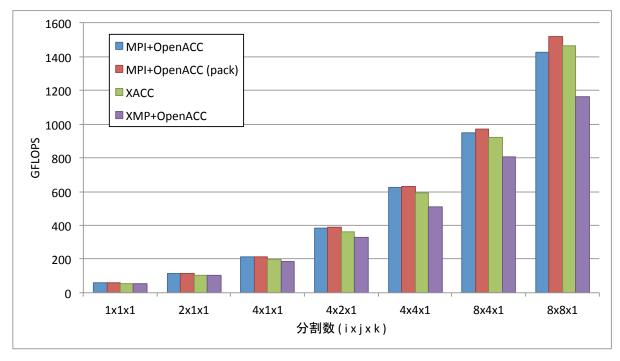

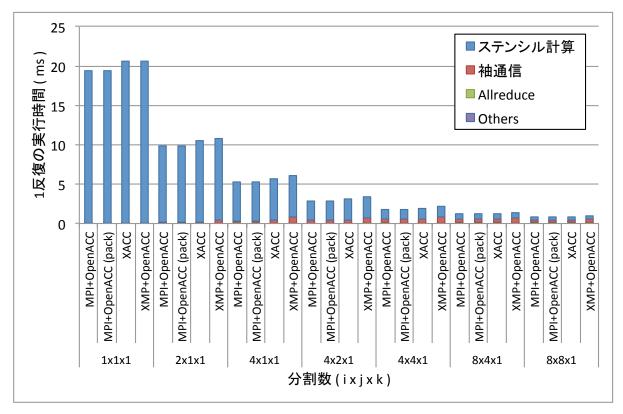

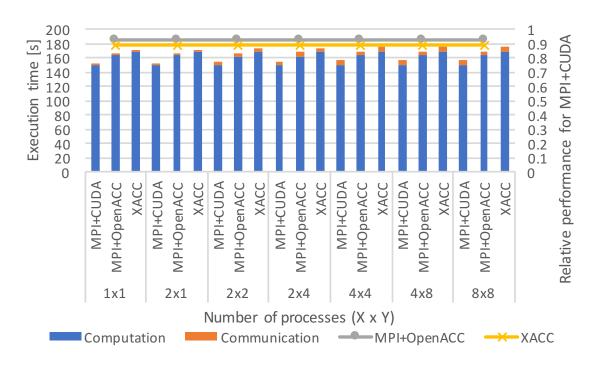

評価には筑波大学計算科学研究センターの HA-PACS/TCA を利用した。1 ノードあたり 4 枚の GPU が搭載されているため、1 MPI プロセス当たり 1 GPU を割り当てて 1 ノードで 4 MPI プロセスを実行し、最大で 16 ノード上で 64 MPI プロセスを実行した。HA-PACS/TCA には GPU 間直接通信のための Tightly Coupled Accelerators (TCA) [38] が搭載されているが、この評価では InfiniBand を用いて一般的なクラスタにおける性能を評価する。また使用したソフトウェアと環境変数を表 5.1 に示す。MPI には CUDA に対応した MVAPICH2-GDR 2.1a を利用し、mpicc のコンパイルオプションには "-O3" を指定した。OpenACC コンパイラには本研究で実装した Omni OpenACC compiler を用い、バックエンドの CUDA コンパイラオプションには "-O3 -arch=sm\_35" を指定した。

#### 5.3.1 Himeno Benchmark

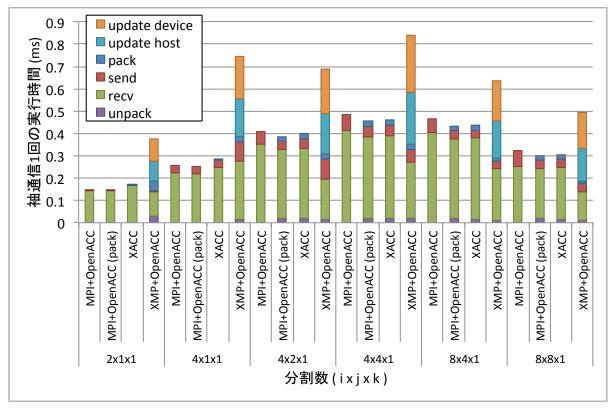

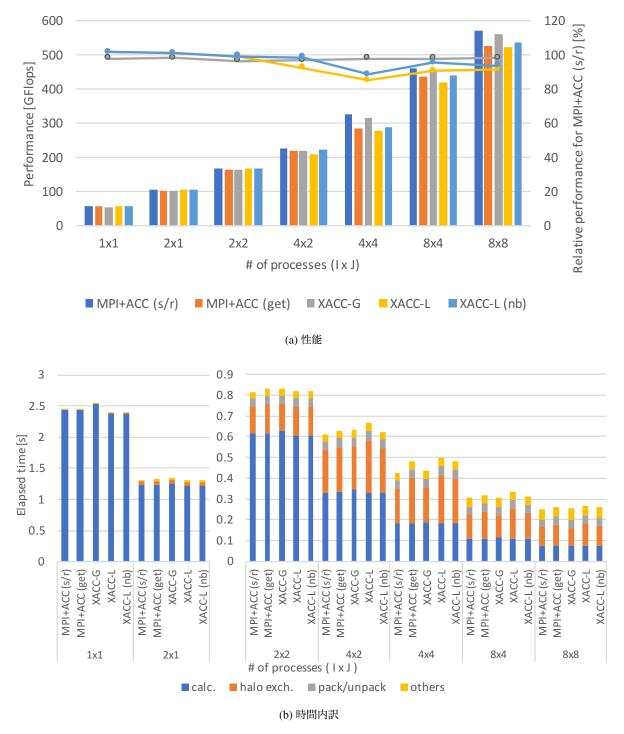

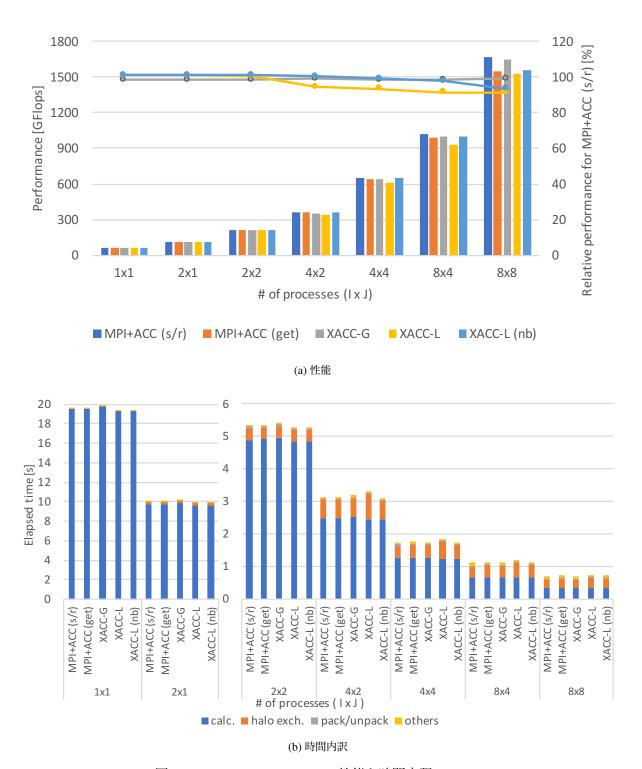

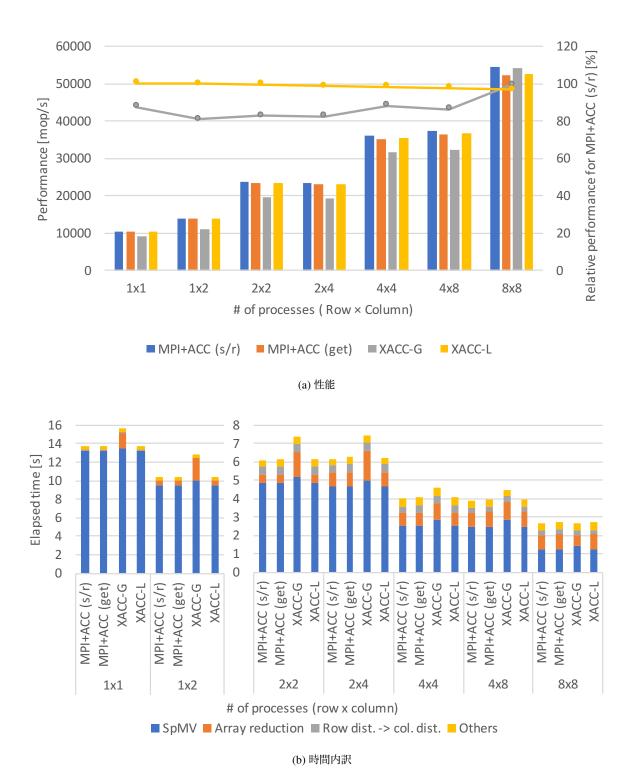

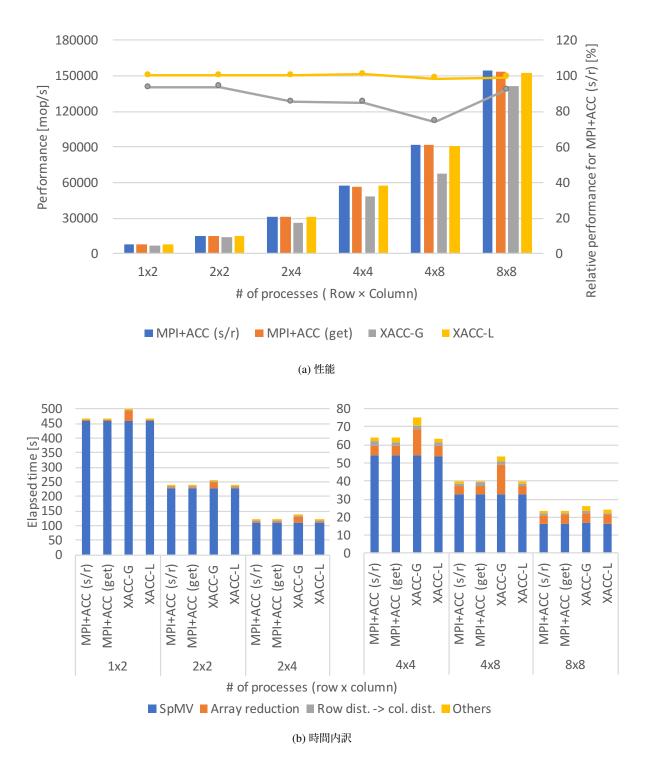

の機能を用いずに XMP と OpenACC で記述した "XMP+OpenACC" とも比較する. 性能測定時の反復回数は 1000 回とし 10 回の計測のうち最良値を使用した.

#### ソースコード 5.5: XACC で記述した Himeno Benchmark

```

1 #pragma xmp template t(0:MKMAX-1, 0:MJMAX-1, 0:MIMAX-1)

2 #pragma xmp nodes n(1, NDY, NDX)

3 #pragma xmp distribute t(block, block, block) onto n

4 \# pragma \times p align p[k][j][i] with t(i, j, k)

5 #pragma xmp shadow p[1:2][1:2][0:1]

6 // 省略した配列bnd, wrk1, wrk2のalignとshadowは配列pと同じ

7 #pragma xmp align a[*][k][j][i] with t(i, j, k)

8 #pragma xmp shadow a[0][1:2][1:2][0:1]

9 // 省略した配列b, cのalignとshadowは配列aと同じ

10 . . .

11 #pragma acc data copy(p,bnd,wrk1,wrk2,a,b,c),create(gosa)

12 {

13 #pragma xmp reflect_init(p) width(1,1,0) acc

14

15

for(n=0; n<nn; ++n){

16

gosa = 0.0;

17 #pragma acc update device(gosa)

19 #pragma xmp loop (k, j, i) on t(k, j, i)

20 #pragma acc parallel loop firstprivate(omega) reduction(+:gosa) collapse(2)

gang vector_length(64) async

21

22

for (i=1; i < imax-1; ++i)

23

for (j=1; j < jmax-1; ++j) {

24 #pragma acc loop vector reduction(+:gosa) private(s0,ss)

25

for (k=1; k < kmax-1; ++k) {

26

s0 = a[0][i][j][k]*p[i+1][j][k]+a[1][i][j][k] ...;

27

ss = (s0 * a[3][i][j][k] - p[i][j][k])

28

* bnd[i][j][k];

29

gosa += ss*ss;

30

wrk2[i][j][k] = p[i][j][k] + omega * ss;

31

}

32

}

33 #pragma xmp loop (k, j, i) on t(k, j, i)

34 #pragma acc parallel loop collapse(2) gang vector_length(64) async

35

36

for (i=1; i < imax-1; ++i)

37

for (j=1; j < jmax-1; ++j) {

38 #pragma acc loop vector

for (k=1; k < kmax-1; ++k)

40

p[i][j][k] = wrk2[i][j][k];

41

42 #pragma acc wait

43 #pragma xmp reflect_do(p) acc

44 #pragma acc update host (gosa)

```

```

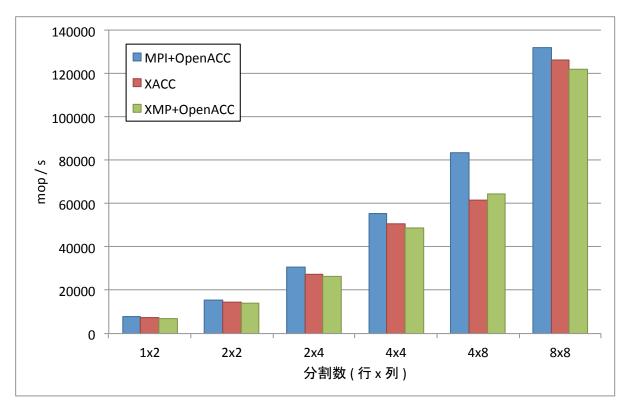

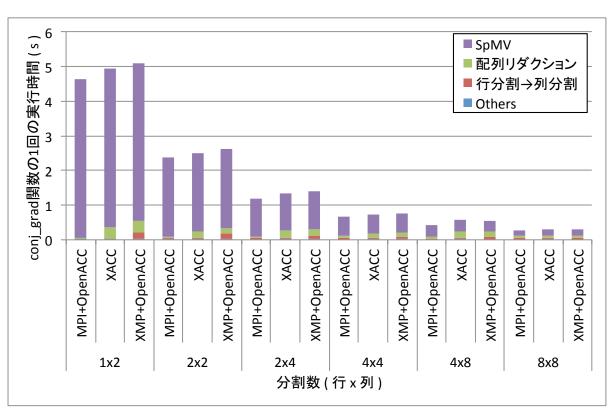

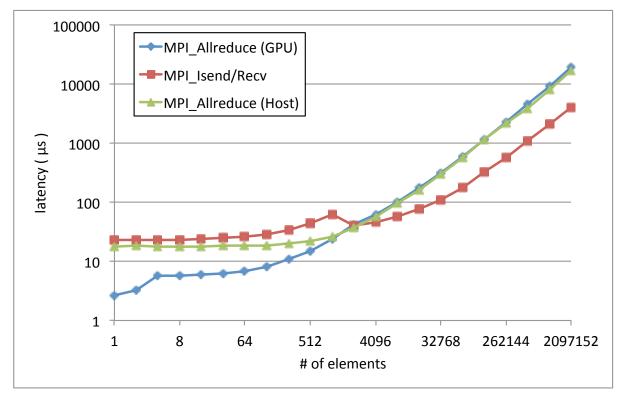

45 #pragma xmp reduction(+:gosa)