| 1  | Advanced solid-phase crystallization for high-hole mobility (450 cm <sup>2</sup> /Vs)                  |

|----|--------------------------------------------------------------------------------------------------------|

| 2  | Ge thin film on an insulator                                                                           |

| 3  |                                                                                                        |

| 4  | R. Yoshimine, K. Moto, T. Suemasu, and K. Toko*                                                        |

| 5  |                                                                                                        |

| 6  | Institute of Applied Physics, University of Tsukuba, 1-1-1 Tennodai, Tsukuba, Ibaraki 305-8573, Japan  |

| 7  |                                                                                                        |

| 8  | The hole mobility of the solid-phase-crystallized Ge layer is significantly improved by                |

| 9  | controlling the deposition temperature of Ge (50–200 $^{\circ}$ C) and the Ge thickness (50–500 nm)    |

| 10 | and by applying post annealing at 500 °C. The resulting hole mobility, 450 cm <sup>2</sup> /Vs, is the |

| 11 | highest value to date among that of semiconductor layers directly formed on glass. The                 |

| 12 | mechanism of the mobility enhancement is discussed from the perspective of three carrier               |

| 13 | scattering factors: grain boundary scattering, interface scattering, and impurity scattering.          |

| 14 | The high-hole mobility Ge layer formed by the simple fabrication process will be useful for            |

| 15 | high-speed thin-film transistors.                                                                      |

| 16 |                                                                                                        |

| 17 | * Author to whom correspondence should be addressed.                                                   |

| 18 | Electronic mail: toko@bk.tsukuba.ac.jp                                                                 |

| 19 |                                                                                                        |

Ge has attracted attention as the most promising candidate for post-Si material because it 20 has higher carrier mobility than Si and is compatible with conventional Si process. Effective 21 mobilities in Ge metal-oxide-semiconductor field-effect-transistors (MOSFETs) have exceeded 22 those in Si-MOSFETs thanks to the development of device technologies including gate stacks.<sup>1-</sup> 23 <sup>6)</sup> Ge on insulator (GOI) technology has been widely studied for lowering the fabrication cost 24 and improving the device performance of Ge-MOSFETs. Researchers have developed many 25 techniques for GOIs, such as mechanical transfer,<sup>7)</sup> oxidation-induced condensation,<sup>8-10)</sup> 26 epitaxial growth on Si on insulator,<sup>11,12</sup> and rapid-melting growth.<sup>13-16</sup> Although these 27 techniques are attractive for achieving high quality GOIs, the direct low-temperature formation 28 (< 600 °C) of Ge on arbitrary substrates is desired for lowering the process costs and expanding 29 the device application. Polycrystalline Ge (poly-Ge) thin films have been directly formed on 30 glass or plastic substrates at low temperatures using solid-phase crystallization (SPC),<sup>17–22</sup> laser 31 annealing,<sup>23-26)</sup> chemical vapor deposition,<sup>27,28)</sup> flash lamp annealing,<sup>29)</sup> and metal-induced 32 crystallization.<sup>30–34)</sup> The performance of the Ge thin film transistors (TFTs), however, has been 33 no match for that of Si-MOSFETs.<sup>20,21,26,29,34</sup>) This is attributed to the fact that the carrier 34 mobilities of the Ge layers are still low ( $\leq 200 \text{ cm}^2/\text{Vs}$ ). In addition, the Ge layers are highly p-35 doped (> 10<sup>17</sup> cm<sup>-3</sup>) because of point defects generating holes,<sup>35)</sup> which restricts device 36 application. To further improve Ge-TFTs, one needs to study not only device technology but 37 also crystallization techniques. 38

Toko *et al.* reported that post annealing (PA) at 500 °C is effective to reduce the point defects and then the hole concentration of SPC-Ge,<sup>17)</sup> which allows for the hole mobility of 140 cm<sup>2</sup>/Vs. On the other hand, Sadoh *et al.* reported that a thicker film allows for the higher hole mobility in SPC-GeSn.<sup>36)</sup> Very recently, we improved the hole mobility of SPC-Ge from 140 cm<sup>2</sup>/Vs to 340 cm<sup>2</sup>/Vs by preparing an amorphous Ge (a-Ge) precursor with heating the substrate.<sup>37)</sup> This hole mobility was the highest ever recorded for a thin film formed on insulators at temperatures below the melting point of Ge (937 °C). In this study, we investigated

the effects of both film thickness and PA on the SPC-Ge and broke the record with a hole

mobility of 450 cm<sup>2</sup>/Vs. The process temperature was 500 °C, making it possible to fabricate

devices on glass substrates.

In the experiment, the Ge precursors were deposited on SiO<sub>2</sub> glass substrates using the 49 Knudsen cell of a molecular beam deposition system (base pressure:  $5 \times 10^{-7}$  Pa). The 50 deposition rate was 1.0 nm/min where the sample substrate was not heated. The thickness of 51 the a-Ge layer, t, ranged from 50 to 500 nm. The substrate temperature during the deposition, 52  $T_{\rm d}$ , ranged from 50 to 200 °C. We note that  $T_{\rm d}$  spontaneously rises from room temperature to 53 50 °C without heating the substrate because of the heat radiation from the Knudsen cell. The 54 samples were then loaded into a conventional tube furnace in a N2 (99.9%) atmosphere and 55 annealed at 450 °C for 5 h to induce SPC. After that, we performed PA at 500 °C for 5 h to 56 enhance the electrical properties. To avoid sublimation of Ge by reaction with oxygen,<sup>17)</sup> PA 57 was performed in a lamp heating furnace in a high-purity Ar (99.9999%) atmosphere. 58

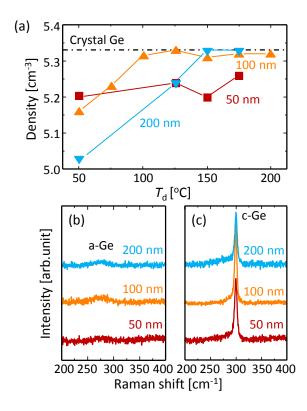

The as-deposited Ge layers, precursors for SPC, were evaluated using X-ray reflectivity 59 (XRR) and Raman spectroscopy (spot size 20 µm, wavelength 532 nm). Figure 1(a) shows that 60 the relationship between the film density of the precursor and  $T_d$  is different for different t. This 61 behavior can be explained as follows. As the migration of Ge atoms reaching the substrate 62 becomes more active, the film density increases and approaches the crystal. Since Ge is difficult 63 to adhere to SiO<sub>2</sub>,<sup>28)</sup> migration is active on the SiO<sub>2</sub> substrate. In contrast, because Ge easily 64 adhere to each other, migration is not active on the Ge film. Reflecting these phenomena, the 65 film density becomes higher as the film becomes thinner for  $T_d = 50$  °C (Fig. 1(a)). The higher 66  $T_{d}$ , the more the migration is promoted and the film density approaches the crystal, as seen for 67 t = 100 and 200 nm. Meanwhile, for t = 50 nm, the film density does not approach that of 68 crystalline Ge. This behavior is not completely understood, but possibly due to residual strain 69

in a thin film. In the case of the a-Ge film on a SiO<sub>2</sub> substrate, the tensile strain due to the film formation is more remarkable in the thinner film.<sup>38,39)</sup> We speculate that the effect of tensile strain is dominant for t = 50 nm, resulting in a constant density with respect to  $T_d$ . Figure 1(b) shows broad peaks near 275 cm<sup>-1</sup> corresponding to a-Ge, while Fig. 1(c) shows the sharp peaks near 300 cm<sup>-1</sup> corresponding to crystalline Ge for all samples. These results indicate that the crystalline Ge nuclei start to form in the a-Ge layer for  $T_d > 150$  °C.

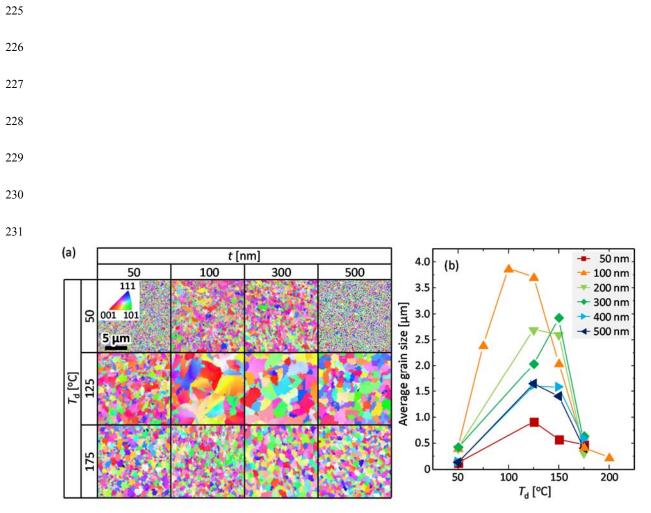

After annealing for SPC, the grown Ge layers were evaluated using electron 76 backscattering diffraction (EBSD) analysis. The EBSD images in Fig. 2(a) show that the grains 77 are randomly oriented and the grain size strongly depends on both  $T_d$  and t. Figure 2(b) shows 78 that there are optimum values for both  $T_d$  and t. For each t, the grain size expands with the 79 increase of  $T_{d}$ , then turns to shrink. As a result, the grain size reaches the highest value at around 80  $100 \le T_d \le 150$  °C. The behavior at  $T_d \ge 150$  °C can be explained by nucleation during 81 deposition of the precursor.<sup>37)</sup> On the other hand, the cause of the behavior at  $T_d \le 100$  °C is not 82 yet clear, but the process of nucleation and growth may depend on the atomic density of the a-83 Ge precursor. In order to verify the speculation, further studies to quantitatively determine the 84 activation energies and frequency factors for nucleation and growth are strongly needed. For t 85 = 50 nm, the grain size is relatively low over the whole  $T_d$ . For  $t \ge 100$  nm, the  $T_d$  for achieving 86 the maximum grain size value shifted to higher  $T_d$  with thicker t. Assuming that the grain size 87 depends on the precursor density, these behaviors are consistent with the results in Fig. 1(a). 88 For  $t \ge 100$  nm, the grain size became smaller with increasing *t*. This result likely reflects the 89 increase of bulk nucleation with the increasing  $t^{36,40)}$  As a result of these phenomena, the 90 maximum grain size value is 3.8  $\mu$ m for the sample with  $T_d = 100$  °C and t = 100 nm. 91

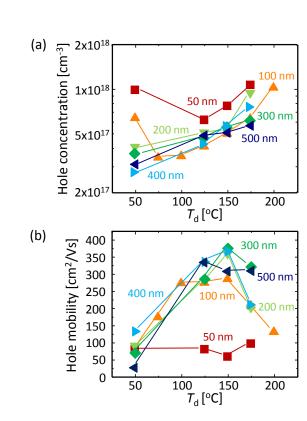

The electrical properties of the SPC-Ge layers before PA were evaluated using Hall effect measurements. All samples showed p-type conduction, similar to conventional non-doped poly-Ge.<sup>17,27,29,34</sup> This is because point defects in Ge provide shallow acceptor levels and then

generate holes at room temperature.<sup>35)</sup> There are three possible locations of point defects: the 95 interface between Ge and SiO<sub>2</sub>, Ge grain boundaries, and within Ge grains. Figure 3(a) shows 96 that hole concentration decreases with increasing t for  $T_d = 50$  °C. This behavior is the same as 97 the previous study on the SPC of GeSn<sup>36)</sup> and considered to arise from point defects located at 98 the interface between Ge and SiO<sub>2</sub>. For t = 50 and 100 nm, the hole concentrations are reduced 99 for  $T_d > 50$  °C. These make the *t* dependence of the hole concentration small for  $T_d > 50$  °C. 100 These behaviors suggest that the point defects located at the interface between Ge and SiO<sub>2</sub> are 101 reduced by the heating deposition of the precursor. For  $T_d > 50$  °C, the hole concentration 102 increases as  $T_d$  increases for each t. This behavior can be explained from the perspective of the 103 104 point defects located at grain boundaries and within grains. Since the grain boundary decreases as the grain size increases, point defects due to grain boundaries decrease. Reflecting the change 105 in grain size with respect to  $T_d$  (Fig. 2(b)), point defects due to grain boundaries are the lowest 106 at around  $T_d = 125$  °C. On the other hand, in crystal growth, as the growth rate increases, 107 vacancies are more easily taken into the grain. Since the growth rate increases with increasing 108  $T_{d}$ ,<sup>37)</sup> higher  $T_{d}$  likely provides more vacancies in the Ge grains. As a result of the balance 109 between the defects in the grain boundary and grain, the hole concentration behaves as shown 110 in Fig. 3(a) with respect to  $T_d$  (> 50 °C). 111

Figure 3(b) shows that the hole mobility of the SPC-Ge layer strongly depends on  $T_{d}$ , 112 except t = 50 nm. For  $t \ge 100$  nm, the high hole mobilities (> 250 cm<sup>2</sup>/Vs) at the high-density 113 amorphous regime ( $100 \le T_d \le 150$  °C) are attributed to both the large grain size and low 114 potential barrier height of grain boundaries.<sup>37)</sup> The thicker t tends to provide the higher hole 115 mobility despite the grain becoming smaller (Fig. 2(b)). These results suggest that the higher 116 hole mobility with the thicker Ge layer arises from the reduction of the interface scattering. The 117 highest hole mobility of the SPC-Ge layer before PA is 380 cm<sup>2</sup>/Vs obtained for  $T_d = 150 \text{ }^{\circ}\text{C}$ 118 and t = 300 nm. For this sample, the limiting factors of hole mobility were discussed as follows. 119

From the Matthiessen's rule, the hole mobility of the Ge layer  $\mu$  (= 380 cm<sup>2</sup>/Vs) is expressed by the following equation:

122 123

$$\frac{1}{\mu} = \frac{1}{\mu_{\rm P}} + \frac{1}{\mu_{\rm I}} + \frac{1}{\mu_{\rm others}} , \qquad (1)$$

where  $\mu_{P}$ ,  $\mu_{I}$ , and  $\mu_{others}$  are the hole mobilities limited by phonon scattering, impurity scattering, and the other scattering factors, respectively. According to the Irvin's curve,<sup>41</sup>  $\mu_{P}$  and  $\mu_{I}$  are determined to be 1900 cm<sup>2</sup>/Vs and 770 cm<sup>2</sup>/Vs, respectively. Therefore, from the equation (1),  $\mu_{others}$  is determined to be 1230 cm<sup>2</sup>/Vs. These results indicate that the hole mobility in this sample is dominantly limited by impurity scattering. Therefore, the reduction of the hole concertation is necessary to further improve the hole mobility.

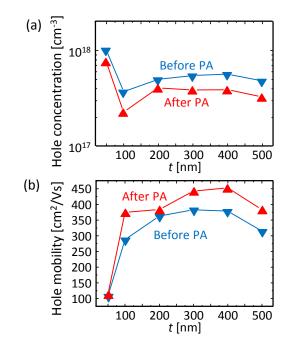

PA was performed for the samples of the highest hole mobility with each t. Figure 4(a)130 shows that the hole concentration decreases by approximately 30% for all samples. This result 131 suggests that Ge atoms migrated by thermal diffusion and passivated point defects, generating 132 holes, in the Ge layers. Figure 4(b) shows that the hole mobility increases for all samples. The 133 improvement of the hole mobility is up to  $100 \text{ cm}^2/\text{Vs}$ , though the improvement rate is relatively 134 small for t = 50 nm. The effect of PA on the electrical properties of 50-nm-thick SPC-Ge agrees 135 with the previous study.<sup>17)</sup> Considering the Irvin's curve and the equation (1), the hole mobility 136 for t = 50 nm is limited by grain boundary and/or interface scattering, whereas it is dominantly 137 138 limited by impurity scattering for t > 50 nm. These facts account for the t dependence of the PA effect (Fig. 4(b)). Thus, the reduction of the hole concentration by PA led to the hole mobility 139 of as high as 450 cm<sup>2</sup>/Vs for t = 400 nm. This Ge layer will be suitable for application to 140 junctionless type multiple gate FETs including FinFETs.<sup>6,29)</sup> 141

In conclusion, we further improved the hole mobility of the SPC-Ge layer by controlling  $T_d$  (50–200 °C) and *t* (50–500 nm) and applying PA (500 °C, 5 h). The resulting hole mobility, 450 cm<sup>2</sup>/Vs, is the highest value to date among that of semiconductor layers directly formed on glass. This achievement is likely attributed to the reduction of the carrier scattering factors: (i) the interface scattering was reduced by thickening SPC-Ge; (ii) the impurity scattering was reduced by PA passivating vacancy defects. These results open up the possibility for developing high-speed complimentary metal-oxide-semiconductor transistors leading to advanced systemin-displays and three-dimensional integrated circuits.

This work was financially supported by the JSPS KAKENHI (No. 26709019), the Iketani Science and Technology Foundation, and the Nanotech CUPAL. The authors are grateful to Prof. T. Sakurai at the University of Tsukuba for assistance with the Hall effect measurement. Some experiments were conducted at the International Center for Young Scientists in NIMS.

## 154 **REFERENCES**

- 155 1) A. Nayfeh, C. O. Chui, T. Yonehara, and K. C. Saraswat, IEEE Electron Device Lett. 26, 311 (2005).

- 156 2) D. P. Brunco, B. De Jaeger, G. Eneman, J. Mitard, G. Hellings, a. Satta, V. Terzieva, L. Souriau, F. E.

- 157 Leys, G. Pourtois, M. Houssa, G. Winderickx, E. Vrancken, S. Sioncke, K. Opsomer, G. Nicholas, M.

- 158 Caymax, a. Stesmans, J. Van Steenbergen, P. W. Mertens, M. Meuris, and M. M. Heyns, J. Electrochem.

- 159 Soc. **155**, H552 (2008).

- 160 3) R. Pillarisetty, Nature **479**, 324 (2011).

- 4) R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, IEEE Trans. Electron Devices 59, 335

(2012).

- 163 5) K. Yamamoto, T. Sada, D. Wang, and H. Nakashima, Appl. Phys. Lett. 103, 122106 (2013).

- 164 6) W. Mizubayashi, S. Noda, Y. Ishikawa, T. Nishi, A. Kikuchi, H. Ota, P.-H. Su, Y. Li, S. Samukawa, and

- 165 K. Endo, Appl. Phys. Express **10**, 26501 (2017).

- 166 7) G. Taraschi, A. J. Pitera, and E. A. Fitzgerald, Solid. State. Electron. 48, 1297 (2004).

- 167 8) T. Maeda, K. Ikeda, S. Nakaharai, T. Tezuka, N. Sugiyama, Y. Moriyama, and S. Takagi, Thin Solid

168 Films **508**, 346 (2006).

- 9) N. Hirashita, Y. Moriyama, S. Nakaharai, T. Irisawa, N. Sugiyama, and S. Takagi, Appl. Phys. Express

1, 1014011 (2008).

- 171 10) H. Yang, D. Wang, and H. Nakashima, Appl. Phys. Lett. 95, 122103 (2009).

- 12) O. Nakatsuka, N. Tsutsui, Y. Shimura, S. Takeuchi, A. Sakai, and S. Zaima, Jpn. J. Appl. Phys. 49,

04DA10 (2010).

- 176 13) Y. Liu, M. D. Deal, and J. D. Plummer, Appl. Phys. Lett. 84, 2563 (2004).

- 177 14) S. Hu, P. W. Leu, A. F. Marshall, and P. C. McIntyre, Nat. Nanotechnol. 4, 649 (2009).

- 178 15) K. Toko, Y. Ohta, T. Tanaka, T. Sadoh, and M. Miyao, Appl. Phys. Lett. 99, 32103 (2011).

- 16) C. G. Littlejohns, M. Nedeljkovic, C. F. Mallinson, J. F. Watts, G. Z. Mashanovich, G. T. Reed, and F.

Y. Gardes, Sci. Rep. 5, 8288 (2015).

- 181 17) K. Toko, I. Nakao, T. Sadoh, T. Noguchi, and M. Miyao, Solid. State. Electron. 53, 1159 (2009).

- 182 18) C.-Y. Tsao, J. Huang, X. Hao, P. Campbell, and M. A. Green, Sol. Energy Mater. Sol. Cells 95, 981

183 (2011).

- 184 19) H.-W. Jung, W.-S. Jung, H.-Y. Yu, and J.-H. Park, J. Alloys Compd. 561, 231 (2013).

- 185 20) T. Sadoh, H. Kamizuru, A. Kenjo, and M. Miyao, Appl. Phys. Lett. 89, 192114 (2006).

- 186 21) S. Kabuyanagi, T. Nishimura, K. Nagashio, and A. Toriumi, Thin Solid Films 557, 334 (2014).

- W. Takeuchi, N. Taoka, M. Kurosawa, M. Sakashita, O. Nakatsuka, and S. Zaima, Appl. Phys. Lett. 107,

22103 (2015).

- 189 23) H. Watakabe, T. Sameshima, H. Kanno, and M. Miyao, Thin Solid Films 508, 315 (2006).

- 190 24) W. Yeh, H. Chen, H. Huang, C. Hsiao, and J. Jeng, Appl. Phys. Lett. 93, 94103 (2008).

- 191 25) K. Sakaike, S. Higashi, H. Murakami, and S. Miyazaki, Thin Solid Films **516**, 3595 (2008).

- 26) C.-Y. Liao, C.-Y. Huang, M.-H. Huang, W.-H. Huang, C.-H. Shen, J.-M. Shieh, and H.-C. Cheng, Jpn.

J. Appl. Phys. 56, 06GF08 (2017).

- 194 27) T. Matsui, M. Kondo, K. Ogata, T. Ozawa, and M. Isomura, Appl. Phys. Lett. 89, 142115 (2006).

- 195 28) M. Tada, J.-H. Park, D. Kuzum, G. Thareja, J. R. Jain, Y. Nishi, and K. C. Saraswat, J. Electrochem.

196 Soc. 157, H371 (2010).

- 197 29) K. Usuda, Y. Kamata, Y. Kamimuta, T. Mori, M. Koike, and T. Tezuka, Appl. Phys. Express 7, 56501

198 (2014).

- 199 30) Z. Wang, L. P. H. Jeurgens, W. Sigle, and E. J. Mittemeijer, Phys. Rev. Lett. 115, 016102 (2015).

- 200 31) S. Hu, A. F. Marshall, and P. C. McIntyre, Appl. Phys. Lett. 97, 82104 (2010).

- 201 32) K. Toko, R. Numata, N. Oya, N. Fukata, N. Usami, and T. Suemasu, Appl. Phys. Lett. 104, 22106 (2014).

- 202 33) J.-H. Park, K. Kasahara, K. Hamaya, M. Miyao, and T. Sadoh, Appl. Phys. Lett. 104, 252110 (2014).

- 203 34) K. Kasahara, Y. Nagatomi, K. Yamamoto, H. Higashi, M. Nakano, S. Yamada, D. Wang, H. Nakashima,

- and K. Hamaya, Appl. Phys. Lett. **107**, 142102 (2015).

- 205 35) H. Haesslein, R. Sielemann, and C. Zistl, Phys. Rev. Lett. 80, 2626 (1998).

- 206 36) T. Sadoh, Y. Kai, R. Matsumura, K. Moto, and M. Miyao, Appl. Phys. Lett. 109, 232106 (2016).

- 207 37) K. Toko, R. Yoshimine, K. Moto, and T. Suemasu, Sci. Rep. 7, 16981 (2017).

- 208 38) J. A. Floro, P. G. Kotula, and S. C. Seel, Phys. Rev. Lett. **91**, 090101 (2003).

- 209 39) Z. Wang, D. Flötotto, and E.J. Mittemeijer, J. Appl. Phys. 121, 95307 (2017).

- 40) P. Germain, K. Zellama, S. Squelard, J. C. Bourgoin, and A. Gheorghiu, J. Appl. Phys. 50, 6986 (1979).

- 41) J.C. Irvin and S.M. Sze, Solid State Electron. 11, 599 (1968).

FIG. 1. Characteristics of the as-deposited Ge layers before SPC obtained by XRR and Raman measurement. (a) Density of precursor Ge as a function of  $T_d$  for t = 50, 100, and 200 nm. The data for crystalline Ge are shown by the dotted line. (b),(c) Raman spectra for the samples with  $T_d =$  (b) 150 °C and (c) 200 °C.

232

FIG. 2. Grain size of the SPC-Ge layers. (a) EBSD images of SPC-Ge summarized as the matrix composed of  $T_d$  (50, 125, and 175 °C) and t (50, 100, 300, and 500 nm). The colors indicate the crystal orientation, according to the inserted color key. (b)  $T_d$  dependence of the average grain size calculated from the EBSD images for t = 50-500 nm.

FIG. 3. Electrical properties of the SPC-Ge layers before PA for t = 50-500 nm, obtained by Hall effect measurement with the van der Pauw method. (a) Hole mobility and (b) hole concentration as a function of  $T_{d}$ .

**FIG. 4.** Electrical properties of the SPC-Ge layers for t = 50-500 nm before and after PA at

$500 \,^{\circ}\text{C}$  for 5 h. (a) Hole mobility and (b) hole concentration as a function of t.