## **OPEN**

Received: 28 July 2017 Accepted: 23 November 2017 Published online: 05 December 2017

# High-hole mobility polycrystalline Ge on an insulator formed by controlling precursor atomic density for solid-phase crystallization

Kaoru Toko, Ryota Yoshimine, Kenta Moto & Takashi Suemasu

High-carrier mobility semiconductors on insulators are essential for fabricating advanced thin-film transistors, allowing for three-dimensional integrated circuits or high-performance mobile terminals. We investigate the low-temperature (375–450 °C) solid-phase crystallization (SPC) of Ge on a glass substrate, focusing on the precursor conditions. The substrate temperature during the precursor deposition,  $T_{\rm dr}$ , ranged from 50 to 200 °C. According to the atomic density of the precursor and the  $T_{\rm dr}$  dependent SPC properties, the precursor conditions were determined by three regimes: the low-density regime ( $T_{\rm d} < 100$  °C), high-density regime ( $T_{\rm dr} < 125$  °C), and nucleation regime ( $T_{\rm dr} > 125$  °C). The use of the precursor in the narrow high-density regime enabled us to form SPC-Ge with a hole mobility of 340 cm²/Vs, the highest value among semiconductor thin films grown on insulators at low temperature ( $T_{\rm dr} > 100$  °C). The origins of the high hole mobility were determined to be both a large grain size (5 µm) and a low energy barrier height (6.4 meV) for the grain boundary. The findings from and knowledge gained in this study, that is, the influence of the precursor conditions on subsequent crystal growth, will be universal and applicable to various materials.

Germanium has been proposed as a major candidate for next-generation electronic devices because of its high carrier mobility and good compatibility with Si<sup>1-3</sup>. In particular, the hole mobility of Ge is the highest among semiconductor materials, which can be used to realize high-performance complementary metal-oxide-semiconductor (CMOS) devices<sup>3</sup>. The developments of gate stacks and source/drain junction technologies have led to high effective mobilities in Ge metal-oxide-semiconductor field-effect-transistors (MOSFETs) exceeding those in Si-MOSFETs<sup>4-7</sup>. For expanding the application of Ge-MOSFETs in system-in-displays (system-on-panels) or three-dimensional integrated circuits, Ge on insulator (GOI) technology has been developed using mechanical transfer<sup>8</sup>, oxidation-induced condensation<sup>9,10</sup>, epitaxial growth on Si on insulator (SOI)<sup>11,12</sup>, and rapid-melting growth<sup>13-16</sup>. To avoid thermal damage to the substrates and to lower the process costs, the low-temperature formation (<600 °C) of GOI is necessary. Polycrystalline Ge (poly-Ge) thin films have been directly formed on glass or plastic substrates at low temperatures using solid-phase crystallization (SPC)<sup>17-21</sup>, laser annealing<sup>22-24</sup>, chemical vapor deposition (CVD)<sup>25,26</sup>, flash lamp annealing (FLA)<sup>27</sup>, and metal-induced crystallization (MIC)<sup>28-32</sup>. The use of these techniques has allowed researchers to fabricate Ge thin-film transistors (TFTs) via all-low-temperature processes<sup>20,21,27,32</sup>. The performance of the Ge-TFTs, however, has been no match for that of Si-MOSFETs. To further improve Ge-TFTs, one needs to study not only device technology but also crystallization techniques.

In 2009, we demonstrated a hole mobility of  $140 \text{ cm}^2/\text{Vs}$  for poly-Ge on glass formed by two-step SPC of amorphous (a–) Ge at  $425 \,^{\circ}\text{C}$  followed by  $500 \,^{\circ}\text{C}^{17}$ . In the last couple of years, the highest hole mobility has been updated frequently: FLA has achieved  $200 \, \text{cm}^2/\text{Vs}^{27}$ , followed by Au-induced crystallization achieving  $160-210 \, \text{cm}^2/\text{Vs}^{31,32}$ . On the other hand, incorporating Sn in Ge has been found to be effective for enhancing the hole mobility  $^{33-35}$ . The SPC of a-GeSn has achieved a hole mobility of  $130 \, \text{cm}^2/\text{Vs}^{34}$ , which was then enhanced to  $320 \, \text{cm}^2/\text{Vs}$  by controlling the thickness of the a-GeSn layer  $^{35}$ . The present study demonstrates a simple method to

Institute of Applied Physics, University of Tsukuba, 1-1-1 Tennodai, Tsukuba, Ibaraki, 305-8573, Japan. Correspondence and requests for materials should be addressed to K.T. (email: toko@bk.tsukuba.ac.jp)

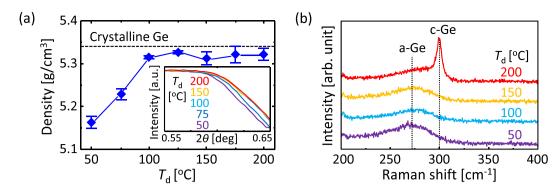

**Figure 1.** Characteristics of the as-deposited Ge layers. (a) Density of Ge as a function of  $T_d$ . The data for crystalline Ge is shown by the dotted line. The inset shows the raw XRR patterns, focusing on the area reflecting the density. (b) Raman spectra for samples with  $T_d = 50$ , 100, 150, and 200 °C.

achieve pure poly-Ge with a hole mobility of  $340\,\mathrm{cm^2/Vs}$  by controlling the atomic density of an a-Ge precursor. This hole mobility is the highest ever recorded for a semiconductor thin film including Ge, Si, compound, oxide, and organic materials formed on insulators at temperatures below  $900\,\mathrm{^{\circ}C}$ .

#### Results

The as-deposited Ge layers, precursors for SPC, were evaluated by X-ray reflectivity (XRR) and Raman spectroscopy. Figure 1a shows that the density of the Ge layer approaches that of crystalline Ge with increasing the deposition temperature  $T_{\rm d}$  and becomes nearly saturated at  $T_{\rm d} > 100\,^{\circ}$ C. The density of the Ge layer for  $T_{\rm d} = 50\,^{\circ}$ C almost agrees with the data from previous study on the a-Ge layer deposited without heating the substrate<sup>36</sup>. Figure 1b shows that samples with  $T_{\rm d} = 50$ , 100, and 150 °C exhibit broad peaks near 270 cm<sup>-1</sup>, corresponding to a-Ge<sup>17,18</sup>. The sample with  $T_{\rm d} = 200\,^{\circ}$ C exhibits a sharp peak near 300 cm<sup>-1</sup>, corresponding to crystalline Ge-Ge bonding<sup>17,18</sup>, in addition to a broad peak near 270 cm<sup>-1</sup>. This result indicates that the sample with  $T_{\rm d} = 200\,^{\circ}$ C includes both crystalline and amorphous states. The optical studies suggest the following: (i) higher  $T_{\rm d}$  provides denser a-Ge; and (ii) crystalline Ge nuclei start to form in the a-Ge layer at  $T_{\rm d} > 150\,^{\circ}$ C.

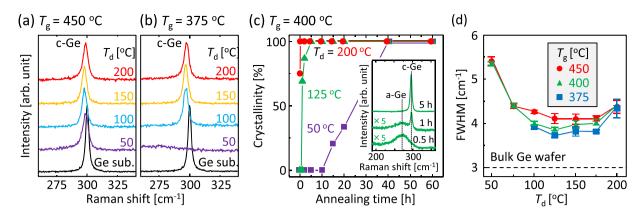

The samples were then annealed to induce SPC, where the growth temperature  $T_{\sigma}$  ranged from 375 to 450 °C. The samples were evaluated by Raman spectroscopy. Figure 2a shows that all samples annealed at 450 °C for 5 h exhibited sharp peaks corresponding to crystal Ge. These peaks are almost symmetrical, suggesting that the Ge layers are completely crystallized. All peaks shifted to lower wavenumbers than that of a bulk Ge substrate, originating from the tensile strain. Generally, as-deposited amorphous semiconductor layers have stress caused by nanovoids or roughened surfaces<sup>37,38</sup>. This should affect the subsequent SPC; however, the initial stress is likely released during the crystallization of a-Ge. We therefore consider the tensile strain in the resulting Ge layers originates from the difference in the thermal expansion coefficients between Ge and the SiO<sub>2</sub> substrate<sup>17,23</sup>. We note that samples with  $T_d = 100$  and 150 °C exhibit larger tensile strains than other samples. This behaviour is likely caused by the large grain growth for samples with  $T_d = 100$  and 150 °C, as revealed in Fig. 3. As representatively shown in Fig. 2b, annealing at 375 °C for 140 h crystallized the samples with  $T_d \ge 100$  °C, but not those with  $T_{\rm d} \le 75\,^{\circ}$ C. We examined the  $T_{\rm d}$  dependence of the growth rate from the annealing-time evolution of the Raman spectra, representatively shown in the insertion in Fig. 2c. The crystallinity of the Ge layer was defined as the ratio of the Raman peak intensity of c-Ge to that of a-Ge. Figure 2c shows that the annealing time for completing crystallization is dramatically reduced by increasing  $T_d$ . This means that the higher  $T_d$  provides a higher growth rate, accounting for the results in Fig. 2b. The full width at half maximum (FWHM) of the Ge-Ge peaks were evaluated from the Raman spectra and are summarized in Fig. 2d. The FWHM depends on both  $T_{\rm d}$  and  $T_{\rm g}$ ; the FWHM is a minimum at approximately  $T_{\rm d} = 125\,^{\circ}\text{C}$  and decreases with decreasing  $T_{\rm g}$ . The sample with  $T_{\rm d} = 125\,^{\circ}$  $^{\circ}$ C and  $T_{g} = 375 \,^{\circ}$ C exhibited the minimum FWHM value (3.7 cm $^{-1}$ ). This value is close to that of a bulk-Ge wafer (3.0 cm<sup>-1</sup>) and the smallest among poly-Ge formed at low temperatures (<600 °C)<sup>17,18,23,30</sup>. This indicates the high crystal quality of the Ge layer obtained in this study.

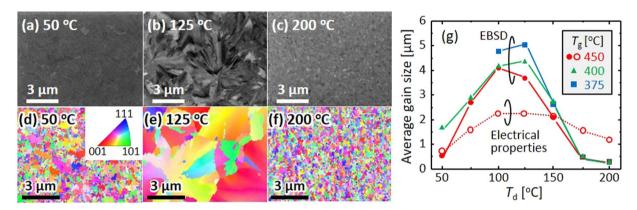

The grain size of the resulting poly-Ge layers was evaluated using scanning electron microscopy (SEM) and electron backscattering diffraction (EBSD) analyses. The SEM images in Fig. 3a–c show some contrast, especially for  $T_{\rm d}=125\,^{\circ}{\rm C}$ . Atomic force microscopy (AFM) revealed that the surface of the sample with  $T_{\rm d}=125\,^{\circ}{\rm C}$  was flat (root mean square value: 0.5 nm). This suggests that the contrast in SEM corresponds to crystal orientation visualized by the electron channelling effect for high-quality crystals. Figure 3d–f show that the crystal orientation is almost random for all samples. Both the SEM and EBSD images indicate that the sample with  $T_{\rm d}=125\,^{\circ}{\rm C}$  exhibits grains that are one order of magnitude larger than those of the other samples. Figure 3g shows that the grain size, as determined by the EBSD analyses, depends on both  $T_{\rm d}$  and  $T_{\rm g}$ . The grain size is a maximum at approximately  $T_{\rm d}=125\,^{\circ}{\rm C}$ . The lower  $T_{\rm g}$  provides a larger grain size, which agrees with the conventional SPC with<sup>30</sup> and without catalytic metals. The dependence of the grain size on  $T_{\rm d}$  and  $T_{\rm g}$  accounts for the results of the Raman measurements shown in Fig. 2d. The sample with  $T_{\rm d}=125\,^{\circ}{\rm C}$  and  $T_{\rm g}=375\,^{\circ}{\rm C}$  exhibited a grain size of 5 µm, which is the largest among poly-Ge formed by SPC<sup>17,18</sup>.

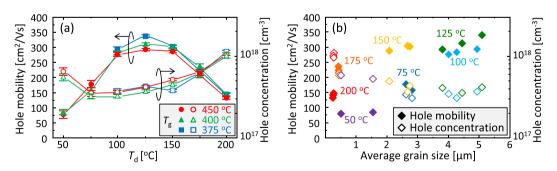

The electrical properties of the resulting poly-Ge layers were evaluated by Hall effect measurements. All samples showed p-type conduction, similar to conventional non-doped poly-Ge<sup>17,25,27,32</sup>. This is because dangling bonds in Ge provide shallow acceptor levels and then generate holes at room temperature<sup>39</sup>. Figure 4a shows

**Figure 2.** Raman spectroscopy study of the Ge layers. (**a,b**) Raman spectra of the sample annealed at (**a**)  $450\,^{\circ}$ C for  $5\,h$  and (**b**)  $375\,^{\circ}$ C for  $140\,h$ . The spectra for a bulk-Ge wafer are shown for comparison. (**c**) Crystallinity for samples with  $T_d = 50\,^{\circ}$ C,  $125\,^{\circ}$ C, and  $200\,^{\circ}$ C as a function of annealing time, determined by the annealing-time evolution of Raman spectra representatively shown in the insertion. (**d**) FWHMs of the Ge-Ge peaks for samples with  $T_g = 375\,^{\circ}$ C,  $400\,^{\circ}$ C, and  $450\,^{\circ}$ C as a function of  $T_d$ . The data for a bulk-Ge wafer is shown by the dotted line.

**Figure 3.** Grain size of the poly-Ge layers. (**a**–**c**) SEM and (**d**–**f**) EBSD images of the samples annealed at 450 °C with  $T_{\rm d}$  = (**a**,**d**) 50 °C (**b**,**e**) 125 °C, and (**c**,**f**) 200 °C. The coloration in the EBSD images indicates the crystal orientation according to the legend inserted in (**d**). (**g**) Average grain size determined by the EBSD analyses for samples with  $T_{\rm g}$  = 375 °C, 400 °C, and 450 °C as a function of  $T_{\rm d}$ . The data determined by the electrical properties of samples with  $T_{\rm g}$  = 450 °C are also shown.

**Figure 4.** Electrical properties of the poly-Ge layers. Hole mobility and hole concentration for samples with  $T_{\rm g} = 375\,^{\circ}\text{C}$ , 400  $^{\circ}\text{C}$ , and 450  $^{\circ}\text{C}$  as a function of (a)  $T_{\rm d}$  and (b) average grain size.

that the hole concentration depends on  $T_{\rm d}$  and is a minimum at approximately  $T_{\rm d}$  = 75–100 °C. Figure 4a also shows that the hole mobility depends on both  $T_{\rm d}$  and  $T_{\rm g}$ , as with the grain size and FWHMs of the Raman peaks. The hole mobility is a maximum at  $T_{\rm d}$  = 125 °C and increases with decreasing  $T_{\rm g}$ . The sample with  $T_{\rm d}$  = 125 °C and  $T_{\rm g}$  = 375 °C exhibited the highest hole mobility, 340 cm²/Vs. Figure 4b shows that the hole concentration decreases with increasing grain size, suggesting that dangling bonds in grain boundaries generate holes similar to those in crystal grains  $^{6,10,17,39}$ . Figure 4b also shows that the hole mobility tends to increase with increasing grain

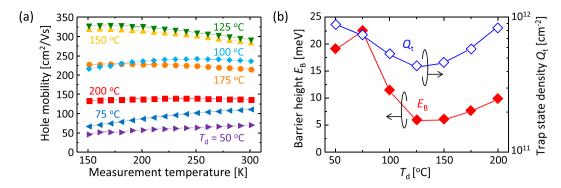

**Figure 5.** Characterization of grain boundaries in the poly-Ge layers. (a) Measurement temperature dependence of the hole mobility for samples with  $T_{\rm d}$  = 50–200 °C and  $T_{\rm g}$  = 450 °C. (b) Energy barrier height  $E_{\rm B}$  and trap state density  $Q_{\rm t}$  of grain boundaries for the samples with  $T_{\rm g}$  = 450 °C as a function of  $T_{\rm d}$ .

size in the same  $T_{\rm d}$ , but overall, the hole mobility depends on  $T_{\rm d}$  rather than grain size. For example, the sample with  $T_{\rm d} = 175\,^{\circ}{\rm C}$  exhibited higher hole mobility than the sample with  $T_{\rm d} = 75\,^{\circ}{\rm C}$ , whereas the grain size shows an opposing trend. This behaviour suggests that the hole mobility is not determined only by grain size, but also by another factor.

According to the carrier conduction model in polycrystalline semiconductors proposed by Seto<sup>40</sup>, the carrier mobility limited by grain boundary scattering can be determined using the following equation:

$$\mu = \frac{Lq}{\sqrt{2\pi m^* kT}} \exp\left(-\frac{E_B}{kT}\right),\tag{1}$$

where  $\mu$  is the carrier mobility,  $E_{\rm B}$  is the energy barrier height of the grain boundary, T is the absolute temperature, L is the grain size,  $m^*$  is the effective mass, and k is the Boltzmann constant. Figure 5a shows that the T dependence of the hole mobility varies with  $T_{\rm d}$ , indicating the difference in  $E_{\rm B}^{40}$ . The Arrhenius plot of  $\mu T^{1/2}$  exhibited downward-sloping straight lines for all samples. This behaviour indicates that the carrier conduction in the poly-Ge layers is limited by grain boundary scattering. Figure 5b shows that  $E_{\rm B}$ , determined by the slopes of  $\mu T^{1/2}$ , depends on  $T_{\rm d}$ . For  $T_{\rm d} = 125\,^{\circ}{\rm C}$ ,  $E_{\rm B}$  exhibits the minimum value, 6.4 meV. The trap state density  $Q_{\rm t}$  in the grain boundary can be determined using the following equation<sup>40</sup>:

$$Q_{\rm t} = \frac{\sqrt{8\varepsilon NE_B}}{q},\tag{2}$$

where N is the carrier concentration,  $\varepsilon$  is the dielectric permittivity, and q is the elementary charge. Figure 5b shows that  $Q_t$  depends on  $T_d$ . The  $E_B$  and  $Q_t$  for  $T_d = 50$  °C nearly agree with those of conventional poly-Ge whose precursors were formed without heating the substrates <sup>17,22,34</sup>. For  $T_d = 125$  °C,  $Q_t$  exhibits the minimum value,  $4.4 \times 10^{11}$  cm<sup>-2</sup>. From the equations (1) and (2),  $\mu$  can be expressed by the following equation:

$$\mu = \frac{Lq}{\sqrt{2\pi m^* kT}} \exp\left(-\frac{q^2 Q_t^2}{8\varepsilon N kT}\right). \tag{3}$$

The equation (3) indicates that  $Q_{\rm t}$  has greater influence on  $\mu$  than L. Reflecting that, the  $T_{\rm d}$  dependence of the hole mobility completely agrees with that of  $Q_{\rm t}$  (Figs 4a and 5b). On the other hand, we determined L from the electrical properties of the sample with  $T_{\rm g}=450\,^{\circ}{\rm C}$  by using the equation. The results are plotted in Fig. 3g, showing that the data from the electrical properties exhibits the same behaviour as that from the EBSD measurement. These results indicate that  $\mu$  depends on not only  $Q_{\rm t}$  but also L. We therefore conclude that the high hole mobility (340 cm²/Vs for  $T_{\rm d}=125\,^{\circ}{\rm C}$ ) observed in this study is due to both the large L and low  $Q_{\rm t}$ .

#### Discussion

The crystal quality and electrical properties of the poly-Ge layer formed by SPC varied with the deposition temperature,  $T_{\rm d}$ , of the precursor Ge layer. According to Fig. 1 and the  $T_{\rm d}$  dependent SPC properties, the precursor conditions can be determined by three regimes: the low-density regime ( $T_{\rm d} < 100\,^{\circ}{\rm C}$ ), high-density regime ( $100 \le T_{\rm d} \le 125\,^{\circ}{\rm C}$ ), and nucleation regime ( $T_{\rm d} > 125\,^{\circ}{\rm C}$ ). In the low-density regime, the atomic distance in a-Ge is longer than that of crystal Ge. Therefore, the lateral growth rate of Ge nuclei during SPC should be low considering that SPC progresses by the migration of atoms during annealing. This speculation is consistent with the results on the growth rate shown in Fig. 2c. The low lateral growth rate result in poly-Ge with small grains because the grain size in SPC is determined by the balance between nucleation and lateral growth. When the atomic density of the a-Ge precursor is lower than that of crystalline Ge, the volume of the resulting SPC-Ge is smaller than that of the precursor. The volume change may cause the voids (dangling bonds) at the grain boundary. This leads to the high trap state density  $Q_{\rm f}$  at grain boundaries and then lowers the hole mobility.

The nucleation regime should be  $T_d > 125$  °C considering the behaviours of the grain size and electrical properties of the SPC-Ge. Although the sample with  $T_d = 150$  °C exhibits no Raman peak (Fig. 1b), the Ge

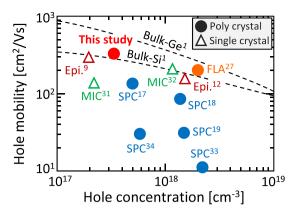

**Figure 6.** Comparison of the hole mobility and hole concentration of GOIs. The growth method and the reference number are shown near each symbol. The data for single-crystal bulk Si and Ge are shown by dotted lines.

precursor layer may contain nuclei which are smaller or less than the detection limit of the Raman measurement. In the high-density regime, the atomic distance in the a-Ge precursor is close to that of crystalline Ge. The growth rate of Ge nuclei during SPC is therefore high, resulting in poly-Ge with large grains. The difference in the atomic density between the a-Ge precursor and resulting poly-Ge is small, leading to low  $Q_t$ . The hole mobility is therefore high in the high-density regime. In the nucleation regime, the as-deposited Ge layer has dense crystalline Ge nuclei, which is common in vapor deposition  $^{25,26}$ . Because SPC starts from the nuclei, the poly-Ge results in small grains. The nuclei perturb the atomic distance of the a-Ge region in the precursor, leading to high  $Q_t$ . The hole mobility is therefore low in the nucleation regime. Thus, choosing a narrow window for  $T_d$  allows us to form the high-density amorphous precursor, which is essential for realizing high-quality poly-Ge. In previous studies, the effects of the deposition temperature of a-Si on the subsequent SPC were examined; however, the crystal quality and electrical properties were not improved dramatically  $^{41}$ . This is probably because the substrate temperature was not set at the high-density regime but the nucleation regime considering that the grain size decreased with increasing  $T_d^{41}$ . We consider that the dramatic improvements of crystal quality and electrical properties occur for any materials as long as one can set the density of the amorphous precursors to the narrow high-density regime.

As shown in Fig. 6, the hole concentration is the lowest among poly-Ge, indicating that the Ge layer contains relatively few defects. The hole mobility of  $340\,\mathrm{cm^2/Vs}$  obtained in this study is the highest value among the Ge layers formed on insulating substrates at temperatures below the melting point of Ge (937 °C). The hole mobility is even higher than that of single-crystal Ge layers epitaxially grown from single-crystal Si templates<sup>9,12</sup>. Moreover, the electrical properties of the present poly-Ge layer exceed those of bulk Si. These results mean that single-crystal wafers are no longer necessary for fabricating a high-hole mobility semiconductor thin film.

In conclusion, the condition of the precursor for SPC dramatically influences the crystal quality and electrical properties in the resulting poly-Ge layer. The a-Ge precursor prepared at 125 °C led to a large-grained (5  $\mu$ m) poly-Ge layer whose grain boundary exhibited a low energy barrier height (6.4 meV) because of the low trap state density (4.4  $\times$  10<sup>11</sup> cm<sup>-2</sup>). This allowed for a hole mobility of 340 cm<sup>2</sup>/Vs, the highest value among semiconductor layers formed on insulators at temperatures below 900 °C. The growth temperature was as low as 375 °C, allowing for Ge devices on plastic substrates. These results open up the possibility for developing advanced CMOS devices as well as system-in-displays and three-dimensional integrated circuits. The findings from and knowledge gained in this study will be universal and applicable to various materials.

## **Methods**

**Sample preparation.** The Ge precursors were deposited on SiO<sub>2</sub> glass substrates using the Knudsen cell of a molecular beam deposition system (base pressure:  $5 \times 10^{-7}$  Pa). The deposition rate was 1.0 nm/min where the sample substrate was not heated. The deposition time was 100 min. The Ge source, manufactured by Furuuchi Chemical Corporation, had a purity of 99.999%. The substrate temperature during the deposition,  $T_{\rm d}$ , ranged from 50 to 200 °C. We note that  $T_{\rm d}$  spontaneously rises from room temperature to 50 °C without heating the substrate because of the heat propagation from the Knudsen cell. The samples were then loaded into a conventional tube furnace in a  $N_2$  atmosphere and annealed at 375 °C for 140 h, 400 °C for 40 h, and 450 °C for 5 h to induce SPC.

**Material characterization.** The XRR was performed using a Rigaku SmartLab. The Raman spectroscopy was performed using a Nanophoton RAMANplus, where the laser wavelength was 532 nm and the spot size was 20 μm. The SEM and EBSD analyses were performed using a JEOL JSM-7001F with a TSL OIM analysis attachment. The AFM was performed using a Shimadzu SPM-9600. The Hall effect measurement with the Van der Pauw method was performed using a Bio-Rad HL5500PC. The hole mobility and hole concentration were averaged over five measurements for each sample.

#### References

- 1. Irvin, J. C. & Sze, S. M. Resistivity, mobility and impurity levels in GaAs, Ge, and Si at 300 degrees. Solid. State. Electron. 11, 599–602 (1968).

- 2. Nayfeh, A., Chui, C. O., Yonehara, T. & Saraswat, K. C. Fabrication of high-quality p-MOSFET in Ge Grown heteroepitaxially on Si. *IEEE Electron Device Lett.* 26, 311–313 (2005).

- 3. Brunco, D. P. et al. Germanium MOSFET Devices: Advances in Materials Understanding, Process Development, and Electrical Performance. I. Electrochem. Soc. 155, H552 (2008).

- 4. Pillarisetty, R. Academic and industry research progress in germanium nanodevices. Nature 479, 324–328 (2011).

- 5. Zhang, R., Iwasaki, T., Taoka, N., Takenaka, M. & Takagi, S. High-Mobility Ge pMOSFET With 1-nm EOT Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge Gate Stack Fabricated by Plasma Post Oxidation. *IEEE Trans. Electron Devices* **59**, 335–341 (2012).

- Jung, W.-S., Park, J.-H., Nainani, A., Nam, D. & Saraswat, K. C. Fluorine passivation of vacancy defects in bulk germanium for Ge metal-oxide-semiconductor field-effect transistor application. Appl. Phys. Lett. 101, 72104 (2012).

- 7. Yamamoto, K., Sada, T., Wang, D. & Nakashima, H. Dramatic enhancement of low electric-field hole mobility in metal source/drain Ge p-channel metal-oxide-semiconductor field-effect transistors by introduction of Al and Hf into SiO<sub>2</sub>/GeO<sub>2</sub> gate stack. *Appl. Phys. Lett.* **103**, 122106 (2013).

- 8. Taraschi, G., Pitera, A. J. & Fitzgerald, E. A. Strained Si, SiGe, and Ge on-insulator: review of wafer bonding fabrication techniques. Solid. State. Electron. 48, 1297–1305 (2004).

- 9. Hirashita, N. et al. Deformation induced holes in Ge-rich SiGe-on-insulator and Ge-on-insulator substrates fabricated by Ge condensation process. Appl. Phys. Express 1, 1014011–1014013 (2008).

- Yang, H., Wang, D. & Nakashima, H. Evidence for existence of deep acceptor levels in SiGe-on-insulator substrate fabricated using Ge condensation technique. Appl. Phys. Lett. 95, 122103 (2009).

- 11. Cammilleri, V. D. et al. Lateral epitaxial growth of germanium on silicon oxide. Appl. Phys. Lett. 93, 43110 (2008).

- 12. Nakatsuka, O. *et al.* Mobility behavior of Ge<sub>1-x</sub>Sn<sub>x</sub> layers grown on silicon-on-insulator substrates. *Jpn. J. Appl. Phys.* **49**, 04DA10 (2010).

- 13. Liu, Y., Deal, M. D. & Plummer, J. D. High-quality single-crystal Ge on insulator by liquid-phase epitaxy on Si substrates. *Appl. Phys. Lett.* 84, 2563–2565 (2004).

- Hu, S., Leu, P. W., Marshall, A. F. & McIntyre, P. C. Single-crystal germanium layers grown on silicon by nanowire seeding. *Nat. Nanotechnol.* 4, 649–53 (2009).

- 15. Toko, K., Ohta, Y., Tanaka, T., Sadoh, T. & Miyao, M. Chip-size formation of high-mobility Ge strips on SiN films by cooling rate controlled rapid-melting growth. *Appl. Phys. Lett.* **99**, 32103 (2011).

- 16. Littlejohns, C. G. et al. Next Generation Device Grade Silicon-Germanium on Insulator. Sci. Rep. 5, 8288 (2015).

- 17. Toko, K., Nakao, I., Sadoh, T., Noguchi, T. & Miyao, M. Electrical properties of poly-Ge on glass substrate grown by two-step solid-phase crystallization. *Solid. State. Electron.* **53**, 1159–1164 (2009).

- 18. Tsao, C.-Y., Huang, J., Hao, X., Campbell, P. & Green, M. A. Formation of heavily boron-doped hydrogenated polycrystalline germanium thin films by co-sputtering for developing p+ emitters of bottom cells. Sol. Energy Mater. Sol. Cells 95, 981–985 (2011).

- Jung, H.-W., Jung, W.-S., Yu, H.-Y. & Park, J.-H. Electrical properties of phosphorus-doped polycrystalline germanium formed by solid-phase and metal-induced crystallization. J. Alloys Compd. 561, 231–233 (2013).

- Sadoh, T., Kamizuru, H., Kenjo, A. & Miyao, M. Low-temperature formation (<500 °C) of poly-Ge thin-film transistor with NiGe Schottky source/drain. Appl. Phys. Lett. 89, 192114 (2006).

- 21. Kabuyanagi, S., Nishimura, T., Nagashio, K. & Toriumi, A. Impacts of oxygen passivation on poly-crystalline germanium thin film transistor. *Thin Solid Films* 557, 334–337 (2014).

- Watakabe, H., Sameshima, T., Kanno, H. & Miyao, M. Electrical properties for poly-Ge films fabricated by pulsed laser annealing. *Thin Solid Films* 508, 315–317 (2006).

- 23. Yeh, W., Chen, H., Huang, H., Hsiao, C. & Jeng, J. Superlateral growth of a-Ge film by excimer laser annealing. *Appl. Phys. Lett.* 93, 94103 (2008).

- 24. Sakaike, K., Higashi, S., Murakami, H. & Miyazaki, S. Crystallization of amorphous Ge films induced by semiconductor diode laser annealing. *Thin Solid Films* 516, 3595–3600 (2008).

- Matsui, T., Kondo, M., Ogata, K., Ozawa, T. & Isomura, M. Influence of alloy composition on carrier transport and solar cell properties of hydrogenated microcrystalline silicon-germanium thin films. Appl. Phys. Lett. 89, 142115 (2006).

- Tada, M. et al. Low Temperature Germanium Growth on Silicon Oxide Using Boron Seed Layer and In Situ Dopant Activation. J. Electrochem. Soc. 157, H371–H376 (2010).

- 27. Usuda, K. et al. High-performance poly-Ge short-channel metal-oxide-semiconductor field-effect transistors formed on  $SiO_2$  layer by flash lamp annealing. Appl. Phys. Express 7, 56501 (2014).

- 28. Wang, Z. M., Wang, J. Y., Jeurgens, L. P. H., Phillipp, F. & Mittemeijer, E. J. Origins of stress development during metal-induced crystallization and layer exchange: Annealing amorphous Ge/crystalline Al bilayers. *Acta Mater.* 56, 5047–5057 (2008).

- 29. Hu, S., Marshall, A. F. & McIntyre, P. C. Interface-controlled layer exchange in metal-induced crystallization of germanium thin films. *Appl. Phys. Lett.* **97**, 82104 (2010).

- 30. Toko, K. *et al.* Low-temperature (180 °C) formation of large-grained Ge (111) thin film on insulator using accelerated metal-induced crystallization. *Appl. Phys. Lett.* **104**, 22106 (2014).

- 31. Park, J.-H., Kasaĥara, K., Hamaya, K., Miyao, M. & Sadoh, T. High carrier mobility in orientation-controlled large-grain (≥50 μm) Ge directly formed on flexible plastic by nucleation-controlled gold-induced-crystallization. *Applied Physics Letters* **104**, 252110 (2014)

- 32. Kasahara, K. *et al.* Electrical properties of pseudo-single-crystalline germanium thin-film-transistors fabricated on glass substrates. *Appl. Phys. Lett.* **107**, 142102 (2015).

- 33. Uchida, N. *et al.* Carrier and heat transport properties of polycrystalline GeSn films on SiO<sub>2</sub>. *Appl. Phys. Lett.* **107**, 232105 (2015).

- 34. Takeuchi, W. et al. High hole mobility tin-doped polycrystalline germanium layers formed on insulating substrates by low-temperature solid-phase crystallization. Appl. Phys. Lett. 107, 22103 (2015).

- Sadoh, T., Kai, Y., Matsumura, R., Moto, K. & Miyao, M. High carrier mobility of Sn-doped polycrystalline-Ge films on insulators by thickness-dependent low-temperature solid-phase crystallization. Appl. Phys. Lett. 109, 232106 (2016).

- 36. Renner, O. The influence of annealing on the density of amorphous germanium films. *Thin Solid Films* 12, S43–S45 (1972).

- 37. Floro, J. A., Kotula, P. G., Seel, S. C. & Srolovitz, D. J. Origins of growth stresses in amorphous semiconductor thin films. *Phys. Rev. Lett.* **91**, 96101 (2003).

- 38. Wang, Z., Flötotto, D. & Mittemeijer, E. J. Stress originating from nanovoids in hydrogenated amorphous semiconductors. *J. Appl. Phys.* **121** (2017).

- 39. Haesslein, H., Sielemann, R. & Zistl, C. Vacancies and Self-Interstitials in Germanium Observed by Perturbed Angular Correlation Spectroscopy. *Phys. Rev. Lett.* **80**, 2626–2629 (1998).

- 40. Seto, J. W. Y. The electrical properties of polycrystalline silicon films. J. Appl. Phys. 46, 5247-5254 (1975).

- Lee, J. N. et al. Effect of Deposition Temperature on the Crystallization Mechanism of Amorphous Silicon Films on Glass. Jpn. J. Appl. Phys. 36, 6862–6866 (1997).

### **Acknowledgements**

This work was financially supported by the JSPS KAKENHI (No. 26709019), the Iketani Science and Technology Foundation, and the Nanotech CUPAL. The authors are grateful to Prof. T. Sakurai at the University of Tsukuba for assistance with the Hall effect measurement. Some experiments were conducted at the International Center for Young Scientists in NIMS.

#### **Author Contributions**

K.T. conceived and designed the experiments. R.Y. and K.M. conducted the experiments and analyses. K.T. and T.S. managed the research and supervised the project. All the authors discussed the results and commented on the manuscript.

#### **Additional Information**

**Competing Interests:** The authors declare that they have no competing interests.

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2017