# Resistance change phenomenon in $Ta_2O_5/TiO_2$ stacked structure and its application to non-volatile memory

Yukihiro Sakotsubo

February 2017

# Resistance change phenomenon in $Ta_2O_5/TiO_2$ stacked structure and its application to non-volatile memory

Yukihiro Sakotsubo Doctoral program in Physics

Submitted to the Graduate School of Pure and Applied Sciences in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Science

> at the University of Tsukuba

# Supervisor

Dr. Yoichi Ootuka

# Local Members of the Jury

- Dr. Kikuo Yamabe

- Dr. Eiji Nishihori

- Dr. Susumu Okada

- Dr. Akinobu Kanda

## Preface

This thesis is submitted to the Graduate School of Pure and Applied Sciences at the University of Tsukuba, Japan, in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Science. The present study found its origins in a research program on emerging nonvolatile memory which took place from October 2008 to March 2010 in Device platforms research laboratory of NEC Corporation.

## Acknowledgments

I would like to express my sincere thank Dr. Yoichi Ootuka, Professor of the Department of Pure and Applied Sciences in Univ. of Tsukuba, who gave the educational guidance such as fruitful discussions and reviewing the manuscripts of this thesis to me. He encouraged me over 16 years since 2001 when I joined his laboratory. His mentorship was paramount in providing a well-rounded experience consistent my long-term career goals.

In the course of the year it has been a great pleasure to discuss together with Dr. Kikuo Yamabe, Dr. Eiji Nishihori, Dr. Susumu Okada and Dr. Akinobu Kanda. Dr. Yamabe gave me his experience in an industry and a deep understanding of device reliability. Dr. Nishihori gave me advanced knowledge on material and its physical analysis. Dr. Okada gave me theoretical support for data analysis in my study. Dr. Kanda urged me to take careful data analysis.

This study was mainly performed in a research program on emerging nonvolatile memory which took place from October 2008 to March 2010 in Device platforms research laboratory of NEC Corporation. I would like to thank Dr. Yasunori Mochizuki, Director of the Device Platform Laboratories for giving me opportunities for this research. Also, I would like to thank Dr. Naoki Kasai, Dr. Yasunobu Nakamura, and Dr. Shingi Fujieda for advice on useful discussion at the time of research.

I would like to appreciate Dr. Masayuki Terai who is a cooperative researcher and had offered various help to my studies. It was with his support that I was able to attend to a number of interesting congresses. Also, I would like to thank Dr. Hiromitsu Hada who managed the research program and always encouraged me.

I would like to thank Dr. Toshitsugu Sakamoto who gave some experimental setup for electric measurements, and also thank Setsu Kotsuji who assisted me in electrical measurement in this study.

My special appreciation goes to Dr. Kimihiko Ito who gave me various support in fabricating memory cell used in this study. His dedicated aid has made my research progress.

I would like to thank Dr. Munehiro Tada, Yuko Yabe, Yukihiro Saito, Ichimura, Koji Masuzaki, Taeko Ikarashi and Tatsuhiko Nohisa who gave me the professional assistance. If I could not get their support, I could not prepare the samples used in this study.

My appreciation goes to Dr. Nobuyuki Ikarashi and Makiko Oshida who provided high resolution transmission electron microscope images of the samples, and Dr. Ichihashi who provided X-ray

diffraction images of the samples, and Dr. Naoki Banno who provided the optimized process condition for getting high insulative  $Ta_2O_5$  layer.

During this study, I have had many fruitful and open-minded discussions with other researchers in the Device platforms research laboratory of NEC Corporation. These include Dr. Koichiro Okamoto, Dr. Makoto Miyamura, Dr. Yukihide Tsuji, Dr. Kensuke Takahashi, Dr. Akio Toda, Dr. Kaoru Mori, Dr. Takashi Nakagawa, Dr. Kenzo Manabe, Dr. Hiroshi Sunamura, Dr. Akihiro Tanabe, Dr. Takashi Hase, Dr. Toru Tatsumi, and Dr. Hirohiro Watanabe.

I would like to express my sincere thank Dr. Taizo Ohgi who gave me how to analyze the current-voltage characteristics of the tunnel junction system. If I could not get his lecture, I could not analyze the data yielded in this study.

I would like to thank Dr. Akio Nishida, Director of the Department of Advanced Process and Device Development in SanDisk Limited, and Dr. Yoichiro Tanaka, Manager of the material group in the department. They gave me encouragement for acquiring the degree.

Finally, and most importantly, I would like to thank my wife Miho. Her support, encouragement, quiet patience and unwavering love were undeniably the bedrock upon which the past seven years of my life have been built. Also, I am thankful to my darling daughter and son, Aira and Ibuki, for giving me motivation and happiness. I thank my parents and brother, Toshihiro, Chiyoko and Tomohiro, for their faith in me and allowing me to be as ambitious as I wanted. It was under their watchful eye that I gained so much experience and an ability to tackle challenges head on.

Yukihiro Sakotsubo

Yokkaichi, February 2017

# List of Publications

In the thesis, the references listed below are referred.

#### Publications Related to Thesis

[1] Y. Sakotsubo, M. Terai, S. Kotsuji, T. Sakamoto and H. Hada, "Physical model for reset state of Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub>-stacked ReRAM", *41th International Conference on Solid State Devices and Material, Technology Digest of Technical Papers*, (2009) 1204-1205.

[2] Y. Sakotsubo, M. Terai, S. Kotsuji, T. Sakamoto and H. Hada, "Physical Model for Reset State of Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub>-stacked Resistance Random Access Memory", *Japanese Journal of Applied Physics* **49**, (2010) 04DD19

[3] M. Terai, Y. Sakotsubo, Y. Saito, S. Kotsuji and H. Hada, "Effect of Bottom Electrode of ReRAM with Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> Stack on RTN and Retention", *2009 International Electron Device Meeting*, Technology Digest of Technical Papers, (2009) 775-778.

[4] M. Terai, Y. Sakotsubo, S. Kotsuji, and H. Hada, "Resistance Controllability of Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> Stack ReRAM for Low-Voltage and Multilevel Operation", *Electron Device Letters* **31**, (2010) 204-206.

[5] M. Terai, Y. Sakotsubo, Y. Saito, S. Kotsuji, and H. Hada, "Memory-State Dependence of Random Telegraph Noise of Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> Stack ReRAM", *Electron Device Letters* **31**, (2010) 1302-1304.

[6] Y. Sakotsubo, M. Terai, S. Kotsuji, Y. Saito, M. Tada, Y. Yabe, and H Hada, "A New Approach for Improving Operating Margin of Unipolar ReRAM using Local Minimum of Reset Voltage", *2010 Symposium on VLSI*, Technology Digest of Technical Papers, (2010) 87-88.

[7] M. Terai, M. Saitoh, T. Nagumo, Y. Sakotsubo, Y. Yabe, K. Takeda and T Hase, "High Thermal Robust ReRAM with a New Method for Suppressing Read Disturb", *2011 Symposium on VLSI*, Technology Digest of Technical Papers, (2011) 50-51.

[8] Y. Sakotsubo, "NONVOLATILE SEMICONDUCTOR OTHER PUBLICATIONS MEMORY DEVICE AND MANUFACTURING METHOD THEREOF", US 8,598,564 (2013).

[9] Y. Sakotsubo, M. Terai, M. Tada, Y. Yabe, and Y. Saito, "SEMICONDUCTOR DEVICE WITH VARIABLE RESISTANCE ELEMENT AND METHOD FOR MANUFACTURING THE SAME", US 8,766,233 (2014).

# Table of contents

| Chapt        | er 1. Introduction3                                                           |

|--------------|-------------------------------------------------------------------------------|

| <b>1-</b> 1  | Resistance change phenomena in Transition metal oxide4                        |

| 1- <i>2</i>  | Resistance change model for transition metal oxide5                           |

| i            | Interface switching model for bipolar-type cell5                              |

| ii           | Filamentary switching model for unipolar-type cell6                           |

|              | ii- 1 Filamentary conductive path in transition metal oxide                   |

|              | ii- $2$ Thermal reaction-based resistance change model                        |

| <b>1</b> - 3 | Filamentary resistance change devices for non-volatile memory application9    |

| i            | Advantages of filamentary resistance change devices9                          |

| ii           | Challenges and the solutions9                                                 |

|              | <i>ii- 1 1T-1R type device</i>                                                |

|              | ii- ${\it 2}$ Heterogeneous TMO stacked structure for the memory cell         |

| <b>1-</b> 4  | Purposes of this study                                                        |

| i            | Resistance change phenomenon in $Ta_2O_5/TiO_2$ stacked structure             |

| ii           | Physical model for high resistance state of $Ta_2O_5/TiO_2$ stacked structure |

| iii          | Non-volatile memory performance of $Ta_2O_5/TiO_2$ stacked structure          |

| <b>1-</b> 5  | Outline of this thesis                                                        |

| <b>1</b> - 6 | Reference                                                                     |

| Chapt        | er 2. Experimental21                                                          |

| <b>2-</b> 1  | Ta <sub>2</sub> O <sub>5</sub> /TiO <sub>2</sub> stacked memory cell21        |

| i            | TiO <sub>2</sub> layer                                                        |

| ii           | Ta <sub>2</sub> O <sub>5</sub> layer                                          |

| <b>2-</b> 2  | Device structure and switching operation                                      |

| i            | Memory cell integration to 1T-1R type device                                  |

| ii           | Unipolar and bipolar switching operation25                                    |

| <b>2-</b> 3  | Measurement setup and Samples27                                               |

| i            | Evaluation systems and measurement setup27                                    |

| ii           | Samples                                                                       |

| 2-4 Refere       | ence                                                                                                                  | 30   |

|------------------|-----------------------------------------------------------------------------------------------------------------------|------|

| Chapter 3.       | Filamentary resistance change phenomenon in $Ta_2O_5/TiO_2$ stacked structure.                                        | 31   |

| 3- 1 I-V cho     | aracteristics of pristine film and FORMING phenomenon                                                                 | 32   |

| 3- 2 Filame      | entary resistance change phenomenon in TiO $_2$ layer                                                                 | 37   |

| i RESET          | phenomenon in Ta <sub>2</sub> O <sub>5</sub> /TiO <sub>2</sub> stacked memory cell                                    | 37   |

| ii SET ph        | nenomenon in Ta <sub>2</sub> O <sub>5</sub> /TiO <sub>2</sub> stacked memory cell                                     | 43   |

| 3- 3 Summ        | nary                                                                                                                  | 45   |

| 3-4 Refere       | ence                                                                                                                  | 46   |

| Chapter 4.       | Electrical conduction in High resistance states of Ta <sub>2</sub> O <sub>5</sub> /TiO <sub>2</sub> stacked structure | 2.51 |

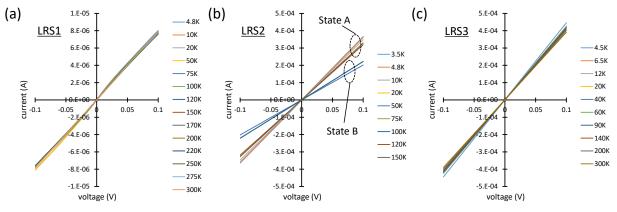

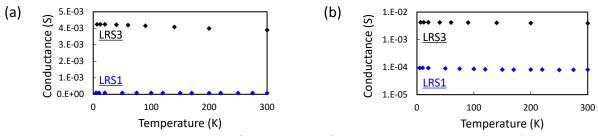

| 4-1 Electri      | ical properties of low resistance states                                                                              | 52   |

| 4- 2 Electri     | ical properties of high resistance states                                                                             | 54   |

| i Tempe          | erature dependence of I-V characteristics                                                                             | 54   |

| ii Therm         | nally activated conduction around the room temperature                                                                | 55   |

| 4- $3$ Physic    | al model for high resistance state                                                                                    | 59   |

| 4- $4$ Summ      | nary                                                                                                                  | 62   |

| 4- 5 Refere      | ence                                                                                                                  | 62   |

| Chapter 5.       | Non-volatile memory performance of Ta <sub>2</sub> O <sub>5</sub> /TiO <sub>2</sub> stacked structure                 | 65   |

| 5- $1$ Integr    | rated Ta <sub>2</sub> O <sub>5</sub> /TiO <sub>2</sub> stacked memory cell to the 1 kbit array                        | 65   |

| 5- $\it 2$ Optim | ization of SET/RESET operation                                                                                        | 67   |

| 5- 3 Demo        | nstration of highly robust non-volatile memory                                                                        | 70   |

| 5- $4$ Summ      | ary                                                                                                                   | 72   |

| 5- 5 Refere      | ence                                                                                                                  | 73   |

| Chapter 6.       | Summary                                                                                                               | 75   |

# Chapter 1. Introduction

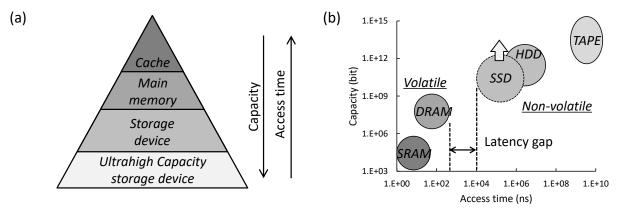

Today's highly information-oriented society is carried by the data processing which is implemented by pyramidal hierarchical structure shown in Figure 1-1(a) of memories and storage devices [1]. To improve the data processing further, reducing the latency gaps is important. Traditionally, improvement of data processing speed and capacity is most interested in the product development for each memory and storage classes. Although the latency gap between dynamic random access memory (DRAM) and hard-disc drive (HDD) had not been bridged by the efforts [2], solid-state drive (SSD) composed of NAND flash memory device appeared into the gap recently, and the SSD dramatically reduced the gap and improved the data processing speed. And now, the SSD is replacing HDD market through the effort of cost reduction rapidly as shown in Figure 1-1 (b). However, the SSD does not fully bridge the gap fundamentally, because the device composed of NAND flash memory cannot be accessed randomly like a DRAM. So, the "non-volatile memory (NVM)" bridging the latency gap is highly required [3].

Figure 1-1 (a) Pyramidal hierarchical structure. (b) Positioning for memories and storages.

Now, transition metal oxide (TMO) -based resistance change device is attracting attention as a candidate of the bridging device between main memory and storage device [3-11]. The cell structure of the device is a simple Metal-TMO-Metal stack, and well-known materials such as hafnium oxide and titanium oxide are used for the TMO layer. The zero-bias conductivity of the cell is changed by only applying the voltage to the cell. This device is characterized by three features [3-11]. Firstly, this device has long retention time which is enough longer than the access times. Secondly, this device works with ultra-high speed less than 100ns. These two features satisfy the demand for "non-volatile memory" bridging the latency gap. Thirdly, the material and process are highly compatible with CMOS process, and one does not need additional dedicated facility and process optimization for fabricating the structure because these material and process are already used in a current product line. Thus, TMO-base resistance change device is the most promising candidate among emerging non-volatile memory devices such as phase change device and magnetic change device [3].

Resistance change phenomenon in the TMO materials has not yet been elucidated. For example, it is not clear why the state changes by applying the voltage and why the changed states keep long time. The resistance change behavior is different for each TMO material, and a variety of resistance change models have been proposed to explain it [3]. In this sense, basic research is indispensable to the

development of the resistance change memory. We will introduce the background easily in the following.

## 1-1 Resistance change phenomena in Transition metal oxide

In 1962, T. W. Hickmott observed a hysteresis loop in current-voltage characteristic of Metal-Insulator-Metal (MIM) structure with oxide insulator such as titanium oxide, zirconium oxide and silicon oxide for the first time [12]. Since then, resistance change phenomena have been found and studied in various binary and multi-nary oxide [15-18] such as , Ag/NiO/Ni [13], Al/TiO<sub>2</sub>/Ti [14], Ti/Cu<sub>2</sub>O/Cu [7], Pt/Pr<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub>(PCMO)/Pt [19] and Pt/PZT/Pt [20, 21] before the late 2000s. This phenomenon was called "Colossal electro-resistance (CER)" because the resistance is changed by electrical stimulation [22].

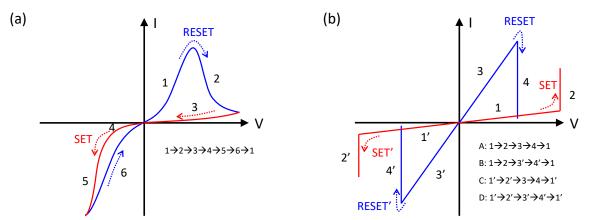

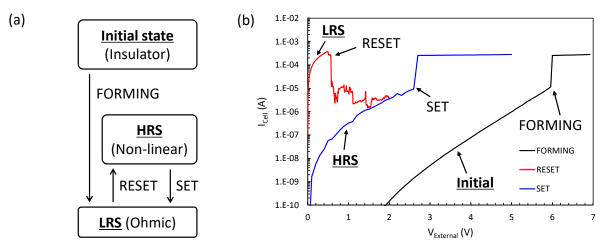

The resistance change behaviors are classified into two types, bipolar- and unipolar- (nonpolar-) type, depending on the materials composing the cell. Typical current-voltage characteristics for each type are shown in Figure 1-2. The cell has two states, high resistance state (HRS) and low resistance state (LRS), and the state is changed by applying the voltage to the cell. An operation changing the cell from LRS to HRS is called RESET, while opposite operation is called SET in the both type cells. In the bipolar-type cells, initial state (as-fabricated pristine state) is usually LRS, and the resistance can be changed by bipolar-type operation [Fig. 1-2(a)]. On the other hand, in the unipolar-type cells, initial state is usually insulating, and the resistance can be changed by unipolar-type operation of either polarity [Fig. 1-2(b)]. The both types of the cells can be also operated with pulsed voltage. Although essential pulse width for SET and RESET operations depends on the pulse height, resistance change phenomena occur in ultra-short pulse less than 10ns [9-11, 19].

Figure 1-2 Schematics of resistance change phenomena. (a) I-V characteristics in bipolar-type cell. Single hysteresis loop is observed. (b) I-V characteristics in unipolar- (nonpolar-) type cell. RESET and SET phenomena are observed in either polarities as indicated by A to D.

# 1- $2\;$ Resistance change model for transition metal oxide

There have been proposed several models for resistance change phenomena in particular class of materials and structure with electrical conduction model. They include the ferroelectricity-based model [23-25], insulator-metal transition (IMT) -based model [26-28], charge-trap-based model [29-31], and V<sub>0</sub> cohesion-isolation transition-based model [32-34]. The ferroelectricity-based model was proposed to described the resistance change in ferroelectric materials such as Cr-doped SrZrO<sub>3</sub> [21], Cr-doped SrTiO<sub>3</sub> [35], Pt/Pb(Zr<sub>0.52</sub>Ti<sub>0.48</sub>)O<sub>3</sub> /SrRuO<sub>3</sub> hetero-structure [36], and is based on the reversal of electric polarization that causes a change in tunnel barrier or the Schottky barrier [23-25]. The IMT-based model deals the resistance change in materials such as Cr-doped SrZrO<sub>3</sub> [21], and Ag/CeO<sub>2</sub>/La<sub>0.67</sub>Ca<sub>0.33</sub>MnO<sub>3</sub> [37], and the strong electron correlation in these materials are thought to be essential for the resistance change [26-28]. The charge-trap-based model is a model for Pt/Pr<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub> [29-31]. The V<sub>0</sub> cohesion-isolation transition is caused by carrier injection/removal. This model is a generalized resistance change mechanism in binary oxides such as TiO<sub>2</sub> [32, 33], NiO [33] and HfO<sub>2</sub> [34].

As for the simple binary TMO-base resistance change devices, the features such as the cell area dependence and the switching polarity differ among devices, and are currently discussed by two types of model, i.e., the interface switching model [38] and the filamentary switching model [3, 15, 38]. Main features of both models are summarized in Table 1-1, which we will explain briefly in the following.

|                                               | Interface switching devices                  | Filamentary switching devices           |  |

|-----------------------------------------------|----------------------------------------------|-----------------------------------------|--|

| Switching polarity                            | Bipolar                                      | Unipolar (Nonpolar)*                    |  |

| Switching model                               | Redox reaction                               | Thermal reaction                        |  |

|                                               | (Reduction & Oxidation)                      | (Conductive path formation & rupture)   |  |

| Physical model                                | Schottky barrier height                      | LRS: Ohmic conductor                    |  |

|                                               | (LRS: Low, HRS: High)                        | HRS: Tunnel barrier                     |  |

| Typical cell SW layer: Non-stoichiometric TMO |                                              | SW layer: Stoichiometric TMO            |  |

| structure                                     | Electrode: Inert electrode                   | ectrode: Inert electrode Electrode: N/A |  |

|                                               | <i>и</i> <u>и</u> <u>и</u> <u>и</u> <u>и</u> |                                         |  |

Table 1-1 General understanding for TMO-based switching devices [3]

*Note:* \*In this devices, "unipolar" has the same meaning as "nonpolar". SET/RESET phenomena are observed in either polarity.

#### i Interface switching model for bipolar-type cell

Interface switching model was proposed for explaining bipolar-type resistance change phenomenon (Fig. 1-2(a)). It is expected that the resistance change occurs at the interface of the electrode and the TMO layer owing to movement of oxygen vacancies/ions or trapping/de-trapping of electrons or holes under the applied electric field [38]. The resistance is usually proportional to the cell area.

In 2008, Wei et al. investigated composition profile of Pt/TaOx/Pt structure by Hard X-ray Photoemission Spectroscopy (HX-PES), and found that the ratio of  $TaO_{2-\beta}/Ta_2O_{5-\delta}$  increases from HRS to LRS, indicating that the  $Ta_2O_{5-\delta}$  component of HRS is reduced to the  $TaO_{2-\beta}$  component of

LRS [39, 40]. The origin of the resistance change was attributed to the changing of the barrier height between the anode and  $TaO_x$  caused by the redox reaction.

To achieve stable resistance change, the device should be composed of non-stoichiometric TMO layer sandwiched between the inert metal electrodes, and the oxygen profile of the unstoichiometric TMO layer should have gradient to control the resistance change region. Moreover, high work-function material for anode electrode achieves stable RESET operation. The interface resistance increases with increasing the Schottky barrier height caused by the oxygen atoms segregation at the anode/oxide interface. Based on these experimental evidences, device model, which could explain well the resistance change behavior, was constructed [41, 42]. By this breakthrough, mass-production of new non-volatile memory with the interface-type cell in 2012.

#### ii Filamentary switching model for unipolar-type cell

Filamentary switching model is proposed to explain another type of devices, where the initial state is a HRS, resistance can be changed by unipolar-type operation of either polarity (see Fig. 1-2(b)), and resistance of both LRS and HRS does not depend on cell area [43-51]. The operation changing from an initial HRS to a LRS is especially called FORMING. By a FORMING operation, filamentary thin conductive path is postulated to be formed perpendicular to the resistance change layer [3]. The region other than the filament is still unchanged in the initial state. This filamentaryconductive-path hypothesis is supported by the fact that the resistance of both LRS and HRS is almost constant irrespective of the cell area [48-51].

#### ii-1 Filamentary conductive path in transition metal oxide

In the early studies, it was speculated that resistance change occurs at grain boundaries which role filamentary ion channel of the polycrystalline TMO layers [12-15, 47], and similar mechanism as the interface switching was supposed [43-46]. In 2000s, the resistance change phenomena were found even in grain boundary-less stoichiometric binary TMO layer such as HfO<sub>2</sub> and NiO formed by the atomic-layer deposition (ALD) method and the epitaxial growth method [43, 49]. Moreover it was reported that the resistance can be changed not only by the bipolar-type operation but also by the unipolar- (nonpolar-) type operation [43-51]. Thus, we understood that the resistance change mechanism in these devices is different fundamentally from that in the interface switching devices [3].

The change during the FORMING is very similar to the dielectric breakdown of gate oxide (e.g.  $SiO_2$ ,  $HfO_2$ ) in the MOS transistor. Defects are generated randomly in the bulk by electrical stress-induced Si-O/Hf-O bond breaking [52]. The defect generation rate is given by following expression,

$$P_E \propto exp\left(-rac{E_a - eta E_{OX}}{k_B T}

ight),$$

(1-1)

where  $E_a$  is the activation energy for Si-O/Hf-O bond breaking,  $\beta$  is the contribution of the bond polarization to the local electric field,  $E_{OX}$  is average electrical field in the oxide,  $k_B$  is the Boltzmann constant, and T is the temperature [52]. Leakage current through the oxide increase with increasing defects. Finally, the generated defects complete a percolation path that bridges the two electrodes across the oxide, eventually [53-55]. The current through the path increases significantly and causes lateral growth of the path. It is noted that isolated defect (typically oxygen vacancy) in the oxide behaves as an electron trap.

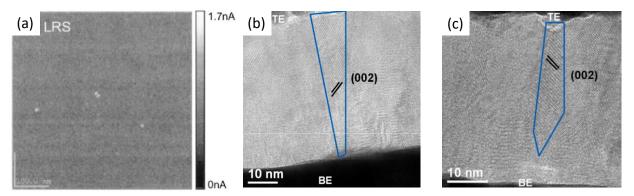

These percolation paths composed of generated defects are formed in the filamentary switching devices after FORMING operation [54]. When the percolation path has an Ohmic current-voltage characteristics, this conductive path is called "filament". Thus, it is believed that the filaments are locally formed in the TMO layer. In 2005, B. J. Choi showed the evidence of localized conductive path in the TiO<sub>2</sub> thin film grown by ALD by using conductive atomic force microscope (CAFM) (see Figure 1-3(a)) [43]. Since 2010, studies of direct observation of the conductive filaments in single TiO<sub>2</sub> layer cell by analyzing crystal structure using a transmission electron microscope (TEM) have been reported [56-59]. According to D.H. Kwon et al., Magnéli phases (Ti<sub>4</sub>O<sub>7</sub>) was confirmed in the TiO<sub>2</sub> layer after FORMING [56]. As Ti<sub>4</sub>O<sub>7</sub> shows metallic conduction at room temperatures, Ti<sub>4</sub>O<sub>7</sub> region bridging the electrodes is regarded as the conducive filament. Moreover, it was confirmed that the Magnéli phases is disappeared in the middle region between the electrodes after RESET operation [56].

Figure 1-3 Evidences of a filamentary conductive path in  $TiO_2$  film. (a) Conductivity mapping results of the low resistance state  $TiO_2$  films, using atomic force microscopy systems with conductive tips(CAFM) [42]. The bright spots represent the conducting spots. (b) High-resolution TEM image of the low resistance state TiO<sub>2</sub> films [56]. (c) High-resolution TEM image of the high resistance state TiO<sub>2</sub> films [56].

#### ii-2 Thermal reaction-based resistance change model

Unipolar switching shown in Figure 1-2(b) of filamentary switching device is obviously not explained by the redox reaction-based resistance change model for the interface switching. Most promising resistance change model for the *RESET* is the thermal reaction-based model which was provided by the linear temperature dependence of the RESET voltage [8, 60-65].

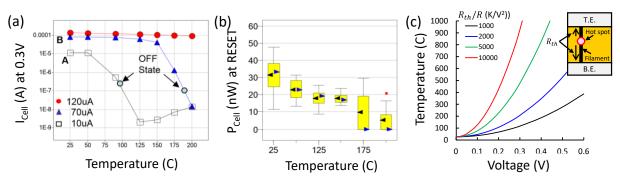

In 2006, Fang et al. investigated temperature dependence of LRS retention property, and found transition to HRS from LRS after thermal stress [8]. The critical temperature for the LRS-HRS transition increases as the LRS resistance decreases as reprinted in Figure 1-4(a). Moreover, it is confirmed that RESET power decreases as the ambient temperature [Figure 1-4(b)] [8, 63]. These results strongly implied that RESET mechanism in the filamentary switching device is caused by the thermal reaction.

Figure 1-4 (a) Thermal stability of LRS in Cu/Cu<sub>2</sub>O/Ni memory cells [8]. The critical temperature for a LRS-HRS transition increases as the LRS resistance decreases. (b) RESET power dependence on ambient temperature [8]. RESET power decreases as the ambient temperature. The box shows the data range and the triangle indicates the mean and median. (c) Calculated filament temperature dependence on the ratio of thermal resistance to filament resistance [63-65].  $R_{th}$  is equivalent thermal resistance of filament describing the heat loss from the hot spot on the filament toward the top and bottom electrodes as shown in inset of (c).

In 2008, Cagli et al. proposed the joule heating model which was considered that the defects composing the filament are relaxed to stable states by thermally acceleration [64, 65]. The relaxation probability is described in following equation,

$$\nu \propto exp\left(-\frac{E_a}{k_BT}\right)$$

, (1-2)

where  $E_a$  is the activation energy for the relaxation,  $k_B$  is the Boltzmann constant, and T is the local temperature. The local temperature depends on power consumption on the filament and thermal conductivity of the filament;

$$T = T_0 + \frac{R_{th}}{R} V^2, \qquad (1-3)$$

where  $T_0$  is the ambient temperature and  $R_{th}$  is the equivalent thermal resistance of the filament describing the heat loss from the hot spot on the filament toward the top and bottom electrodes as shown in inset of Figure 1-4(c). The filament temperature just depends on the voltage across the filament [Fig. 1-4(c)], and the relaxation probability significantly increases with the voltage. Therefore, the defect states composing conductive filament decrease during the RESET operation, and the conductive filament is ruptured, finally.

# 1-3 Filamentary resistance change devices for non-volatile memory application

Nowadays, conventional DRAM and NAND flash memory developments face the serious challenges which exist in the tradeoff between READ/WRITE latencies, WRITE/ERASE immunity, data retention and scalability, and the filamentary resistance change devices are expected to be able to overcome the tradeoff relation, fundamentally. Requirements for achieving the non-volatile memory (NVM) are

- 1. Low READ/WRITE latencies,

- 2. Highly WRITE/ERASE immunity (i.e. cycle endurance),

- 3. Highly non-volatility (i.e. data retention under thermal and electrical stresses).

- i Advantages of filamentary resistance change devices

In the filamentary resistance change devices, the LRS (On-state) composed of the conductive filament bridging the electrodes is the most important state for the retention properties such as non-volatility and disturb immunity. If we use the result of simulation with Eq. 1-2 and Eq. 1-3, the retention time of the LRS depends strongly on the applied voltage, and the retention time at READ bias (~0.1V) is about 10<sup>12</sup> times longer than that at RESET bias (~0.5V) although sufficient cell current can be obtained in low voltage due to the ohmic property of LRS in filamentary switching device. So, the state can be sensed with short integration time compared to the interface switching device which has nonlinear property of LRS. These facts mean that filamentary switching devices make both highly non-volatility and low READ/WRITE latencies happen at once.

The filamentary resistance change devices have two other significant advantages over other candidates such as the TMO-based interface switching devices, the phase change devices and the magnetic change devices in terms of the process integration feasibility in a chip fabrication plant (FAB). First one is the fact that the materials such as stoichiometric TMO is already introduced in the FAB. These materials are used for the gate insulator of a field effect transistor. The other one is that the materials can be deposited with atomic layer deposition (ALD) method. This means that the device is applicable to three dimensional (3D) structure which realize the both high density and high cost performance at once. Moreover it is expected to be able to be scaled the cell size to the filament size level. Thus, filamentary resistance change devices are the most promising candidate for the next-generation nonvolatile memories.

## ii Challenges and the solutions

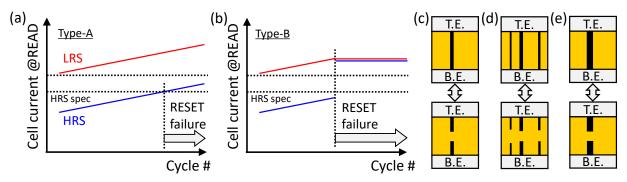

Filamentary switching devices have a challenge in the SET/RESET cycle endurance. Generally, cell current of both LRS and HRS increases as the SET/RESET cyclings advance. Most frequent failure is RESET failure, which is classified into two types shown in Figure 1-5(a) and (b). In Type-A failure mode, the reduction of the cell current after RESET operation is not large enough to meet the HRS specification. In Type-B failure, the cell current get stuck on the LRS because the switching current for RESET becomes larger than drivability of voltage source. Both failures are caused by increase of

total cross-sectional area of the filaments, which is originated from filament number [Fig. 1-5(d)] and/or thickness [Fig. 1-5(e)] [43].

Figure 1-5 Schematics of RESET failure modes. Cell currents of both LRS and HRS increase with increasing cycling number. (a) Type-A failure mode: Cell current does not reach the HRS criteria. (b) Type-B failure mode: Cell current get stuck on the LRS. (c) Schematics of the filament in initial cycling stage. (d) Schematics of the filament in aged cells. (e) Schematics of the filament with large SET current.

So, to suppress the additional filament formation is a key to improve the cycle endurance, and the process had been studied in details by R. Degraeve [66]. The risk of additional filament formation during SET operation is higher than that during RESET operation, because the electrical stress such as electrical field is larger in SET operation. In order to reduce the stress at the SET operation, we have two methods [67]: One is the cutoff of the stress just after SET by using series transistor. The other one is the reduction of the effective electrode size to the filament size by stacking relatively stable TMO layer in series.

#### ii-1 1T-1R type device

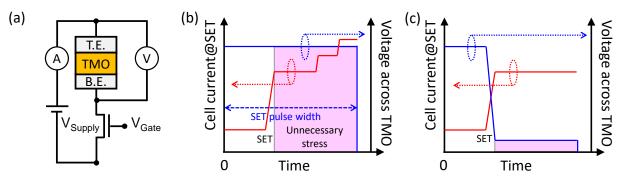

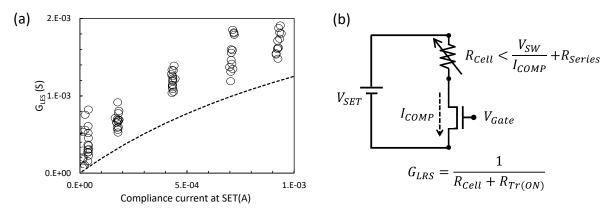

In 2004, usefulness of 1T-1R type device structure was introduced by I. G. Baek et al. [5]. Transistor (FET) controlling the operating current was incorporated in series with the memory cell as shown in Figure 1-6(a). Because of current limiting feature of FET, the voltage across the memory cell decreases instantaneously after SET occurs, as shown in Figure 1-6(c). Thus, additional filament formation risk is significantly reduced [54-55]. Oneness of the conductive filament formed on the 1T-1R configuration was shown in several literatures. I. G. Baek et al. and H. Shima et al. reported that resistance of LRS does not depend on the cell area [5, 61]. In addition, K. Kinoshita reported that one of the divided cells after FORMING operation is always high resistive state although another one showed the low resistance that agreed with LRS before being divided [68].

1T-1R type device is also useful to control the filament thickness [69-72]. K. Kinoshita et al. reported that the RESET current depends on the compliance current at SET operation [71]. Type-B RESET failure is dramatically reduced by using 1T-1R type device structure.

Figure 1-6 Schematics of SET operation on 1T-1R device. (a) Schematic circuit diagram of 1T-1R device. Transistor is incorporated in series with the memory cell. (b) SET operation on 1R device. Large electrical stress is applied continuously to the TMO layer during SET operation. (c) SET operation on 1T-1R device. Electrical stress is decreased significantly after SET.

#### ii-2 Heterogeneous TMO stacked structure for the memory cell

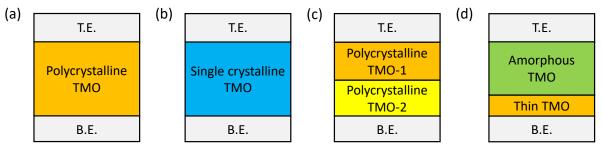

In the early days, filamentary switching devices were composed of single layer of polycrystalline TMO (Figure 1-7(a)) [5, 6, 11-14, 45-48]. The cycle endurance of such devices was poor, because filaments easily increases in domain boundaries (DBs) of the polycrystalline film during the cycling. A simple solution is to apply single crystalline film as the TMO layer, but it is not easy to fabricate a perfect film [43, 49, 73].

Kinoshita et al. proposed heterogeneous polycrystalline TMO stacked cell (Figure 1-7(c)) [68]. In this memory cell, higher isolative initial state and lower switching current were observed. They speculated that number of filament bridging the two electrodes was suppressed in the heterogeneous TMO stacked cell, and relatively stable filaments in the  $TiO_2$  layer acts as an electrode. If we believe this hypothesis, the switching current can be reduced by using single stable filament as the electrode.

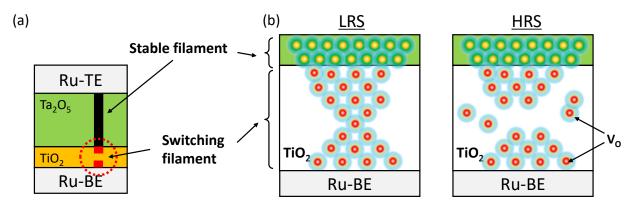

In 2008, Terai et al. proposed a novel cell structure which is composed of amorphous  $Ta_2O_5$  (a- $Ta_2O_5$ )/polycrystalline  $TiO_2$  (p- $TiO_2$ ) stacked layers (Figure 1-7(d)) [74]. They were inspired by two fact, that is,

- The amorphous structure is homogeneous and isotropic, and there is no weak structure like grain boundaries or lattice defects, and

- Single Ta<sub>2</sub>O<sub>5</sub> layer does not show any switching properties.

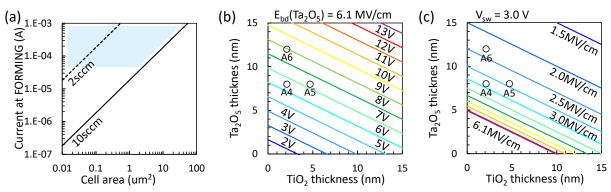

These facts suggest that un-switchable stable conductive filament is formed in the  $a-Ta_2O_5$  layer by FORMING operation, while the  $p-TiO_2$  stacked on  $a-Ta_2O_5$  acts as typical resistance change material. Based on it, they speculated that resistance change phenomena occur in limited area of TiO<sub>2</sub> by apex of the stable filament formed in  $a-Ta_2O_5$  layer. Additional fact that

FORMING voltage in the a-Ta<sub>2</sub>O<sub>5</sub>/p-TiO<sub>2</sub> stack can be controlled by the a-Ta<sub>2</sub>O<sub>5</sub> thickness, and • SET/RESET voltages are enough lower than the FORMING voltage,

suggest that the probability of the stable conductive filament formation in a-Ta<sub>2</sub>O<sub>5</sub> is very small during the cycling [54, 55]. Thus, the RESET failures of both Type-A and Type-B are expected to be significantly reduced in this structure, however highly SET/RESET cycle endurance was not demonstrated in the literature although data retention properties dependence on thermal and electrical stresses were examined.

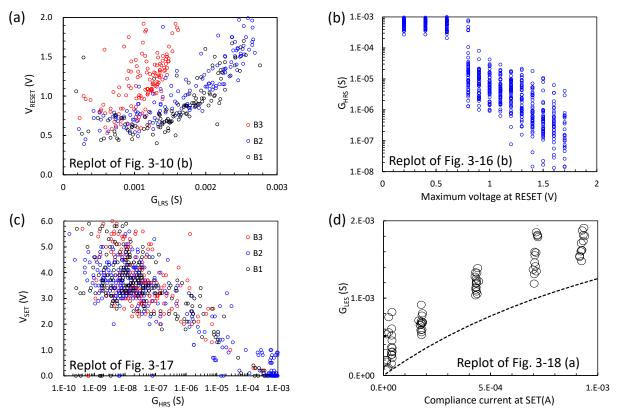

Terai et al. also reported distributions of SET/RESET voltages in the  $Ta_2O_5/TiO_2$  stacked cell, and pointed out that the distributions depend on the HRS/LRS resistances [74]. However, physical origin of the variations was not discussed because detail parametric analysis and in-depth understanding of the states were lacked in the study. It is noted that Terai et al. had reported that the RESET phenomenon was observed only with single polarity like a bipolar operation in the literature [74]. As a result of additional experiments, it has been found that unipolar (nonpolar) operation is possible as long as sufficient current is supplied in RESET operation [75].

Figure 1-7 Schematic cell structures of filamentary switching device. (a) Conventional polycrystalline TMO cell, (b) Single crystalline TMO cell, (c) Heterogeneous polycrystalline TMO stacked cell, (d) Amorphous TMO and ultra-thin polycrystalline TMO stacked cell.

# 1- $4\;$ Purposes of this study

As described in the preceding section, the Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> stacked resistance change device proposed by Terai et al. was expected to have superior performance in the cycle endurance. Although the resistance change phenomena and non-volatility were already reported [74], the resistance change mechanism and the transport mechanism were not discussed. In this study, we examined the transport properties of this device in details to understand following three issues.

## i Resistance change phenomenon in Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> stacked structure

In reference 69, Terai et al. speculated that the resistance change in the  $Ta_2O_5/TiO_2$  stacked device occurs by the redox reaction in  $TiO_2$  layer. However, the model cannot explain the unipolar switching in the device. In this study, we analyze the switching parameters in details to know the mechanism of the resistance change.

## ii Physical model for high resistance state of Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> stacked structure

Microscopic understanding of the HRS is important to discuss the risk of unnecessary filament formation during switching operations and to construct the reliability model for the SET/RESET cycle endurance. In this study, we show the physical model for the HRS based on the detail analysis of the electrical properties of HRS at low temperatures.

#### iii Non-volatile memory performance of Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> stacked structure

Most important function is the SET/RESET cycle endurance for achieving the non-volatile memory application. However SET/RESET cycle endurance in the Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> stacked cell was still not demonstrated although data retention properties dependence on thermal and electrical stresses were examined. In this study, we demonstrate the cycle endurance of Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> stacked cell on 1kbits memory cell array.

## 1-5 Outline of this thesis

This thesis is organized in six chapters. In the Chapter 1, we introduced a background of this study at first. The resistance change phenomena and models for the phenomena were described to give a purpose of this study. In Chapter 2, we explain the experimental details such as sample preparation and electrical evaluation method.

Main subjects are described in Chapters 3, 4 and 5.

In Chapter 3, we investigate the resistance change phenomenon in the  $Ta_2O_5/TiO_2$  stacked cell. As a result, we understand that the resistance change phenomenon is originated from rupture and reconnection of the conductive filament in the  $TiO_2$  layer, which is induced by the joule heating of the conductive filament.

In Chapter 4, we investigate the conduction mechanism of the HRS by analyzing the I-V characteristics at low temperatures, and discuss the detail process of the conduction by comparing the data with a simple conduction model on the picture of the ruptured filament. As a result, we realize that the conduction in the HRS composed of not only the direct tunneling but also the trapassisted tunneling.

In Chapter 5, we demonstrate the memory function of  $Ta_2O_5/TiO_2$  stacked cell on 1kbits memory cell array. From the investigation in chapter 3, we find the SET occurrence is influenced by parameters in RESET operation, and vice versa. We show the decision making process of the operating parameters such as the target LRS/HRS specs and the operating voltages for reducing the risk of unnecessary additional or thicker filament formation at switching operations. We understand that the compliance current ( $I_{COMP}$ ) at SET operation and the pulse height in RESET operation are keys for reliable operation. Then, we show the memory function with optimized switching parameters on 1kbits array. We confirm an excellent cycle endurance with single pulse operation, and a good retention property in 100 degrees C.

In Chapter 6, we summarized this thesis.

# **1-**6 Reference

[1] D. A. Patterson and J. L. Hennessy, "Computer Organization and Design: The Hardware/Software Interface", Fifth edition, *Morgan Kaufmann* (2013).

[2] International technology roadmap for semiconductors,

http://www.semiconductors.org/main/2015\_international\_technology\_roadmap\_for\_semiconductor s\_itrs/, (2016).

[3] D. Ielmini and R. Waser, "Resistive switching from fundamentals of nanoionics redox processes to memristive device applications" *WILEY-VCH* (2016).

[4] W. W. Zhuang, W. Pan, B. D. Ulrich, J. J. Lee, L. Stecker, A. Burmaster, D. R. Evans, S. T. Hsu, M. Tajiri, A. Shimaka, K. Inoue, T. Naka, N. Awaya, K. Sakiyama, Y. Wang, S. Q. Liu, N. J. Wu, and A. Ignatiev, "Novell Colossal Magnetoresistive Thin Film Nonvolatile Resistance Random Access Memory (RRAM)", *IEDM Tech. Dig.*, pp. 193-196 (2002).

[5] I. G. Baek, M. S. Lee, S. Seo, M. J. Lee, D. H. Seo, D.–S. Suh, J. C. Park, S. O. Park, H. S. Kim, I. K. Yoo, U.-In Chung and J. T. Moon, "Highly Scalable Non-volatile Resistive Memory using Simple Binary Oxide Driven by Asymmetric Unipolar Voltage Pulses," *IEDM Tech. Dig.*, pp. 587-590 (2004).

[6] I. G. Baek, D. C. Kim, M. J. Lee, H.-J. Kim, E. K. Yim, M. S. Lee, J. E. Lee, S. E. Ahn, S. Seo, J. H. Lee, J. C. Park, Y. K. Cha, S. O.Park, H. S. Kim, I. K. Yoo, U-In. Chung, J. T. Moon, and B. I. Ryu, "Multi-layer cross-point binary oxide resistive memory (OxRRAM) for post-NAND storage application", *IEDM Tech. Dig.*, pp. 769-762 (2005).

[7] A. Chen, S. Haddad, Y.-C. Wu, T.-N. Fang, Z. Lan, S. Avanzino, S. Pangrle, M. Buynoski, M. Rathor, W. Cai, N. Tripsas, C. Bill, M. VanBuskirk, and M. Taguchi, "Non-Volatile Resistive Switching for Advanced Memory Applications", *IEDM Tech. Dig.*, pp. 746-749 (2005).

[8] T.-N. Fang, S. Kaza, S. Haddad, A. Chen, Y.-C. Wu, Z. Lan, S. Avanzino, D. Liao, C. Gopalan, S. Choi, S. Mahdavi, M. Buynoski, Y. Lin, C. Marrian, C. Bill, M. VanBuskirk and M. Taguchi, "Erase Mechanism for Copper Oxide Resistive Switching Memory Cells with Nickel Electrode", *IEDM Tech. Dig.*, pp. - (2006).

[9] Y. Hosoi, Y. Tamai, T. Ohnishi, K. Ishihara, T. Shibuya, Y. Inoue, S. Yamazaki, T. Nakano, S. Ohnishi, N. Awaya, I. H. Inoue, H. Shima, H. Akinaga, H. Takagi, H. Akoh, and Y. Tokura, "High Speed Unipolar Switching Resistance RAM (RRAM) Technology", *IEDM Tech. Dig.*, pp. 1-4 (2006).

[10] K. Tsunoda, K. Kinoshita, H. Noshiro, Y. Yamazaki, T. Jizuka, Y. Ito, A. Takahashi, A. Okano, Y. Sato, T. Fukano, M. Aoki, and Y. Sugiyama, "Low Power and High Speed Switching of Ti-doped NiO ReRAM under the Unipolar Voltage Source of less than 3 V", *IEDM Tech. Dig.*, pp. 767-770 (2007).

[11] C. Yoshida, K. Tsunoda, H. Noshiro, and Y. Sugiyama, "High speed resistive switching in Pt/TiO<sub>2</sub>/TiN film for nonvolatile memory application", *Appl. Phys. Lett.*, **91**, 223510 (2007).

[12] T. W. Hickmott, "Low-frequency negative resistance in thin anodic oxide films", *J. Appl. Phys.*, **33**, 2669–2682 (1962).

[13] J. F. Gibbons and W. E. Beadle, "Switching properties of thin NiO films", *Solid State Electronics Pergamon Press*, **7**, 785-797 (1964).

[14] F. Abgall, "Switching phenomena in titanium oxide thin films", *Solid-State Electronics Pergamon Press*, **11**, 535-541 (1968).

[15] G. Dearnaley, A. M. Stoneham, and D. V. Morgan, "Electrical phenomena in amorphous oxide films", *Rep. Prog. Phys.*, **33**, 1129–1191 (1970).

[16] Y. Hirose and H. Hirose, "Polarity-dependent memory switching and behavior of Ag dendrite in Ag-photo-doped amorphous As2S3 films", *J. Appl. Phys.*, **47**, 2767–2772 (1976).

[17] D. P. Oxley, "Electroforming, switching and memory effects in oxide thin films", *Electrocomponent Sci. Technol. UK*, **3**, 217–224 (1977).

[18] H. Pagnia and N. Sotnik, "Bistable switching in electroformed metal-insulator-metal devices", *Phys. Status Solidi*, **108**, 11–65 (1988).

[19] A. Asamitsu, Y. Tomioka, H. Kuwahara, and Y. Tokura, "Current switching of resistive states in magnetoresistive manganites", *Nature*, **388**, 50–52 (1997).

[20] M. N. Kozicki, M. Yun, L. Hilt and A. Singh, "Applications of programmable resistance changes in metal-doped chalcogenides", *Pennington NJ USA: Electrochem. Soc.*, 298–309 (1999).

[21] A. Beck, J. G. Bednorz, C. Gerber, C. Rossel and D. Widmer, "Reproducible switching effect in thin oxide films for memory applications", *Appl. Phys. Lett.*, **77**, 139–141 (2000).

[22] D. S. Kim, Y. H. Kim, C. E. Lee, and Y. T. Kim, "Colossal electroresistance mechanism in a Au/Pr0.7Ca0.3MnO3/Pt sandwich structure: evidence for a Mott transition", *Phys. Rev. B*, **74**, 174430 (2006).

[23] L. Esaki, R. B. Laibowitz, and P. J. Stiles, "Polar Switch", IBM Tech. Discl. Bull., 13, 2161 (1971).

[24] H. Kohlstedt, N. A. Pertsev, J. R. Contreras, and R. Waser, "Theoretical current–voltage characteristics of ferroelectric tunnel junctions", *Phys. Rev. B*, **72**, 125341 (2005).

[25] E. Y. Tsymbal, and H. Kohlstedt, "Tunneling across a ferroelectric", Science, 313, 181–183 (2006).

[26] M. J. Rozenberg, I. H. Inoue, and M. J. Sanchez, "Nonvolatile memory with multilevel switching: a basic model", *Phys. Rev. Lett.*, **92**, 178302 (2004).

[27] M. J. Rozenberg, I. H. Inoue, and M. J. Sanchez, "Strong electron correlation effects in nonvolatile electronic memory devices", *Appl. Phys. Lett.*, **88**, 033510 (2006).

[28] I. H. Inoue, M. J. Rozenberg, S. Yasuda, M. J. Sanchez, M. Yamazaki, T. Manago, H. Akinaga, H. Takagi, H. Akoh and Y. Tokura, "Strong electron correlation effects in non-volatile electronic memory devices", *Non-Volatile Memory Technology Symposium Tech. Dig.*, pp. 131-136 (2005).

[29] A. Odagawa, H. Sato, I. H. Inoue, H. Akoh, M. Kawasaki, Y. Tokura, T. Kanno and H. Adachi, "Colossal electroresistance of a Pr<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub> thin film at room temperature", *Phys. Rev. B*, **70**, 224403 (2004). [30] S. Tsui, A. Baikalov, J. Cmaidalka, Y. Y. Sun, Y. Q. Wang, Y. Y. Xue, C. W. Chu, L. Chen and A. J. Jacobson, "Field-induced resistive switching in metal-oxide interfaces", *Appl. Phys. Lett.*, **85**, 317-319 (2004).

[31] T. Harada, I. Ohkubo, K. Tsubouchi, H. Kumigashira, T. Ohnishi, M. Lippmaa, Y. Matsumoto, H. Koinuma, and M. Oshima, "Trap-controlled space-charge-limited current mechanism in resistance switching at Al/Pr<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub> interface", *Appl. Phys. Lett.*, **92**, 222113 (2008).

[32] K. Kamiya, M. Y. Yang, S.-G. Park, B. M.-Köpe, Y. Nishi, M. Niwa, and K. Shiraishi, "ON-OFF switching mechanism of resistive–random–access–memories based on the formation and disruption of oxygen vacancy conducting channels", *Appl. Phys. Lett.*, **100**, 073502 (2012).

[33] B. M.-Köpe, S.-G. Park, H.-D. Lee, Y. Nishi, "First principles calculations of oxygen vacancy-ordering effects in resistance change memory materials incorporating binary transition metal oxides", *J. Mater. Sci.*, **47**, 7498–7514 (2012)

[34] K. Kamiya, M. Y. Yang, T. Nagata, S.-G. Park, B. M.-Köpe, T. Chikyow, K. Yamada, M. Niwa, Y. Nishi, and K. Shiraishi, "Generalized mechanism of the resistance switching in binary-oxide-based resistive random-access memories", *Phys. Rev. B.*, **87**, 155201 (2013).

[35] Y. Watanabe, J. G. Bednorz, A. Bietsch, C. Gerber, D. Widmer, A. Beck, and S. J. Wind, "Resistive switching in metal–ferroelectric–metal junctions", *Appl. Phys. Lett.*, **78**, 3738–3740 (2001).

[36] J. R. Contreras, H. Kohlstedt, U. Poppe, R. Waser, C. Buchal and N. A. Pertsev, "Resistive switching in metal–ferroelectric–metal junctions", *Appl. Phys. Lett.*, **83**, 4595–4597 (2003).

[37] Rickard Fors, Sergey I. Khartsev, and Alexander M. Grishin, "Giant resistance switching in metalinsulator-manganite junctions: Evidence for Mott transition", *Phys. Rev. B*, **71**, 045305 (2005).

[38] A. Sawa, "Resistive switching in transition metal oxides", Mater. Today, 11, 28-36 (2008).

[39] Z. Wei, Y. Kanzawa, K. Arita, Y. Katoh, K. Kawai, S. Muraoka, S. Mitani, S. Fujii, K. Katayama, M.

lijima, T. Mikawa, T. Ninomiya, R. Miyanaga, Y. Kawashima, K. Tsuji, A. Himeno, T. Okada, R. Azuma,

K. Shimakawa, H. Sugaya, and T. Takagi, R. Yasuhara, K. Horiba, H. Kumigashira, and M. Oshima,

"Highly Reliable TaOx ReRAM and Direct Evidence of Redox Reaction Mechanism", IEDM Tech. Dig.,

pp. 293-296 (2008)

[40] Z. Wei, Y. Kanzawa, K. Arita, Y. Katoh, S. Muraoka, S. Mitani, S. Fujii, K.Katayama, T.Ninomiya, and T. Takagi, "Switching Mechanism of TaOx ReRAM", *SSDM Tech. Dig.*, pp1202-1203 (2009).

[41] S. Kim and Y.-K. Choi, "A Comprehensive Study of the Resistive Switching Mechanism in Al/TiOx/TiO2/Al-Structured RRAM", *Electron Devices*, **56**, 3049-3054 (2009).

[42] J. H. Hur, M.-J. Lee, C. B. Lee, Y.-B. Kim, and C.-J. Kim, "Modeling for bipolar resistive memory switching in transition-metal oxides", *Phys. Rev. B*, **82**, 155321 (2010).

[43] B. J. Choi, D. S. Jeong, S. K. Kim, C. Rohde, S. Choi, J. H. Oh, H. J. Kim, C. S. Hwang, K. Szot and R. Waser, B. Reichenberg, and S. Tiedke, "Resistive switching mechanism of TiO<sub>2</sub> thin films grown by atomic-layer deposition" *J. Appl. Phys.*, **98**, 033715 (2005).

[44] K. M. Kim, B. J. Choi, Y. C. Shin, S. Choi, and C. S. Hwang, "Anode-interface localized filamentary mechanism in resistive switching of TiO<sub>2</sub> thin films", *Appl. Phys. Lett.*, **91**, 012907 (2007).

[45] K. Kinoshita, T. Tamura, H. Aso, H. Noshiro, C. Yoshida, M.Aoki, Y. Sugiyama and H. Tanaka, "New Model Proposed for Switching Mechanism of ReRAM", *Non-Volatile Semiconductor Memory Workshop Tech. Dig.*, pp. - (2006).

[46] K. Kinoshita, T. Tamura, M. Aoki, Y. Sugiyama and H. Tanaka, "Bias polarity dependent data retention of resistive random access memory consisting of binary transition metal oxide," *Appl. Phys. Lett.*, **89**, 103509 (2006).

[47] G.-S. Park, X.-S. Li, D.-C. Kim, R.-J. Jung, M.-J. Lee, and S. Seo, "Observation of electric-field induced Ni filament channels in polycrystalline NiO<sub>x</sub> film", *Appl. Phys. Lett.*, **91**, 222103 (2007).

[48] K. M. Kim, B. J. Choi, Y. C. Shin, S. Choi, and C. S. Hwang, "Anode-interface localized filamentary mechanism in resistive switching of TiO<sub>2</sub> thin films" *Appl. Phys. Lett.*, **91** 012907 (2007).

[49] K. M. Kim, B. J. Choi, and C. S. Hwang, "Localized switching mechanism in resistive switching of atomic-layer-deposited TiO<sub>2</sub> thin films", *Appl. Phys. Lett.*, **90**, 242906 (2007).

[50] H. D. Lee, B. M.-Köpe, and Y. Nishi, "Model of metallic filament formation and rupture in NiO for unipolar switching", *Phys. Rev. B*, **81**, 193202 (2010).

[51] J.S. Lee, S.B. Lee, S.H. Chang, L.G. Gao, B.S. Kang, M.-J. Lee, C.J. Kim, T.W. Noh, and B. Kahng, "Scaling Theory for Unipolar Resistance Switching", *Phys. Rev. Lett.* **105**, 205701 (2010).

[52] G. Bersuker, A. Korkin, L. Fonseca, A. Safonov, A. Bagatur'yants, and H. R. Huff, "The role of localized states in the degradation of thin gate oxides", *Microelectronic Engineering*, **69**, 118–129 (2003).

[53] M. A. Alam, "A Study of Soft and Hard Breakdown-Part I: Analysis of Statistical Percolation Conductance", *Electron Devices*, **49**, 232-238 (2002). "A Study of Soft and Hard Breakdown-Part II: Principles of Area, Thickness, and Voltage Scaling", *Electron Devices*, **49**, 239-246 (2002).

[54] J. Sune, "New physics-based analytic approach to the thin oxide breakdown statistics", *Elec. Dev. Lett.*, **22**, 296-298 (2001).

[55] E. Wu and J. Sune, "Power-law voltage acceleration: a key element for ultra-thin gate oxide reliability", *Microelectronics reliability*, **45**, 1809-1834 (2005).

[56] D.-H. Kwon, K. M. Kim, J. H. Jang, J. M. Jeon, M. H. Lee, G. H. Kim, X.-S. Li, G.-S. Park, B. Lee, S. Han, M. Kim, and C. S. Hwang, "Atomic structure of conducting nano-filaments in TiO<sub>2</sub> resistive switching memory", *Nature Nanotechnology*, **5**, 148 (2010).

[57] J. P. Strachan, M. D. Pickett, J. J. Yang, S. Aloni, A. L. David Kilcoyne, G. Medeiros-Ribeiro, and R. Stanley Williams, "Direct identification of the conducting channels in a functioning memristive device", *Advanced Materials*, **22**, 3573 (2010).

[58] K. Szot M. Rogala, W. Speier, Z. Klusek, A. Beshmehn, and R. Waser, "TiO<sub>2</sub>-a prototypical memristive material", *Nanotechnology*, **22**, 254001 (2011).

[59] F. Miao, J. P. Strachan, J. J. Yang, M. –X. Zhang, I. Goldfarb, A. C. Torrezan, P. Eschbach, R. D. Kelley, G. Medeiros-Ribeiro, and R. S. Williams, "Anatomy of a Nanoscale Conduction Channel Reveals the Mechanism of a High-Performance Memristor", *Advanced Materials*, **23**, 5633 (2011).

[60] D. C. Kim, S. Seo, et al., "Electrical observations of filamentary conductions for the resistive memory switching in NiO films", *Appl. Phys. Lett.*, **88**, 202102 (2006).

[61] H. Shima, F. Takano, H. Akinaga, Y. Tamai, I. H. Inoue, H. Takagi, "Resistance switching in the metal deficient-type oxides: NiO and CoO", *Appl. Phys. Lett.*, **91**, 012901 (2007).

[62] Y. Sato, K. Kinoshita, M. Aoki, and Y. Sugiyama, "Consideration of switching mechanism of binary metal oxide resistive junctions using a thermal reaction model", *Appl. Phys. Lett.*, **90**, 033503 (2007)

[63] U. Russo, D. Jelmini, C. Cagli, A. L. Lacaita, S. Spigat, C. Wiemert, M. Peregot and M. Fanciullit, "Conductive-filament switching analysis and self-accelerated thermal dissolution model for reset in NiO-based RRAM", *IEDM Tech. Dig.*, pp.775-778 (2007)

[64] C. Cagli, D. Ielmini, F. Nardi and A. L. Lacaita, "Evidence for threshold switching in the set process of NiO-based RRAM and physical modeling for set, reset, retention and disturb prediction", *IEDM Tech. Dig.*, pp.301-304 (2008).

[65] C. Cagli, F. Nardi, and D. Ielmini, "Modeling of Set/Reset Operations in NiO-Based Resistive-Switching Memory Devices", *Electron Devices*, **56**, 1712-1720 (2009).

[66] R. Degraeve, P.H. Roussel, L. Goux, D. Wouters, J. Kittl, L. Altimime, M. Jurczak, and G. Groeseneken, "Generic learning of TDDB applied to RRAM for improved understanding of conduction and switching mechanism through multiple filaments", *IEDM Tech. Dig.*, pp. 633-636 (2010).

[67] M. A. Alam, "Statistically independent soft-breakdown redefine oxide reliability specifications", *IEDM Tech. Dig.*, pp. 151-154 (2002).

[68] K. Kinoshita, T. Tamura, M. Aoki, Y. Sugiyama and H. Tanaka, "Lowering the Switching Current of Resistance Random Access Memory Using a Hetero Junction Structure Consisting of Transition Metal Oxides", *Jpn. J. Appl. Phys.*, **45**, L991–L994 (2006).

[69] C. Rohde, B. J. Choi, D. S. Jeong, S. Choi, J.-S. Zhao, and C. S. Hwang, "Identification of a determining parameter for resistive switching of TiO<sub>2</sub> thin films", *Appl. Phys. Lett.*, **86**, 262907 (2005).

[70] K. Kinoshita, T. Tamura, M. Aoki, Y. Sugiyama and H. Tanaka, "Lowering the Switching Current of Resistance Random Access Memory Using a Hetero Junction Structure Consisting of Transition Metal Oxides", *Jpn. J. Appl. Phys.*, **45**, L991-994 (2006).

[71] K. Kinoshita, K. Tsunoda, Y. Sato, H. Noshiro, S. Yagaki, M. Aoki, and Y. Sugiyama, "Reduction in the reset current in a resistive random access memory consisting of NiOx brought about by reducing a parasitic capacitance", *Appl. Phys. Lett.*, **93**, 033506 (2008).

[72] H. Shima, F. Takano, H. Muramatsu, H. Akinaga, Y. Tamai, I. H. Inoue, and H. Takagi, "Voltage polarity dependent low-power and high-speed resistance switching in CoO resistance random access memory with Ta electrode", *Appl. Phys. Lett.*, **93**, 113504 (2008).

[73] K. M. Kim, B. J. Choi, B. W. Koo, S. Choi, D. S. Jeong, and C. S. Hwang, "Resistive Switching in Pt/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub>/Ru Stacked Structures", *Electrochemical and solid-state Letters*, **9**, G343-G346 (2006).

[74] M. Terai, S. Kotsuji, H. Hada, N. Iguchi, T. Ichihashi, and S. Fujieda, "Effect of ReRAM-Stack Asymmetry on Read Disturb Immunity", *IRPS Tech. Dig.*, pp. 134-138 (2009).

[75] In the early papers [70], they reported that the RESET phenomenon was observed only at the voltage with polarity opposite to the SET voltage like a bipolar operation. Later, however, it became clear that unipolar operation in either polarity is also possible as long as sufficient current is supplied in RESET operation (see Figure 2-8(b)).

## Chapter 2. Experimental

In this chapter, experimental techniques and methods are described. At first, formation methods of stoichiometric TMO layers, which is important to achieve the filamentary switching, are explained. After that, device structure and switching operation method are shown briefly. Finally, measurement systems and evaluated samples are summarized.

## 2-1 Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> stacked memory cell

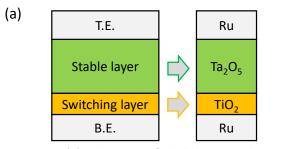

Tantalum oxide  $(Ta_2O_5)/T$ itanium oxide  $(TiO_2)$  stacked memory cells, the concept of which was proposed by M. Terai et al. [1, 2], were used for our study. When the stacked structure is operated as the filamentary switching device, the  $Ta_2O_5$  layer and the  $TiO_2$  layer are expected to act as the stable layer and the switching layer, respectively [1]. As we wrote in section 1-2, the non-stoichiometric  $TaO_x$ and  $TiO_x$  show another type, i.e., the interface type resistance change [3, 4]. So, stoichiometric composition for both layers is very important to achieve the filament type memory cell (Figure 2-1(a)). In this study, we optimized the deposition process conditions for achieving stoichiometric composition. The results of composition and crystallinity characterization of both layers are given in this section. The cell integration and process optimization were done on 8-inch processing R&D line at Device platforms research laboratory of NEC Corporation.

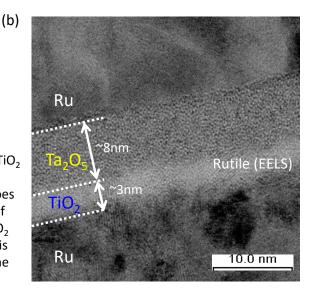

Figure 2-1 (a) Schematic of the bilayer stack concept.  $TiO_2$  is the most promising switching material. In contrast, conductive filament formed in stoichiometric  $Ta_2O_5$  does not switch to HRS [1]. (b) Cross-sectional TEM image of Ru/Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub>/Ru stack provided by Terai et al. [1].  $TiO_2$  layer was deposited by using reactive sputtering. In this study, this type of samples were used for examining the transport properties in Chapter 4.

## i TiO<sub>2</sub> layer

In reference 1, Terai et al. used a reactive sputtering method to make  $TiO_2$  layer on bottom electrode. The deposited  $TiO_2$  they obtained is polycrystalline with rutile structure, which was confirmed by the electron diffraction and the electron energy loss spectroscopy (EELS) [1], and the grain size is larger than  $TiO_2$  layer thickness as shown in the Figure 2-1(b). This means that grain

boundaries penetrate the layer. As it is widely accepted that grain boundaries behave high mobility path for oxygen ion, unintended degradation of the resistive state can easily occur in such films [5].

In our study, we chose an alternative method to form the  $TiO_2$  layer on bottom electrode, that is, deposition of thin titanium film followed by the oxidation [2].

At first, the ruthenium bottom electrode 20 nm thick was sputtered on a Si substrate. Then, thin titanium layer was deposited physically on bottom electrode by sputtering a titanium target. Deposition rate was about 0.04 nm/sec, that was evaluated from process time for thicker film formation as shown in Figure 2-2(a). Continuous thin film was obtained with low Ar-gas flow (20 sccm) and dc-power (0.5 kW) conditions at room temperature.

0

<sup>4</sup>Depth (nm)

10 12

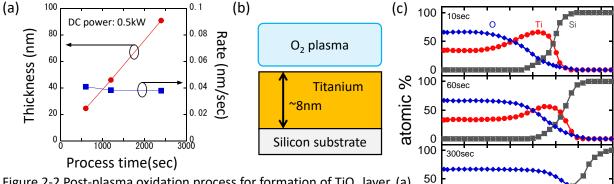

Figure 2-2 Post-plasma oxidation process for formation of TiO<sub>2</sub> layer. (a) Calculation of Ti deposition rate for thin film formation. (b) Schematic of O<sub>2</sub>-plasma exposure in post-oxidation process. Three samples were prepared with different exposure times (10s, 60s and 300s) in preliminary experiment. (c) Depth profile of  $TiO_2$  composition which was investigated by RBS technique.

Post-oxidation was done by using plasma-enhanced method at 250 degrees C. In order to get stoichiometric TiO<sub>2</sub>, we made preliminary experiments, and optimum  $O_2$ -plasma exposure time was determined with fixed dc-power and O<sub>2</sub>-gas flow (2800sccm). Three sample were prepared with different exposure times (10 s, 60 s and 300 s) to 8nm-thickness titanium film on silicon substrate as shown in Figure 2-2(b), and the depth profile of  $TiO_2$  composition was investigated by High Resolution Rutherford Backscattering Spectrometry (HR-RBS). The results are shown in Figure 2-2(c). Atomic O/Ti ratio near the surface is almost 2, which means that TiO<sub>2</sub> layer was formed at the surface by  $O_2$ -plasma exposure. The Ti $O_2$  layer thickness increased with the exposure time, and after 300 s exposure TiO<sub>2</sub> layer reached 8nm thick, which means that 5 nm-titanium region from the surface was fully oxidized in this case.

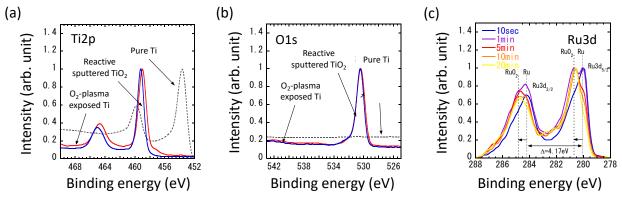

Stoichiometry of O<sub>2</sub>-plasma exposed 5 nm-titanium on ruthenium was investigated by X-ray photoelectron spectroscopy (XPS). Figure 2-3(a) shows the spectrum near the Ti-2P peaks. We found that Ti-2p peaks was shifted to higher binding energy by the  $O_2$ -plasma exposure. Position of the peaks is similar to that of reactive sputtered TiO<sub>2</sub>. The difference between plasma-oxidized TiO<sub>2</sub> and reactive-sputtered TiO<sub>2</sub> is existence of small shoulder near 457eV. This means that TiO<sub>2-x</sub> exists

in interface between fully oxidized TiO<sub>2</sub> layer and ruthenium bottom electrode when O<sub>2</sub>-plasma exposure time is not long enough.

It should be noted that surplus longer exposure time also causes oxidation of the ruthenium bottom electrode. Figure 2-3(c) shows XPS spectrum near the Ru-3d peak from the O<sub>2</sub>-plasma exposed sample which was processed to 2 nm-thick titanium film on ruthenium bottom electrode. Additional peaks caused by forming RuO<sub>2</sub> to the interface between TiO<sub>2</sub> layer and ruthenium bottom electrode were observed in case with longer process time condition than 1 min.

Figure 2-3 XPS spectra from  $O_2$ -plasma exposed 5nm-titanium on ruthenium [2] (a) Spectrum near the Ti-2p peaks (Red solid line:  $O_2$ -plasma exposed titanium, Blue solid line: Reactive sputtered Ti $O_2$ , Black dashed line: Pure titanium). (b) Spectrum near the O-1s peak. (c) Spectra near the Ru-3d peaks. The spectra is different in the oxidation time.

### ii Ta<sub>2</sub>O<sub>5</sub> layer

$Ta_2O_5$  layer was deposited on  $TiO_2$  layer by RF sputtering using  $Ta_2O_5$  target. Process conditions such as  $Ar/O_2$  flow ratio and temperature were tuned for achieving isolative  $Ta_2O_5$ .

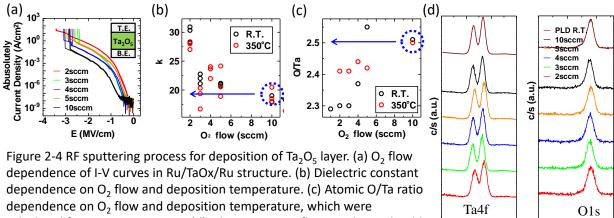

calculated from XPS spectrum in (d). The 10 sccm- $O_2$  flow condition should be used for achieving the stoichiometric Ta<sub>2</sub>O<sub>5</sub> film which is expected to have low leakage property[3].

35 30 25 20 540 535 530 Binding energy (eV) Binding energy (eV)

Figure 2-4(a) shows the leakage current as a function of the applied electric field for five films made at different  $O_2$  flow rates. We understand that high oxygen flow rate gives preferable isolation. We also measured the dielectric constant and XPS spectrum of the films, from which atomic O/Ta ratio was determined (Figure 2-4(b) ~ (d)). We found desirable parameters were obtained with small cellto-cell variation in higher oxygen flow condition. From these results, we decided the Ar/O<sub>2</sub> flow ratio to 40/10sccm with 2.0kW-rf-power. The temperature was aligned to maximum temperature in the integration process (350 degrees C). Deposition rate of Ta<sub>2</sub>O<sub>5</sub> is about 0.15nm/sec.

## **2-** 2 Device structure and switching operation

Based on the conductions obtained in the previous section, we fabricated  $Ru/Ta_2O_5/TiO_2/Ru$  stacked memory devices. Control of current through the memory cell at the switching operations is very important to achieve reproducible switching in the filamentary switching device [6], and we employed 1T-1R type device structure mentioned in section 1-3. In this section, we show the structure of the integrated 1T-1R memory device at first. After that, operation methods of 1T-1R type device are described for both unipolar and bipolar switching.

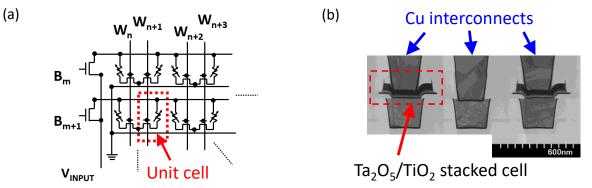

## i Memory cell integration to 1T-1R type device

Ru/Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub>/Ru stacked memory cell was integrated to the 1T-1R type devices on 6-inch wafer with conventional 0.35um-node CMOS process. An n-channel field-effect transistor (n-FET) is incorporated in series with a memory cell. Cross-sectional schematic of the device is shown in Figure 2-5(a) [1, 2]. Memory cell was placed directly on the drain contact to reduce the parasitic capacitance. Effective memory cell size is defined by top electrode area.

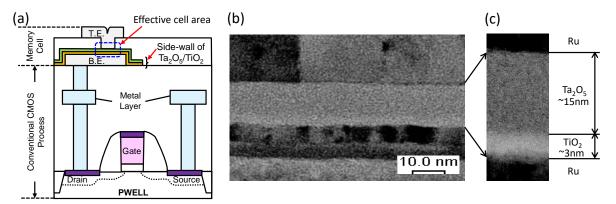

Figure 2-5 (a) Cross-sectional schematic of integrated 1T-1R device. Memory cell module was placed just above drain contact for reducing the parasitic capacitance. Effective memory cell size is defined by the top electrode area. (b) Cross-sectional TEM image of Ru/Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub>/Ru stacked memory cell. (c) Magnified TEM image shows that both Ta<sub>2</sub>O<sub>5</sub> layer and TiO<sub>2</sub> layer are amorphous.

Cross-sectional TEM image of the memory cell is shown in Figure 2-5(b) and (c). It is composed of a ruthenium bottom electrode (BE), a 3nm-thick titanium oxide layer  $(TiO_2)$ , a 15nm-thick tantalum

oxide layer ( $Ta_2O_5$ ), and a ruthenium top electrode (TE). The TiO<sub>2</sub> layer was formed by oxidizing 2nm-thick titanium metal by O<sub>2</sub>-plasma. The maximum temperature in memory cell integration process is sufficiently lower than the crystallization temperature of  $Ta_2O_5$  and TiO<sub>2</sub> [2], and we ascertain the both layers are amorphous.

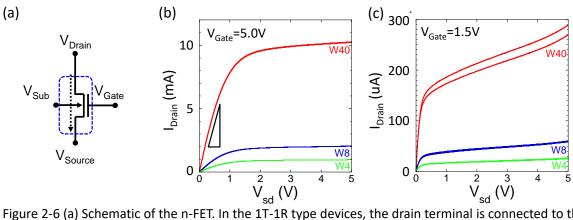

Figure 2-6 (a) Schematic of the n-FET. In the 1T-1R type devices, the drain terminal is connected to the the bottom electrode of the memory cell as shown in the Figure 2-5 (a). (b) Drain current dependence on bias voltage between source and drain with some channel width variations in case of  $V_{Gate} = 5.0$ V. (c) Drain current dependence on bias voltage between source and drain with some channel width variations in case of  $V_{Gate} = 1.5$ V.

Figure 2-6(b) and (c) show the electrical characteristics of the integrated transistors. Drain current as a function of bias voltage between source and drain is given for three devices with different channel width (W). The saturation current and the ON-conductance is proportional to the channel width as summarized in Table 2-1. As we will see in the next chapter, RESET characteristics and apparent LRS resistance are influenced by the ON-resistance of the FET. Thus, we have to consider the effects in analysis of the resistance change parameters.

| Name | W(um) | Saturation current | ON-resistance | Saturation current | Series resistance in |

|------|-------|--------------------|---------------|--------------------|----------------------|

|      |       | @Vg=5.0V           | @Vg=5.0V      | @Vg=1.5V           | 1T-1R type device    |

| T1   | 4     | 1mA                | $1000\Omega$  | 30μΑ               |                      |

| T2   | 8     | 2mA                | $500\Omega$   | 60μΑ               | ~28Ω                 |

| Т3   | 40    | 10mA               | $100\Omega$   | 300µA              |                      |

| Table 2-1 Device parame | eters of series | transistors |

|-------------------------|-----------------|-------------|

|-------------------------|-----------------|-------------|

*Note:* These values come from transistor only devices. Series resistance in 1T-1R type device is estimated by adding contact resistance to the ON-resistance.

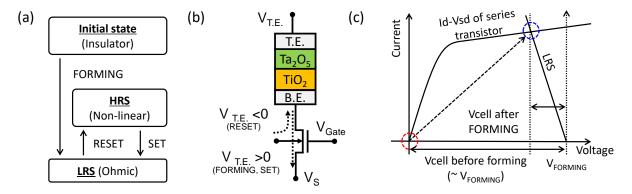

## ii Unipolar and bipolar switching operation

The Ru/Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub>/Ru stacked memory cell is a unipolar-type device, and basically it works in either polarity of voltage. As for our 1T-1R device, however, FORMING and SET operations must be done with positive bias, i.e., to apply a positive voltage to the top Ru electrode while the source of the

FET being grounded. In this case, the current flowing the cell is kept smaller than the saturation current of the FET even after the sudden resistance drop takes place. If we apply negative voltage to the top electrode, however, a larger current can flow directly from the Si substrate, because it is grounded to stabilize the FET characteristics (see Figure 2-7(b)).

Figure 2-7 (a) Switching operation flow. (b) Schematic of 1T-1R type device configuration. Current compliance is possible only in positive drain bias condition. Drain current includes the current from the substrate in negative drain bias condition. (c) Schematic load curve of 1T-1R type device at FORMING and SET operations.

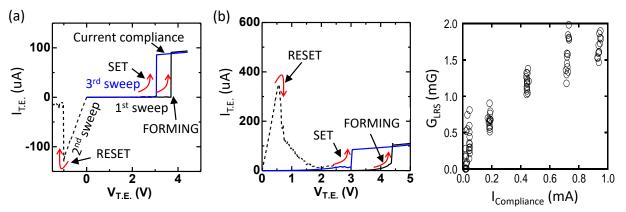

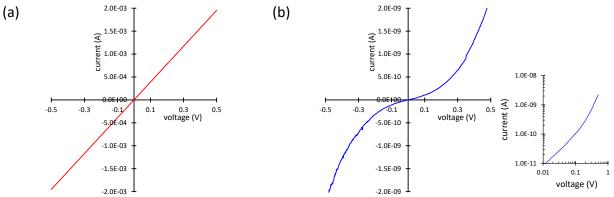

In our early experiments [1], we did the measurement by bipolar operation. Figure 2-8(a) shows an example of the bipolar operation with dc sweep method. Black solid line shows the FORMING: applying positive voltage to the top electrode causes the resistance of the memory cell to decrease suddenly at around 4 V. At this time, the current flowing the cell is bounded by the saturation current of the FET. Black dashed line shows the RESET: applying negative voltage to the top electrode causes the resistance of the memory cell to increase suddenly at around 1 V. This high resistive state defines the "off-state" or "high resistance state (HRS)". Blue solid line shows the SET: applying positive voltage to the top electrode caused the resistance of the memory cell to decrease suddenly at around 3 V. At this time, current is limited by FET in common with the FORMING operation. This low resistive state defines the "on-state" or "low resistance state (LRS)". The limit current in FORMING and SET operation is called the "compliance current". The compliance current is controllable by the gate voltage.

In this research, we mainly used the unipolar operation. Figure 2-8(b) shows an example of the unipolar operation with dc sweep method. Black solid line shows the FORMING: applying positive voltage causes a sudden resistance drop at around 4 V. After that, the current is limited to the compliance current. Black dashed line shows the RESET: applying positive voltage to the top electrode with Vg=5V causes a jump to the HRS at around 1 V. Generally, in RESET operation we have to apply the current larger than the compliance current at SET operation. To do this, we set the gate voltage at Vg = 5 V, where the saturation current of the FET is much higher than compliance current at SET. Blue solid line shows the SET: applying positive voltage caused a jump to the LRS at around 3 V. The compliance current is an important control parameter.

Figure 2-8(c) shows compliance current dependence of LRS conductance in our 1T-1R type devices. LRS conductance can be changed by the compliance current. This means that the compliance current can control the conductance of single conductive filament formed in the  $Ta_2O_5/TiO_2$  stacked cell. By using this controlling method, we investigate resistance change characteristics dependence on the LRS conductance in Chapter 3.

Figure 2-8 (a) Example of bipolar switching operation. (b) Example of unipolar switching operation. (c) Compliance current dependence of LRS conductance.

#### 2-3 Measurement setup and Samples

In this section, the evaluation environments and the samples are described.

#### i Evaluation systems and measurement setup

Three type of measurement systems were used in this study.

Single cell level evaluations at and above the room temperature were done on a wafer by semiautomatic probing system (S300, CascadeMicrotech) with semiconductor parametric analyzer (4156C, Agilent). A heater installed in the wafer stage enabled the sample temperature to be varied from 300K–400K. Switching phenomena and basic electrical properties of the memory cells were investigated by this system.

Single cell level evaluations at low temperature were done on a diced chip which was mounted on cryogenic system. Cryogenic system (Oxford) consists of a low boil-off helium cryostat with a liquid nitrogen reservoir and a variable temperature insert (VTI). A heat exchange coil at the base of the VTI tail controls the temperature in the VTI. A heater installed on the heat exchanger enables the sample temperature to be varied from 2.0–300 K.

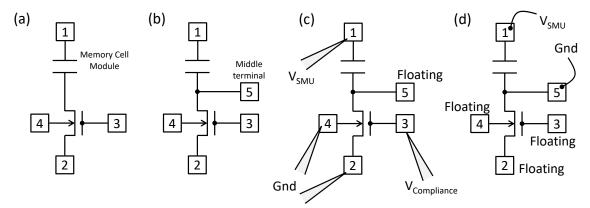

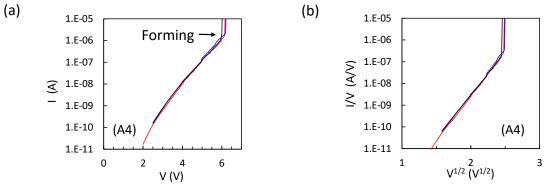

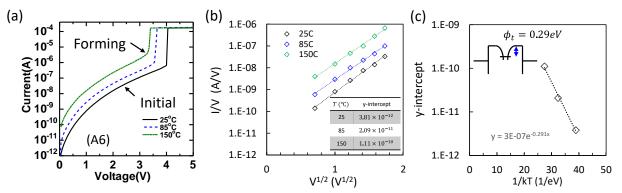

For the measurement at low temperatures, we used a special 1T-1R type device which has middle terminal on the node between the n-FET and the memory cell as shown in Figure 2-8(b). This configuration satisfies two necessary conditions: to control the current through the memory cell in the switching operation (Figure 2-8(c)), and to measure just the electrical properties of the memory cell free from that of transistor (Figure 2-8(d)). In this study, digital multimeters (34401A, Agilent)

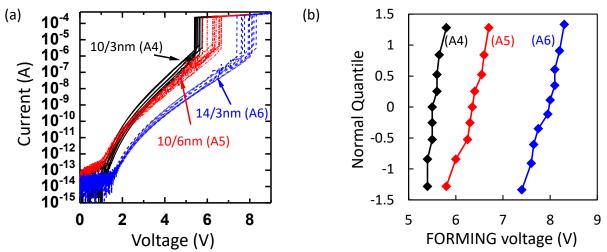

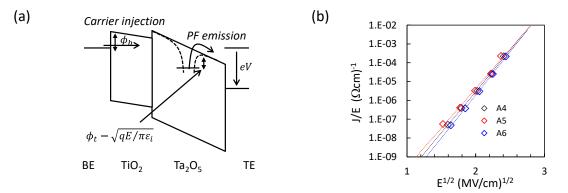

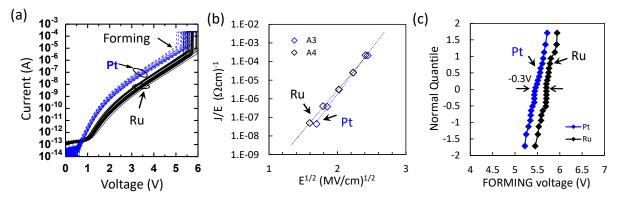

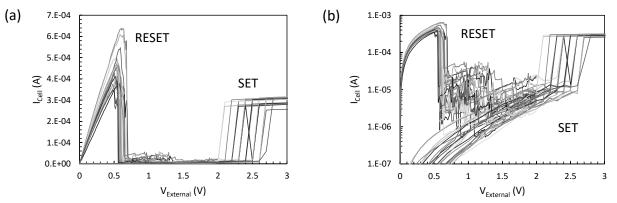

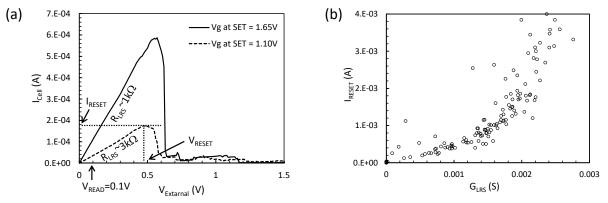

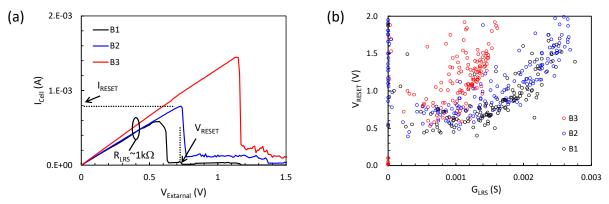

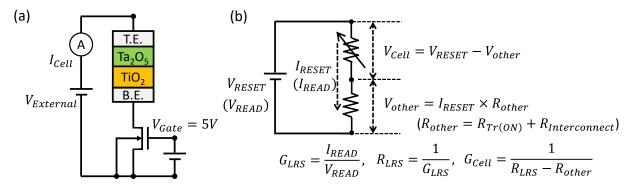

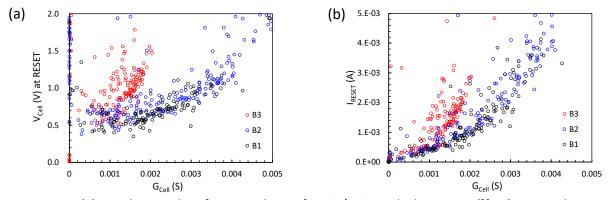

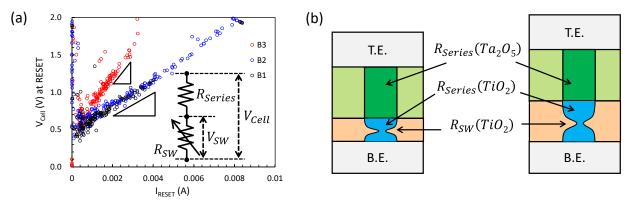

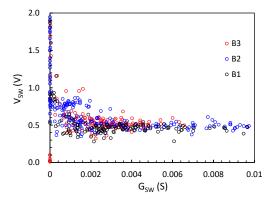

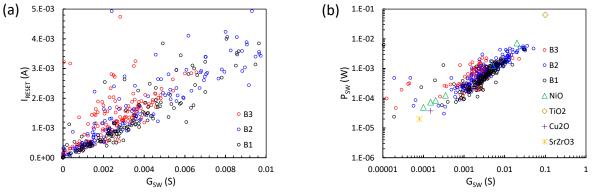

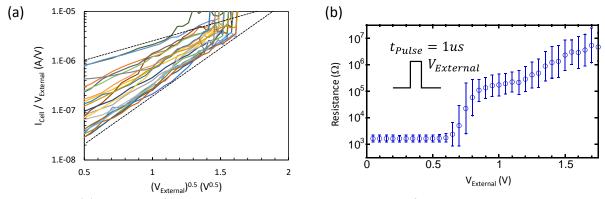

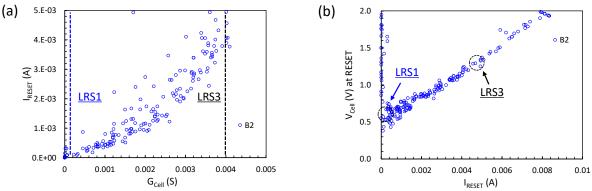

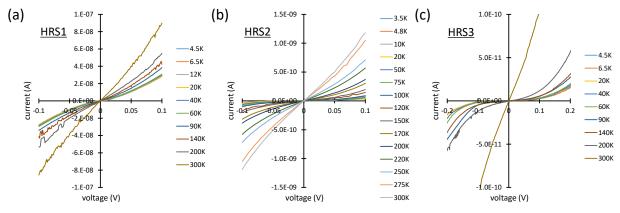

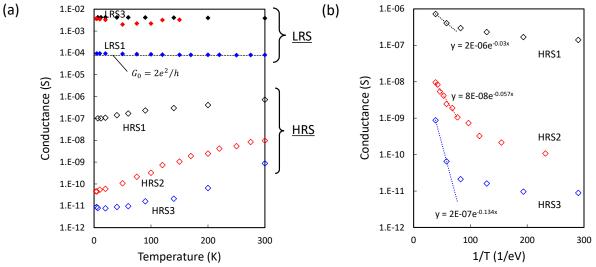

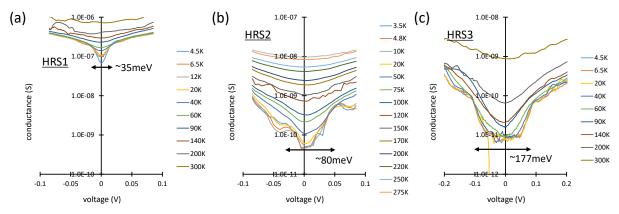

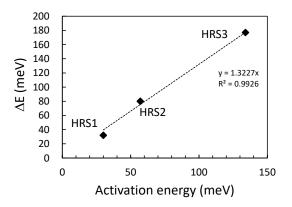

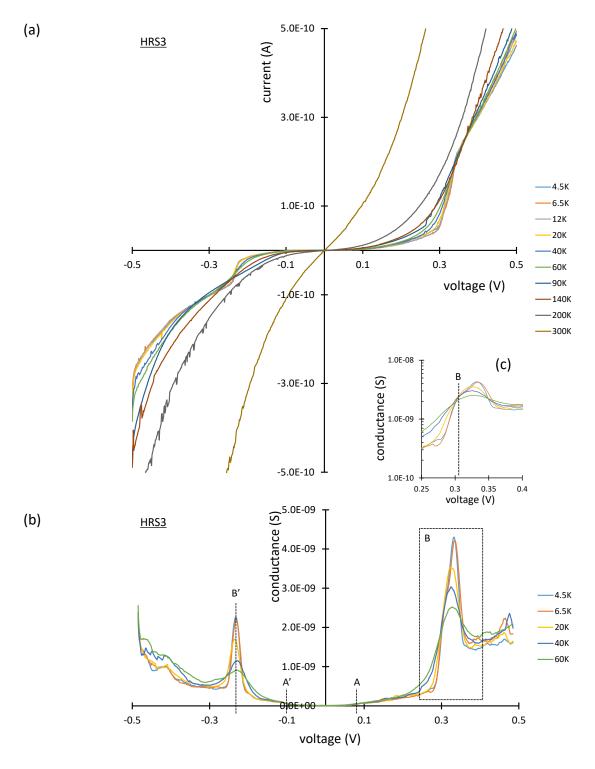

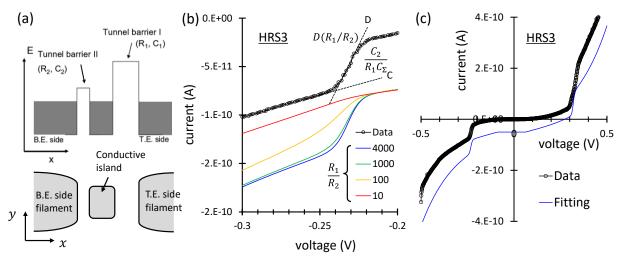

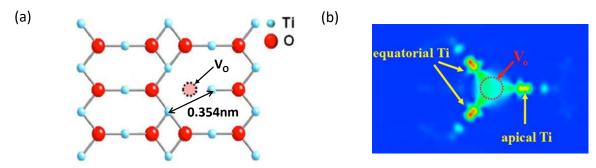

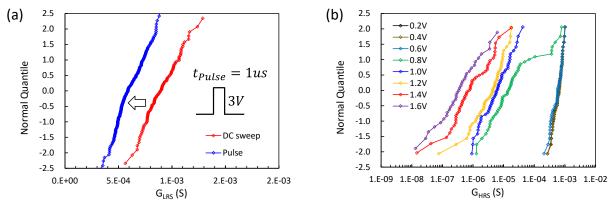

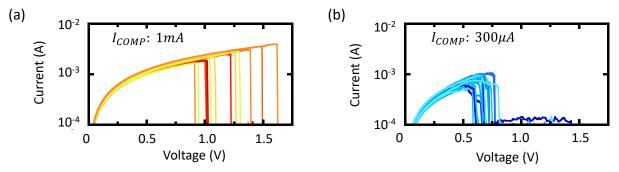

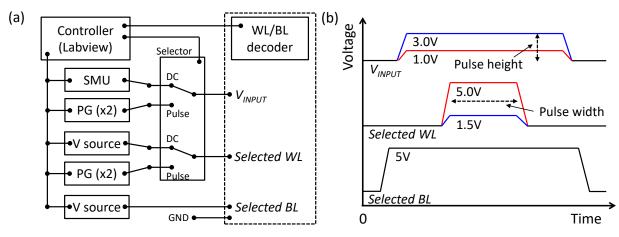

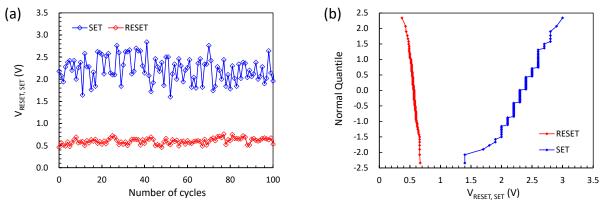

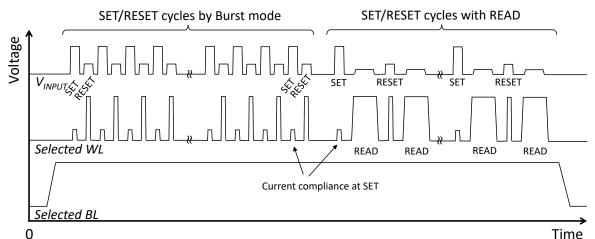

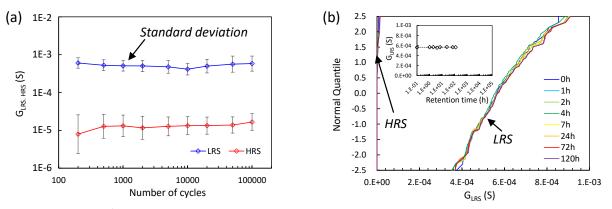

and semiconductor parametric analyzer (4156C, Agilent) were used. It is noted that controllability of the current through the memory cell is poor in this special 1T-1R type device, because this device has large parasitic capacitance associated with the middle terminal. When we want to control the LRS resistance, normal 1T-1R device should be used (Figure 2-8(a)).