198

## 工学博士学位論文

客 上川井 良木郎氏 田和 年 月 日

「高速計算機ハードウェア 設計支援システムの研究」

上川井 良太郎

昭和63年12月

# 目 次

| 1 | 序論 |

|---|----|

|   | 1 | . 1 | はじ  | めに   | •••• | • • • •     | • • • | ••         | ••    | • • • | • •   | • • •   | • • • | ••    | ••  | ••  | • • | ••  | ••  | ••  | • • | • • | ••  | • • | ••  | 1          |

|---|---|-----|-----|------|------|-------------|-------|------------|-------|-------|-------|---------|-------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------|

|   | 1 |     |     | 究の目  |      |             |       |            |       |       |       |         |       |       |     |     |     |     |     |     |     |     |     |     |     |            |

|   |   | 1.2 | . 1 | 高速計  | 算機   | <b>'</b> \- | ドゥ    | ェ          | ア     | の‡    | 妖男    | 医       |       | · • • | ٠.  | • • | • • | • • | • • | ٠.  | ٠.  |     | • • |     |     | 1          |

|   |   |     |     | 高速計  |      |             |       |            |       |       |       |         |       |       |     |     |     |     |     |     |     |     |     |     |     |            |

|   |   | 1.2 | . 3 | 設計の  | ための  | の支払         | 爰シ    | ス          | テ     | ム     | ٠     | • • •   | • • • | ••    | ••• | ••  | ••  | • • | ••  | ••  | ••  | ••  | ٠.  | ••  | ••  | 5          |

|   | 1 | . 3 | 従来  | の研究  | との関  | 係           | ••    | ••         | ••    | •••   | · • • | • • •   |       | · • • | ••  | ••  | ••  | ••  | ••  | ••  | ••  | ••  | ••  | ••  | ••  | 7          |

| 2 | • | 電気  | 特性  | 解析シ  | ステム  |             |       |            |       |       |       |         |       |       |     |     |     |     |     |     |     |     |     |     |     |            |

|   |   |     |     | 特性解  |      |             |       |            |       |       |       |         |       |       |     |     |     |     |     |     |     |     |     |     |     |            |

|   |   |     |     | はじめ  |      |             |       |            |       |       |       |         |       |       |     |     |     |     |     |     |     |     |     |     |     |            |

|   |   | 2.1 | . 2 | 髙速化  | ・高智  | 好度(         | との    | 間          | 題,    | 点     | ٠     |         | • •   | • •   | ٠.  | • • | ••  | • • | • • | ٠.  | • • | • • | ••  | ٠.  | • • | 9          |

|   |   | 2.1 | . 3 | 電気特  | 性解析  | 斤シン         | ステ    | ム          | ^(    | のヨ    | 医叉    | <b></b> | 項     | ĺ     | • • | • • | ••  | • • | ••  | • • | ••  | ••  | • • | ••  | ••  | 11         |

|   | 2 | . 2 | 問題  | の定式  | 化。   | • • • •     | • • • | ••         | ••    |       | ٠.    | • • •   | ••    | ••    | ••  | ••  | ••  | ••  | ••  | ••  | ••  | ••  | ••  | ••  | ••  | 13         |

|   |   |     |     | パシタ  |      |             |       |            |       |       |       |         |       |       |     |     |     |     |     |     |     |     |     |     |     |            |

|   |   |     |     | 基本方  |      |             |       |            |       |       |       |         |       |       |     |     |     |     |     |     |     |     |     |     |     |            |

|   |   | 2.3 | . 2 | 大規模  | 問題。  | へのi         | 適用    | に          | 向     | け゛    | C (   | ある      | (良    | Į     | ••  | ••  | • • | • • | • • | ٠.  | • • | • • | • • | ٠.  | • • | 24         |

|   |   | 2.3 | . 3 | 計算結  | 果の色  | 列·          | • • • | • •        | ••    | • • • | • •   | • • •   | • • • | ••    | • • | ••  | ••  | • • | • • | • • | • • | • • | ••  | • • | • • | 26         |

|   |   |     |     | ダクタ: |      |             |       |            |       |       |       |         |       |       |     |     |     |     |     |     |     |     |     |     |     |            |

|   |   | 2.4 | . 1 | 基本方  | 式・   | • • • •     | • • • | ••         | • • • |       | ٠.    | • • •   | • • • | • • • | • • | • • | ••  | • • | • • | • • | • • | • • | • • | • • | • • | 30         |

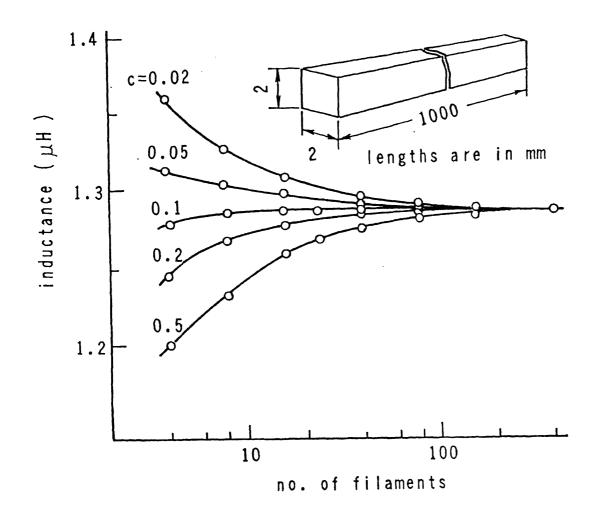

|   |   | 2.4 | . 2 | 太さ 0 | のフィ  | ィラコ         | メン    | ۲          | のま    | 採月    | Ħ     | • •     |       | • •   | • • | • • | ••  | • • | ••  | • • | • • | ٠.  | • • | • • | ٠.  | 32         |

|   |   | 2.4 | . 3 | 複数導  | 体セク  | ブメン         | ノト    | の          | イ:    | ンタ    | y ?   | ノタ      | ン     | ゚ス    | の   | 合   | 成   |     | • • | • • | • • | ٠.  | • • | ٠.  | ٠.  | 34         |

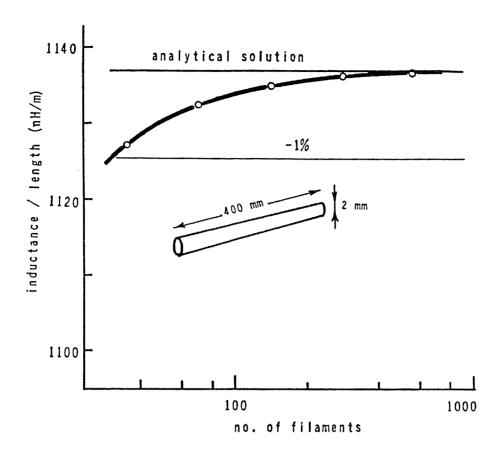

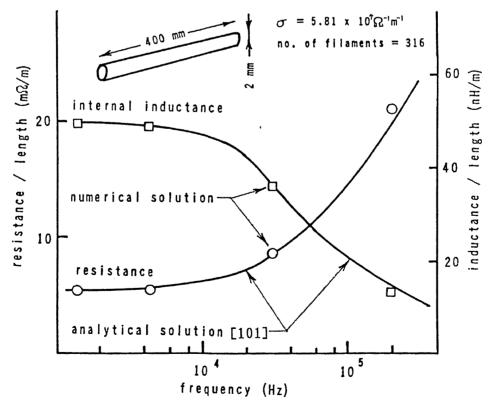

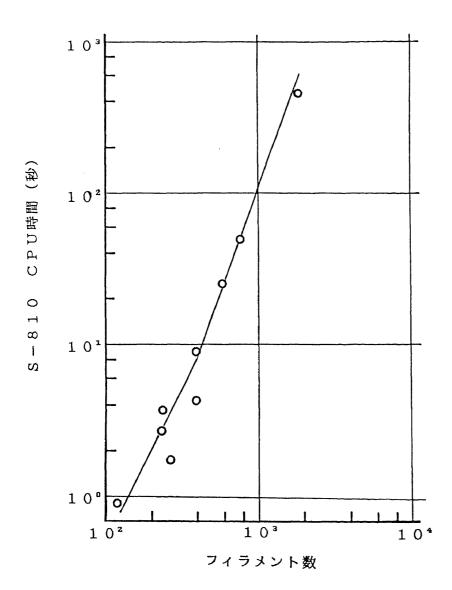

|   |   | 2.4 | . 4 | 計算結  | 果の色  | <b>列</b> ·  | • • • | • •        | ••    | • • • | • •   | • • •   | • • • | ••    | ••  | ••  | ••  | • • | ••  | • • | ••  | ••  | ••  | ••  | ••  | 37         |

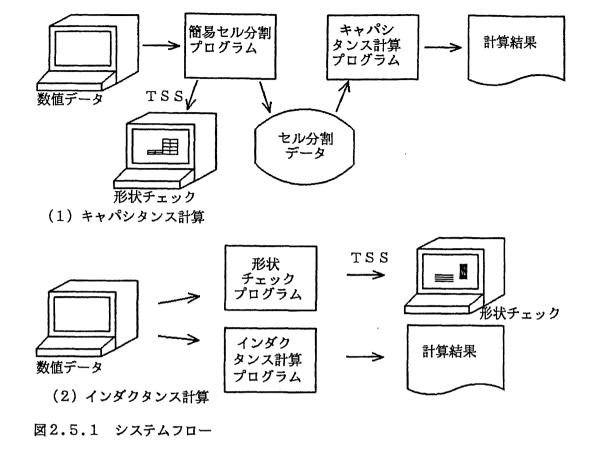

|   | 2 | . 5 | デー  | タの入れ | 出力   |             | • • • | ••         | •••   |       | ٠.    | • • •   | •••   | ••    | ••  | ••  | ••• | ••  | ••  | ••  | ••  | • • | ••  | ••  | ••  | 38         |

|   | 2 | . 6 | 実装  | 系の電台 | 気特性  | 解析          | ~0    | ي<br>المار | は用    | ŀ     |       |         |       |       |     | • • | ••  | ٠.  | • • | ٠.  |     |     | • • |     |     | <u>4</u> 1 |

| 参 | 考 | 文献·  |              |    |               |         | ٠.           |     |       |                 |      | ••                  |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       | . 82  |

|---|---|------|--------------|----|---------------|---------|--------------|-----|-------|-----------------|------|---------------------|----------|-------|----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|-----|-------|-------|-----|-------|-------|-------|

| 謝 | 辞 | •••• |              |    | •••           | • • •   | ••           | ••• | • • • | • • •           | ••   | ••                  | •••      |       | • • •    | ••• | • •   | • • •                                                                                                                                                                                                                                                                                                                                  | •• | •••   | • • | • • • | •••   | ٠.  |       |       | • 81  |

| 5 | • | 付舅   | ţ            | •• | •••           | · • • • | •••          | ••• |       | • • •           | ••   | ••                  | •••      | • • • | •••      | ••• | • •   | • • •                                                                                                                                                                                                                                                                                                                                  | •• | •••   | • • | • •   | • • • | ••  | •••   | •••   | • 78  |

| 4 | • | 結論   | i            | •• | •••           | • • •   | ••           | ••• | • • • | • • •           | ••   | ••                  | •••      |       | • • •    | ••• | · • • | • • •                                                                                                                                                                                                                                                                                                                                  | •• | •••   |     | • • • |       | ••  | •••   | · • • | • 75  |

|   |   | 3.3  |              |    |               |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   | 3.3  |              |    |               |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   | 3.3  |              |    |               |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   | 3.3  |              |    |               | 11形     |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   | 3 | . 3  |              |    |               |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   |      |              |    |               |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   | 3.2  | . 5          | 5  | ク             | リテ      | ٠,           | 力。  | ルン    | ۲۶              | 発    | 見:                  | 法        |       | • • •    |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       | • 64  |

|   |   | 3.2  |              |    | 配約            |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   | 3.2  | . 3          |    |               |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   | 3.2  | . 2          | 2  |               | 層処      |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   | 3.2  |              |    |               | 本機      |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   | 3 | . 2  | パ            | ス・ | ディ            | ν.      | イラ           | F x | . ツ   | ク:              | シン   | スラ                  | ニム       | の:    | 特質       | 女   |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       | ••  | •••   |       | • 51  |

|   |   | 3.1  | . 2          | 2  | パ             | スデ      | ٠,           | レ   | イヲ    | £x              | ッ    | ク                   | シ        | ステ    | ٠<br>٨   | ^(  | の多    | ままり ままり ままり ままり ままり はい かいしゅう はいしゅう はいしゅう かいしゅう しゅう かいしゅう かいしゅう しゅう かいしゅう しゅう かいしゅう しゅう かいしゅう しゅう しゅう しゅう しゅう しゅう しゅう しゅう しゅう しゅう | 事  | 項     | •   | • • • | • • • | ••  | •••   |       | • 51  |

|   |   | 3.1  | 1            | L  | タ・            | イミ      | ン            | グ   | 設計    | 1上              | : の  | 間                   | 題,       | 点     | ••       | • • | • • • |                                                                                                                                                                                                                                                                                                                                        | •• | • • • | • • |       |       | • • | • • • |       | • 50  |

|   | 3 | . 1  |              |    |               |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

| 3 | • | パフ   | くデ           | 1  | レイ            | 'チ:     | エッ           | ック  | シ     | ス・              | テム   | 4                   |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   | 2.6  | ) <b>.</b> č | 5  | <i>}\c\</i> ) | 用货      | ı <b>)</b> — | 3   | 4     | ミシ              | ′ユ   |                     | ע :      | コネ    | <i>9</i> | タト  | 司氏    | 手切                                                                                                                                                                                                                                                                                                                                     | 替  | Ι.    | 1 ) | ス     | ••    | ••  | •••   | •••   | • 47  |

|   |   | 2.6  |              |    |               |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       |       |

|   |   | 2.6  |              |    | 応力            |         |              |     |       |                 |      |                     |          |       |          |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       | • 41  |

|   |   | 9 6  | 1            |    | 15.           | FFI Ind | ď            | 1   | 1.    | <b>⇒ &gt;</b> ¥ | : 女白 | $\boldsymbol{\Phi}$ | <b>4</b> | ≅ Ad  | - 44     |     |       |                                                                                                                                                                                                                                                                                                                                        |    |       |     |       |       |     |       |       | . A 1 |

## 記号の説明

- A (1)ベクトルポテンシャル, (2)接続行列

- B 磁束密度

- C。 伝送線の長さ当りキャパシタンス

- C。 伝送線相互間の長さ当りキャパシタンス

- Cab 容量行列要素

- D 電束密度

- D: フィラメントi 断面の幾何学的平均距離

- E 電界

- E\* 等価真空系での電界

- G 表面電荷法の係数行列

- Gij 表面電荷法の係数行列の(i,j)要素

- g Gの逆行列

- H 磁界

- Hii 表面電荷法の係数行列の(i,j)要素(i=誘電体境界セル)

- I フィラメント電流のベクトル

- Ii フィラメントiを流れる電流

- In 各ノードに外部から流入する電流からなるベクトル

- is 各導体セグメントを流れる電流からなるベクトル

- J (1)電流密度, (2)フィラメント電流のベクトル(付録)

- L フィラメントインダクタンス行列

- Lii フィラメントインダクタンス行列の(i,j)要素

- L。 伝送線の長さ当りインダクタンス

- Lm 伝送線間の長さ当り相互インダクタンス

- L<sub>H</sub> 導体セグメントのインダクタンス行列

- li フィラメントiの長さ

- n 法線ベクトル

- q 電荷密度

- q\* 等価真空系での電荷密度

- q<sub>i</sub> セルi内の電荷

- q : 全電荷密度

- q<sub>t</sub>\* 等価真空系での全電荷密度

- Ri フィラメントiの抵抗

- r 位置ベクトル

- ria セル重心座標

- S: (1)セルiの面積,(2)フィラメントiの断面積

- t 時間

- \* 行列の転置

- T13 容量・誘導係数行列要素

- ∇<sub>N</sub> 各ノードの電位からなるベクトル

- vs 各導体セグメント両端間の電圧からなるベクトル

- 1 成分が全て1であるベクトル

- ε 誘電率

- ε。 真空の誘電率

- ε, 比誘電率

- μ 透磁率

- σ 導電率

- σoi セルiの導電率

- Φ。 a 点のスカラーポテンシャル

- $\Phi_{ba} = \Phi_b \Phi_a$

- Ψ 磁束

- φ 電束

- ω 角周波数

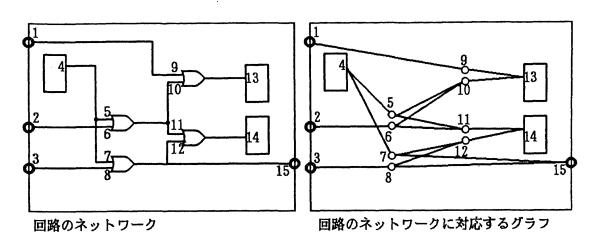

#### 1.1 はじめに

汎用計算機のハードウェア性能の進歩は著しく、約10年に1桁の割合で処理速度の向上が続けられてきている。これを維持するため各メーカーでは世代ごとにその時点で可能な最先端のテクノロジーを動員して開発努力を傾注してきた。関連する技術分野、開発内容の主なものをあげると、(1)論理、メモリLSIの高速化、高集積化、(2)配線基板、コネクタ、LSIパッケージ等実装部品の高密度化、大規模化、(3)回路を高密度に実装するための冷却能力の向上がある。計算機のハードウェア開発においてはこれら個々の要素技術はもちろん、これらの技術を統合してハードウェア系にまとめあげる、いわばハードウェアシステム技術が重要な役割を持っている。この分野では従来、過去の経験や勘にたよらざるを得ない部分が多く、合理的な判断を積み重ねて設計を進めてゆくのが困難な状況にあった。しかし各要素技術が進歩をとげ、それぞれの限界と思われる点に近づいてくるに従って、このハードウェアシステム技術の分野での複雑で高度な設計・判断が必要になり、これを的確に行うための設計支援システムの重要性が高まってきた。

本論文は筆者が昭和43年以来主にこの計算機ハードウェアシステム技術の設計支援の分野で4世代にわたって大型汎用計算機の開発に参画してきた過程で、特に計算機の高速化のための必要性から構想をまとめ、開発・実用化した設計支援システムとして、(1)ハードウェア基本構造の設計時に、電気的なノイズとディレイを予測するための「電気特性解析システム」

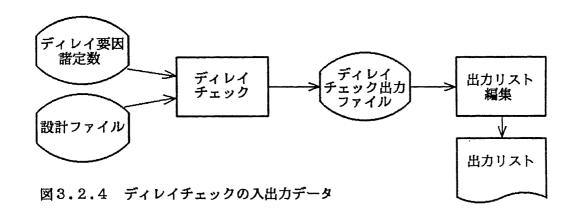

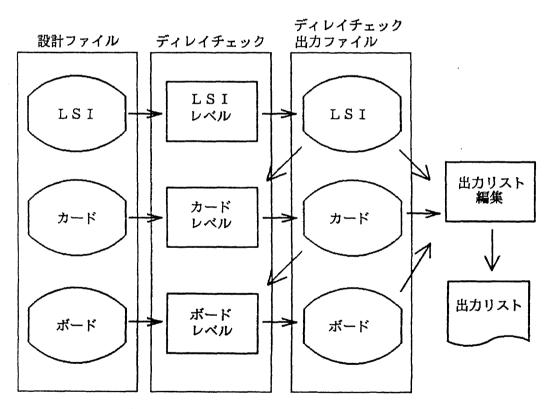

(2) ディレイが目標マシンサイクル時間から決まる制限値を越えているような論理のパスを発見する「パスディレイチェックシステム」

について,要求されていた課題と,その実現のために新しく開発した技術内容,実際の設計への適用結果をまとめたものである。

#### 1.2 本研究の目的と概要

## 1.2.1 高速計算機ハードウェアの概要

髙速計算機ハードウェア系は以下に述べるような物理的特徴を持っている。

- (1)多数の論理回路とそれらをつなぐ複雑な配線からなる。

- (2)回路間の距離を短縮するためできる限り髙密度に実装している。

- (3) 短い立上り時間のパルス信号を使う。

- (4) それぞれの論理回路は高速性への要求から消費電力が高く,高度の冷却技術を駆使 して発生する熱を除去している。

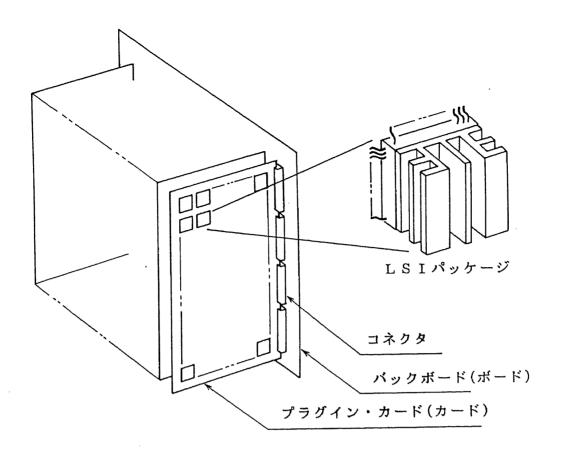

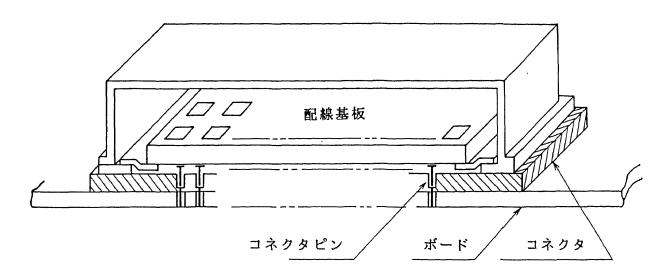

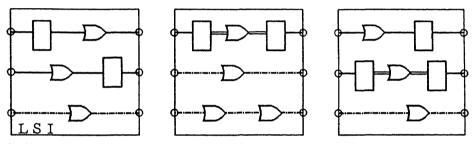

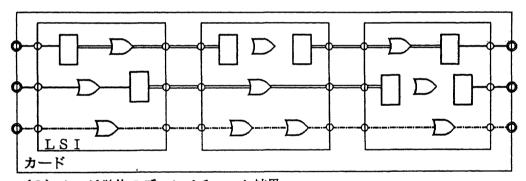

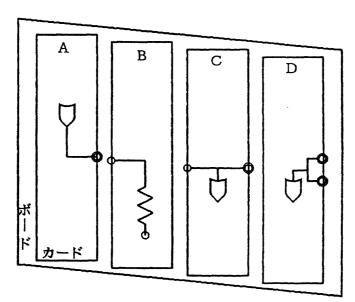

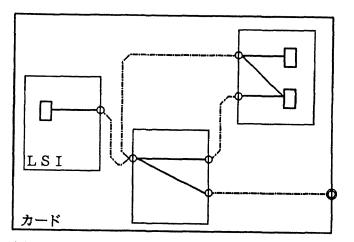

図1.2.1は代表的な高速計算機ハードウェア構造の例であり、特に高速の処理を行う CPUの部分を示している[1]~[6]。論理回路は図に示すようなLSIパッケージに収容 されプラグイン・カード (以後単にカードと呼ぶことにする) に接続されている。1つの LSIパッケージは200~5000ゲートのLSI 1チップを収容している。性能 への要求から論理の並列度が高く、この規模のLSIでは100~200本のピンが必要 である。論理LSIは多品種を短期間に開発しなければならないのでゲートアレイ方式を とるのが普通である[7],[8]。

ゲートアレイ方式というのは半導体のアクティブ素子は全品種共通に作り、それらを組合せて単位回路(2入力norゲート、フリップフロップ等)を構成するための素子間相互配線と、それら単位回路間をつなぐ配線のみが品種ごとに異なるようにした設計・製造方式である。この方式によれば回路特性が均一で製造のターンアラウンドタイム、コストが少なくてすむうえ、設計作業は(1)チップを細分した標準的な領域に所要の単位回路に対応する既設計の配線パターンを配置し、(2)単位回路を論理設計結果に基づいて接続する配線経路を決めるのみでよい。従ってちょうどSSI(小規模集積回路)を搭載したカードと同じように設計することが可能である。

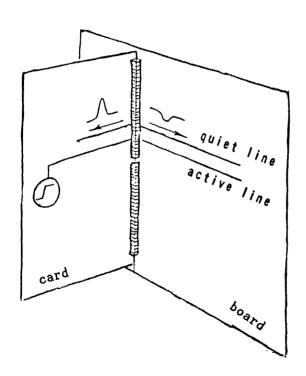

LSIを搭載するカードは高密度化のため、信号配線と電源供給用の導体層を多数設けた基板を使う[9]。LSIの場合と同様、部品搭載位置、電源供給パターンなど高度に規格化されており、品種ごとに異なるのは各実装位置に搭載するLSIの品種とそれらをつなぐ信号配線のみになっている。カードの間を接続する印刷回路基板であるバックボード(以下単にボードと呼ぶ)についても同様である。1枚のカードに収容する論理の量が増加するに従い、カードとボードの間をつなぐコネクタは高密度、多ピンのものが必要になる[10]。

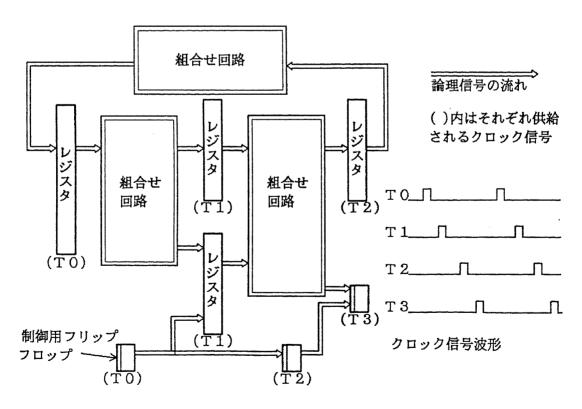

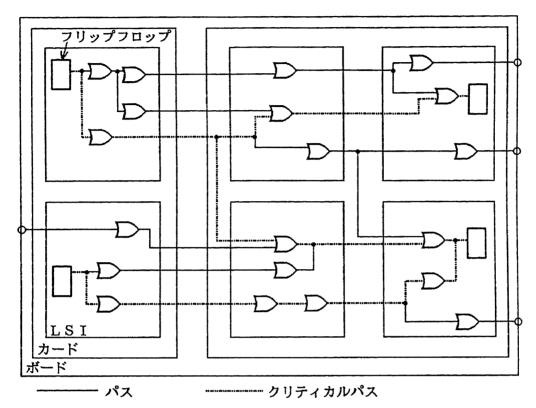

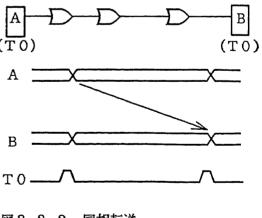

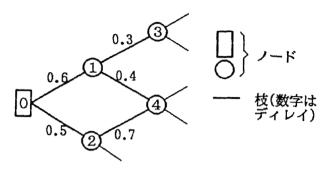

計算機内のタイミングの制御は一定周期で位相の異なる数種類のクロック信号を使って行う。すなわちレジスタや制御用のフリップフロップは、図1.2.2に示すように全てこれらのクロック信号に同期して動作するようになっている。通常クロック信号の周期をマシンサイクル時間という。

計算機のハードウェア性能は各命令の実行時間をその命令の出現頻度で重み付けして平均した平均命令実行時間で表しているが、これはマシンサイクル時間を使って次のように表すことができる。

平均命令実行時間=(マシンサイクル時間)×(平均命令実行サイクル数)

(1.2.1)

平均命令実行サイクル数は1つの命令を平均的に何マシンサイクルかけて(クロック周期の何倍かけて)実行するかを示す量で、論理方式の性能の目安といえる。これに対しマシンサイクル時間は、回路、実装系などの狭義のハードウェアとしての性能を示すものである。本論文の主題の設計支援システムはこの狭義のハードウェア性能向上、すなわちマシンサイクル時間の短縮を目的とするもので、以後本論文でハードウェア、または

図1.2.1 高速計算機ハードウェア構造の例

図1.2.2 計算機内のタイミング制御概念図

ハードウェア性能といった場合は特にことわらないかぎり狭義のそれを指すものとする。

#### 1.2.2 高速計算機ハードウェアの設計

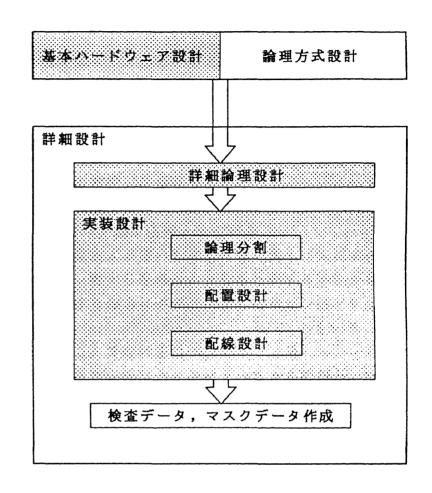

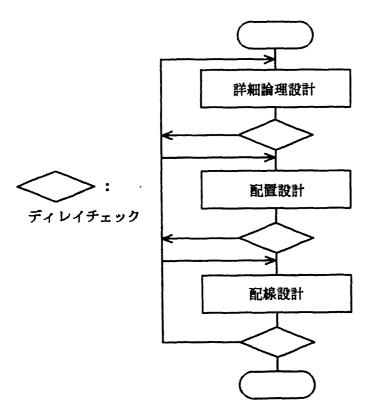

計算機ハードウェアの設計は(1)基本ハードウェア設計,(2)詳細設計,の2つのフェーズに分けることができる(図1.2.3参照)。

これらの項目の決定に当っては,一方では部品の製造・ 検査・保守技術,コスト,安

図1.2.3 計算機ハードウェア設計の流れ

全性を考慮し、一方では予想される量の論理回路を収容して目標マシンサイクル時間を実現することを保証できなければならない。また電気的なノイズが許容できる範囲内であること、消費した熱量を除去できる冷却手段が準備されていることが必要である。この時点での設計を誤ると製品の性能や信頼性の低下をまねくことになる。とは言え設計期間は限られているので、過去の実績データに基づいた確実な設計を行い、さらに試作により確認するのが普通である。ところが高いハードウェア性能を得るためにはこの時点で設計の選択の幅を広くとれることが必要で、このためには問題となりそうな点は漏れなく試作に盛り込んで実測、確認できるよう、対象となる事象の十分な理解と、設計結果を予測する能力が必要とされる。

詳細設計のフェーズには論理方式の詳細論理への展開,LSI,カード等の部品への分割,ピン割り付け,搭載する部品の配置設計,部品間の配線経路の設計,さらに部品のテ

スタにインプットする検査データの作成,部品製造のためのマスクデータ作成が含まれる。このフェーズでの設計作業では既に決まっている枠組み,ルールに合わせての同一種類の多数の部品の開発を,誤りなく短期間に行う必要がある。特にLSIの高集積化が進み,いったん完成してしまえば修正が大変なので,論理,実装設計の不良は早期に発見して対策を講じることが必要で,このため設計の検証が重要な課題になっている。

#### 1.2.3 設計のための支援システム

## (1) 基本ハードウェア設計

このフェーズの設計作業を大きく分類すると、(a)回路素子およびLSIの設計,

(b) 部品のサイズ,ピン数等の規模の設計 (c) 回路,実装系の電気特性を考慮した形状,スタンダードの設計,(d)冷却系の設計,に分けられる。

このうち (a) のための支援システムとしては,デバイスシミュレータ[11],[12],回路 シミュレータ[13],[14]が一般に実用化され,広く活用されている。

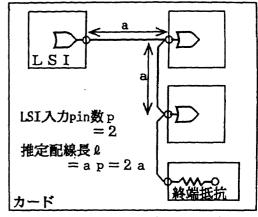

(b) では過去の統計データに基づく推定式が用いられている。例えば配線基板の層数を決定するには搭載するLSIの信号ピン数から配線長の分布を予測する手法が報告されている[15]~[20]。また論理回路を収容する部品に必要な入出力信号ピン数PについてはP=aG (1.2.2)

で推定できることが知られている[21]。ここでGはその部品のゲート数, a, r は定数で 経験的に決められる。これらのためには従来の計算機の設計データから配線長, ゲート数, ピン数などのデータを抽出するプログラムが使われる。このようにして合理的に実装規模 を決定することが可能になっている。

- (c) については、本研究の着手時点では実装系でのノイズや遅延時間計算のため主として伝送線のパラメータを計算するためのプログラムが利用されていた。また寄生容量、インダクタンスの効果については電磁気学の公式を使ってC, Lを計算し、回路シミュレータで過渡応答を求めるのが一般的であった。

- (d)のためには固体中の熱伝導,流体境界層での熱伝達の有限要素法によるシミュレータが広く使われている[22]。

このように基本ハードウェア設計のフェーズでは自然法則,工場の生産設備,論理方式等多様な要素を考慮して,ハードウェア系の枠組を創出するもので,対象範囲が広範で,設計の自由度が極めて高いのが特徴である。このため設計そのものは自動化が不可能で,設計に必要な情報を得るためのシミュレータと過去の統計データの利用が主体である。対象は広範囲にわたっており,設計支援システムの特性としては一般的,汎用的であることが要求される。

## (2) 詳細設計

このフェーズは大きく分類すると (a) 詳細論理設計, (b) 実装設計, (c) 検査データ,マスクデータ作成に分けられる。

- (a) はごく限られた適用を除いては自動化は難しく,設計者が設計内容をチェックするための論理シミュレータが使われている。

- (b) については高性能の自動配置,自動配線プログラムがあり人間に代わってほぼ100%自動的に実装位置,配線経路を決定することができるが,その設計結果がマシンサイクル時間の目標値を満たすものであるかどうかまでは保証できないのが現状である。すなわち配線経路の設計のしかたによっては,1マシンサイクルの間に転送すべきデータのパスのディレイが大きくなりすぎてしまうことがありうる。これについては設計結果がマシンサイクル時間の目標値を満たしているかどうかをチェックしながら設計を進めるのが現実的なアプローチである。

- (c) については比較的自動化が進んでおり、特にマスクデータの作成は機械的な処理 内容で、最も早く自動化された分野である。

このように詳細設計のフェーズでは決まった枠の中で一定のルールに従った設計を行う ので自動化が進んでいるが、詳細論理および論理のパスのディレイについては人手による 設計に頼っている。

## (3) 高速化を目的とした設計支援

上に述べたとおり設計自動化技術の進歩により計算機設計の多くの部分が自動化され、またはシミュレート可能になってきているが、開発時点でのハードウェア要素技術を最大限に利用して高性能の計算機を設計することが強く要求される状況になるに従い、今までの設計支援システムでは不十分な点が明らかとなってきた。

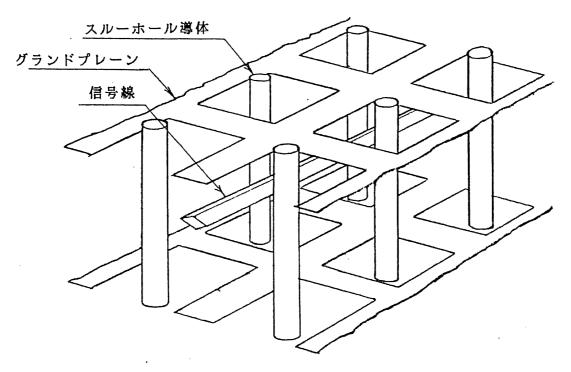

基本ハードウェア設計のフェーズではパルス信号の立上り時間の短縮と実装系の高密度化に伴って、ノイズと伝送線の電気特性の正確な予測技術なしには(1)(c)の分野での質の高い設計は望めなくなってきた。第2章に述べるように伝送線やその接続部の電磁気現象は電気回路の応答として求めることができる。すなわちこれらの導体構造からキャパシタンス、インダクタンスを計算すれば、既存の回路解析プログラムを使って過渡応答を求めることが可能である。そこで配線基板、LSI接続部、コネクタ等のように多数の導体が接近して存在するような任意の3次元構造について、形状からキャパシタンス、インダクタンスを計算できる3次元電気特性解析システムの開発がハードウェア性能向上の必須条件となってきた[23]~[26]。これについての詳細は第2章に述べる。

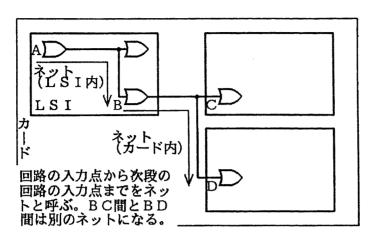

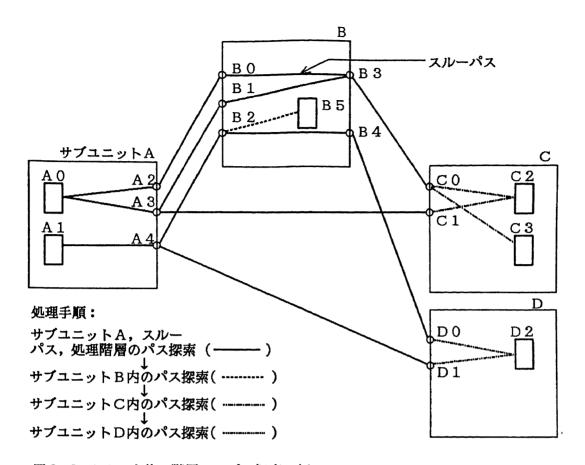

詳細設計のフェーズでは論理規模の拡大と、回路の高速化に伴う実装ディレイの全体に占める比率の増加により、CPU内に無数に存在するフリップフロップ間の論理のパスのディレイがそれぞれ目標とするマシンサイクル時間を満足するか否かの判断が極めて困難になってきている。ディレイが目標値をオーバーしたパスの存在は、完成した計算機の性能を大きく悪化させることになるので、設計の段階でこれを全て発見し、対策を講じることが必要であるが、従来の論理シミュレーションでこれを発見することは困難である。そこで詳細論理、実装設計データからこれを全て自動的にチェックできるような設計支援システムの存在が、詳細設計の質を決定的に左右することになる。この目的で開発したパスディレイチェックシステム[27]~[31]について第3章に述べる。

電気特性解析システムとパスディレイチェックシステムは,ともにハードウェア性能向上を目的とした設計支援システムであるが,使用されるフェーズ,目的の相違からその性格も異なっている。電気特性解析システムは電磁気学,数値解析の専門知識のない一般の設計者が多様な対象に適用できるよう,汎用性とフレキシビリティが要求されるのに対し,パスディレイチェックシステムは既に決まっている実装の枠組みのデータ,設計データ等を最大限に利用し,設計の早い時期に,効率よく正確なチェックができることが要求される。

#### 1.3 従来の研究との関係

#### (1)電気特性解析システム

回路実装系の電気特性を計算によって求める試みとしては、伝送線の長さ当りキャパシタンスの2次元計算が早くから実用化されていた。これに基づいて特性インピーダンスを求める種々の近似公式や[32]~[34]、複数の信号配線の間のクロストークノイズ計算法[35]~[39]が報告されている。伝送線の接続部等2次元計算では不可能な所についてはキャパシタンスとインダクタンスを何らかの方法で3次元的に計算し、回路解析プログラム[13][14]を使って過渡応答を求めることが必要である[40]。3次元形状のキャパシタンス計算については表面電荷法による計算が発表されていたが、ごく単純な形状のものに限られていた[41][42]。その後計算機の性能向上と数値解析技術の進歩とともに、差分法[43]~[45]、有限要素法[46][47]、表面電荷法[48][49]による3次元の容量計算が可能になり、特に[49]では表面電荷法で係数行列の次数が小さくてすむよう、ポテンシャルの計算時にセル内平均するSilvesterの手法[50]の有効性が述べられている。本研究では基本アルゴリズムとして上記[48][50]の方法を採用しているが、計算しようとしている対象の形状が複雑なので、この方式に改良を加えて約6倍の高速化を達成している。

一方上に述べた伝送線の接続部等では過渡電流がどの様なループを構成するか明確でなかったり、ループの途中の導体と他の部分との間のキャパシタンスが無視できなかったりするため、ループを構成する導体の一部分に対して定義される部分インダクタンスを通常のインダクタンスとみなして回路シミュレーションを行うことが提案されている[51][52]。パルスの立上り時間の間に電磁波が進む距離にくらべ十分小さな寸法では、通常のインダクタからなる回路については電磁気現象は電気回路論の問題としてとして取り扱えることが示されているが[53][54]、本論文ではこれを拡張し、部分インダクタンスでも通常のインダクタとみなして回路解析を行ってよいことを示した。部分インダクタンスは電磁気学の基本的な公式から計算でき、具体的な計算例は多いが[55]~[57]、いずれも直方体、長方形シート等特定の形状の導体セグメントに限られていた。これは導体セグメント内の電流の流線に相当するフィラメント状のセルのペアの体積に対して合わせて6重の積分が必要だったことによる。

本研究の成果のひとつはこの手法を改良し、太さ0のフィラメントを使った計算方式を

確立したことである。これにより任意の断面形状の導体セグメントについて部分インダクタンスを容易に計算できるようになった。

これらの改良,拡張の結果,従来[58]~[63]に比べて遥かに複雑な形状の導体系の過渡 解析が可能になった。

## (2) パスディレイチェックシステム

計算機の詳細設計は複雑な判断を要するものの、比較的均一なルールに基づく作業なので自動化に適する部分が多く、特に自動配線[64][65]、自動配置[66]、検査データ作成[67]の分野については早くから研究がなされ、プリント板を中心に実用化が進められていた。これらの技術はゲートアレー方式の出現とともにLSI設計にも改良、適用された[68]~[70]。一方詳細論理設計については自動化は困難で、設計結果を論理シミュレータで検証するのが通常行われている設計法である[71][72]。ところが大型計算機の設計においてはこれに加え、論理規模の増大と回路の高速化による実装ディレイの比率の増加によって、設計者が論理のパスのディレイを把握することが困難になり、これを自動的にチェックする新しい設計支援システムが必要となった。

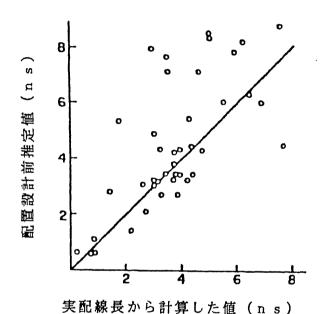

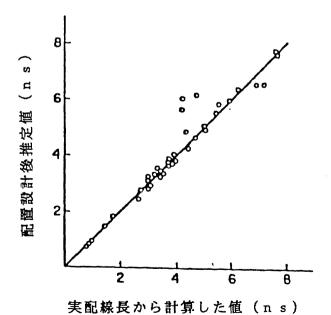

本研究の着手時にはパスのディレイに関連した設計支援システムとしてはPERT手法をディレイ計算に導入したもの[73]と,順序回路のレース解析[74]に関する研究が既に報告されていた。[73]は完了した設計データの特定のパスを選んで統計的な計算を行なうことが目的で,[74]はクロック信号等の入力データをもとに,順序回路の複雑なレース条件を検出するシステムであって,クリティカルパスを探索する点は共通しているが,本研究とは目的が違うので機能の上でも異なっている。本研究のディレイチェックシステムの特徴は,異なる階層をまたぐ部品を経由した非常に多数の論理のクリティカルパスを設計ファイルから自動的に発見できること,しかも実装設計が完了しない時点でもディレイを予測する機能を備えていることであり,これらは従来の文献よりも,むしろ実際の開発に携わる設計者のニーズから発したものである。同種のシステムはほぼ同時にいくつかの計算機メーカーから発表されており[75]~[80],以後この分野の研究が相次いで報告されている[81]~[85]。

## 2. 電気特性解析システム

## 2.1 電気特性解析の目的

#### 2.1.1 はじめに

電気特性解析システムは 1.2.2 で述べた設計のフェーズのうちの,基本ハードウェア設計の時点での設計支援を目的としている。このフェーズではその時点での最先端の要素技術レベルを最大限に活用して,高速の回路を高密度に実装できるようなハードウェア系の枠組みを作ることを目標としており,この結果が計算機のハードウェアとしての性能を大きく左右する。

この時点での設計において電気特性上最も問題としなければならないのはLSI内や 実装系でのノイズである。この時点で電気的に無理な設計をすると製品が誤動作を起こ すことになるが、もちろんこのような事態は絶対に避けなければならない。製品化前で も設計が進んでからこれが判明すれば、詳細論理設計の自由度や回路速度を犠牲にして 設計変更を行うことが必要で、ハードウェア性能の低下をもたらす。また不必要に安全 側に設計すると実装密度の低下をまねき、やはりハードウェア性能を低下させることに なる[86]~[89]。

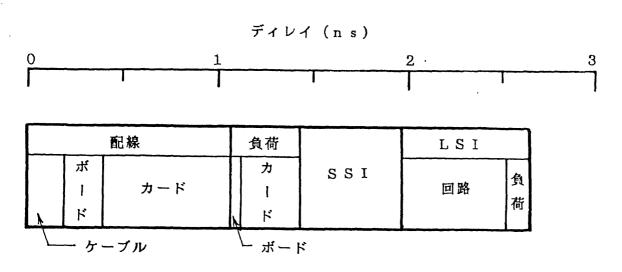

さらに基本ハードウェア設計の時点では実装系でのディレイ値を正確に見積ることが必要である。この結果は以後の設計各段階における性能評価の基本となるもので,第3章で述べるパスディレイチェックにおいてもこれを利用することになる。このディレイ値の評価についてもノイズの場合と同様,少なく見積りすぎて後で大きいことがわかった場合にはマシンサイクル時間が目標より長くなってしまって性能の低下をもたらす。また大きく見積りすぎれば,そのぶんディレイを目標値にあわせて短縮するために余分な努力を払うことになり,設計がアンバランスになってコストの上昇や開発の遅延をまねく。

ノイズ,およびディレイ値を正確に知る一番確実な手段は、プロトタイプを試作して 測定してみることであるが、構造の複雑さから設計の自由度が高く、考えられる方式を 全てカバーすることは難しい。従って限られた期間内にこれを正確に予測して、過不足 のない基本ハードウェア設計を完了するのは容易なことではない。従来は期限が迫れば 予測不可能な項目を残したまま、外れた場合の再設計のシナリオも用意した上で設計責 任者の勘で決断を下すことも少なくなかった。しかしハードウェアの高性能化を追及し、 信号の高速化と実装系の高密度化が進むにつれて電気特性を的確にコントロールするこ との重要性が高まっており、これを正確に予測できる設計支援システムの必要性が極め て高くなっている。

## 2.1.2 高速化・高密度化の問題点

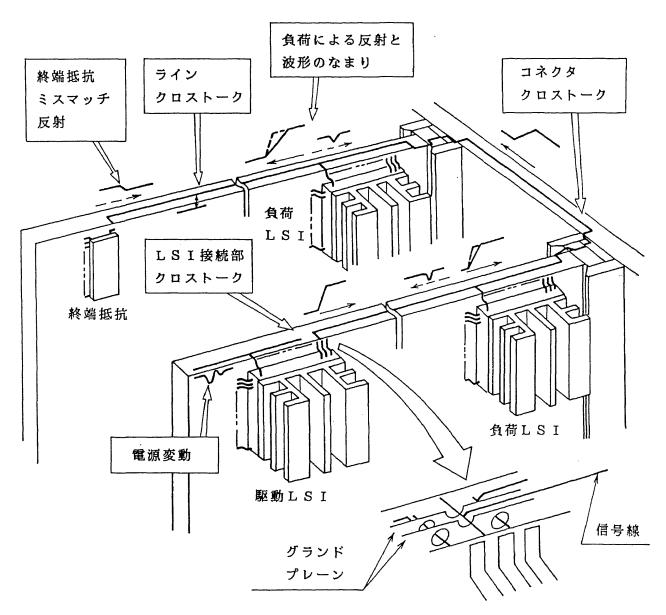

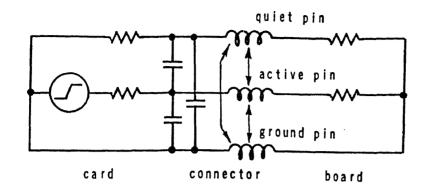

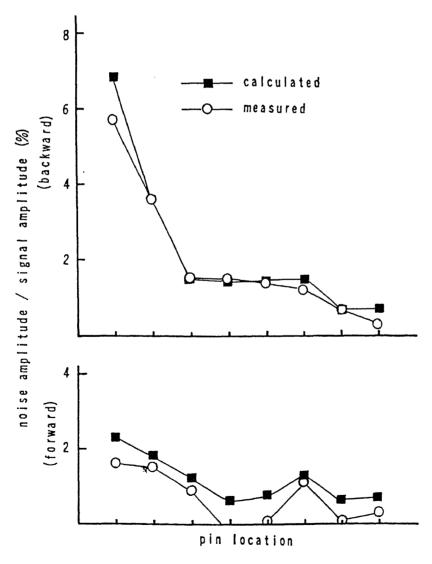

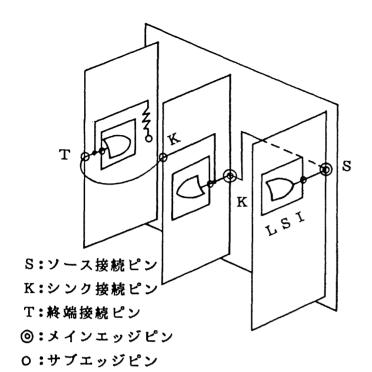

高速計算機では実装系内の信号伝送は基本的には整合終端したストリップラインなどの伝送線を使う。理想的な伝送線では入射波はそのままの波形を保って一定の速度で終端抵抗まで伝わる。図2・1・1 は実装系での信号伝送の形態と,ノイズ要因を示す概念図であり,図1・2・1 に示した実装系の場合を例にとって示したものである。駆動LSIを出たパルス信号はパッケージのピンを通ってカードの配線基板内層に設けた,グランドプレーンにはさまれたストリップラインに伝えられ,途中負荷となるLSIに信号を供給しながらコネクタ,ボードを通って別のカード内で配線の最遠端に設けられた終端抵抗に到達する。LSI出力ピンの部分,コネクタ,終端抵抗ピンで信号は伝送線でない所を通過する。また負荷LSIの所では伝送線からの枝別れがある。

図2.1.1 実装系での信号伝送とノイズ

このような配線系では次のようなノイズ要因が考えられ、特に高速化、高密度化に伴ってその影響が顕著になりつつある。

まずストリップライン自体の内部では(1)特性インピーダンス不整合による反射 (終端抵抗との不整合を含む)[90], (2) 隣接配線とのクロストーク[91], (3) 配 線の直流抵抗による電圧降下,がある。特に(1)によるノイズは電圧振幅も大きく継 続時間も長いのでカード,ボードの配線構造を設計する時に特性インピーダンスを正し く設定することが重要である。

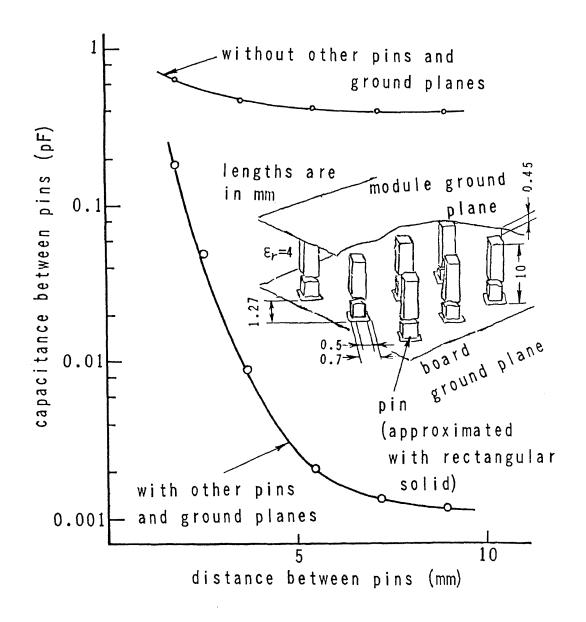

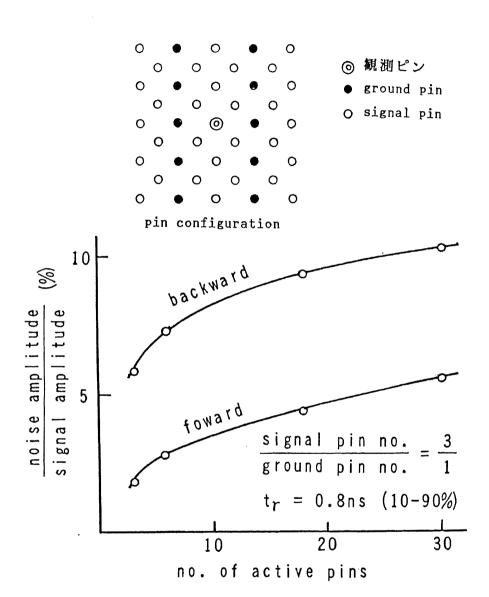

伝送線接続部で問題となるのは(4) LSIピン,およびコネクタでのクロストーク, (5) 負荷LSI接続部での反射と波形のなまり,である。またLSI接続部近傍では (6) 電源電圧の変動が生ずる[92][93]。マシンサイクル時間を短縮するためには,そ れに比例して信号の立上り時間も短縮が必要で,これは(4),(5),(6)を増加 させる要因となる。さらに(4) は高密度化によって多数のピンを一ヶ所に集中させる ことによって増大する。高密度化は大量の電流を小さな領域に供給する必要性を増し,

実装ディレイについては負荷LSI接続部やコネクタでの波形のなまり、配線構造が 理想的な伝送線から外れることによるディレイの増加が考えられる。

LSIパッケージ,カード,ボード,コネクタ等の設計ではこれらを全て考慮にいれる必要がある。

#### 2.1.3 電気特性解析システムへの要求事項

(6)が問題となる。

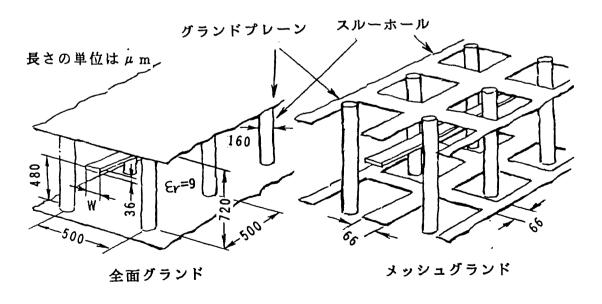

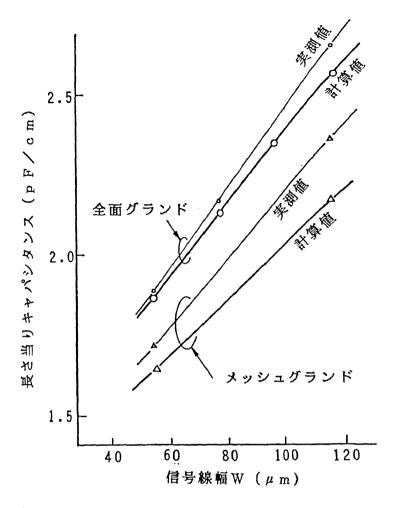

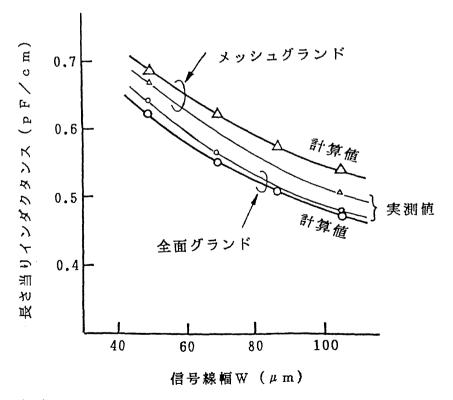

伝送線やその接続部分にパルス信号を印加した際の電磁気的応答を求めるためには、 最も一般的には Maxwell 方程式を解く必要があるが、上で述べたような計算機実装系 の多くの導体が複雑に組み合あわさった構造について電磁界の過渡応答を求めるのは現 実的でない。一般に導体の寸法がパルスの立上り時間内に電磁波が進む距離にくらべ十 分小さい場合には,電磁気現象を電気回路の問題として解けることが知られている[53]。 これをさらに一般化し,上述の小寸法の条件下では電磁気現象は導体の枝の部分インダ クタンスを通常のインダクタンスとみなした電気回路の応答と考えてよいことが電磁気 学的に証明できる(2.2節参照)。したがって計算機実装系のノイズ,ディレイの予測 は結局導体の3次元形状からキャパシタンスと部分インダクタンスを計算することに帰 着し,これより一般に実用化されている回路解析プログラムを使って過渡応答を求めれ 上述のストリップラインやその接続部分の例でもわかるように計算すべき対 象の形状は多様であり,これらの設計に広く適用可能であるためには一般の3次元形状 の電気特性解析ができなければならない。従来は伝送線の特性については2次元計算が 主体で、このほか集中的なキャパシタンス、インダクタンスの効果については単純な形 状で近似して電磁気学の公式を使って手計算し,回路解析プログラムを使って過渡応答 をシミュレートしていた。このように公式で計算できるような形状の例を表2.1.1に 示す[94]。しかし2.6節に述べるように断面形状が不均一な伝送線では2次元計算で

は正確な特性値は得られない。また単純化が不可能な不規則形状や,導体間の容量が別の導体によって遮蔽されている場合に適用できるような公式はない。表 2.1.2 に従来の方法では解析不可能で,3次元解析が必要である項目の例を示す。

また電磁気学や数値解析の専門家でない設計者が限られた期間内に設計を完了しなければならないことを考えれば、形状の特定の性質を利用してキャパシタンス、部分インダクタンスの計算を定式化するのではなく、任意の3次元形状を入力すればすぐに解が得られることが望まれる。2.3節以降に述べるようにキャパシタンス計算は表面電荷法で任意の形状に適用できるが、計算機処理時間を実用的な範囲に収めるには高速化のための改良が必要であった。また部分インダクタンスについては従来長方形等断面が一定の形状を持ち、電流の方向が一定とみなせるような導体に適用可能な計算アルゴリズムがあったが、このままでは適用先が限られるので本システムではこれを改良、拡張して、任意の断面形状の細長い導体を多数組み合わせたような構造に適用できるようにした。

表2.1.1 公式によりLCを求められる形状の例

|     | 形状                                                       | 公式                                                                         | 条件                 |

|-----|----------------------------------------------------------|----------------------------------------------------------------------------|--------------------|

| 円柱  | $r \stackrel{\varrho}{\longleftrightarrow}$              | $L = \frac{\mu \ell}{2 \pi} \left( \ln \frac{2 \ell}{r} - 1 \right)$       | 2 ≫ r              |

| 平行  | $r \stackrel{\ell}{ } $                                  | $C = \frac{\pi  \epsilon  \ell}{\ln(d/r)}$                                 | 1 ≫ d ≫ r          |

| 円柱  | $r \stackrel{d}{ \uparrow}$                              | $C = \frac{\pi \epsilon \ell}{\cosh^{-1}(d/2r)}$                           | l ≫ d              |

|     | ·_ Q                                                     | $M = \frac{\mu \ell}{2 \pi} \ln \frac{2 \ell}{d}$                          | l ≫ d              |

| 平行線 | d d                                                      | $M = \frac{\mu \ell}{2 \pi} [\ln(\sqrt{(\ell^2/d^2+1)} +$                  | $\frac{\ell}{d}$ } |

|     |                                                          | $+\frac{\mathrm{d}}{\varrho}\left(1-\sqrt{(\ell^2/\mathrm{d}^2+1)}\right)$ | }]                 |

| 同軸  | $ \begin{array}{c}                                     $ | $C = \frac{2\pi \epsilon \ell}{\ln(b/a)}$                                  | æ≫ъ                |

C:キャパシタンス, L:自己インダクタンス M:相互インダクタンス

表2.1.2 3次元電気特性解析の必要な項目とその理由

|     | 項目      | 計算内容 | 必要理由                   |

|-----|---------|------|------------------------|

| 伝送線 | 特性インピー  | С    | スルーホール,交差配線,グランドプレーンの  |

| 特性  | ダンス,    | L    | クリアランスホールがあり、断面形状が一定で  |

|     | 伝播遅延時間  |      | ないので2次元計算不可。           |

|     | LSIピン間  | C m  | 関与する導体数が数十個以上あり、導体間の   |

| LSI | クロストーク  | М    | Cm, Mが他の導体に影響されるので,利用可 |

| 接続部 |         |      | 能な近似公式なし。              |

| での  | 負荷LSIに  |      | 形状が複雑、また近くにあるピンを経由した対  |

| ノイズ | よる反射と波形 | С    | 地容量計算が必要のため利用可能な近似公式な  |

|     | のなまり    |      | υ.                     |

| 電源系 | 電源系のインピ | L    | 配線基板電源層,スルーホール,LSIパッケ  |

| ノイズ | ーダンスによる | М    | ージピンの自己・相互インダクタンスの計算が  |

|     | 電源変動    |      | 必要。形状の複雑さのため利用可能な近似公式  |

|     |         |      | なし。                    |

C: 対地容量,  $C_m$ : 導体間容量, L: 自己インダクタンス, M: 相互インダクタンス

## 2.2 問題の定式化

2.1節で述べたようにカード,ボード上のラインは伝送線とみなせるように作ってある(そうしないと波形歪,クロストークが大きくなってしまう)。この過渡応答は伝送線のパラメータ(特性インピーダンス,伝播遅れ,クロストーク係数)から求められ,これらのパラメータはいずれも伝送線長さ当りのキャパシタンス,インダクタンスから計算できる。

また現在計算機で使用しているパルス信号の立上り時間は1 n s 前後であり、材質の比誘電率を4.0とするとこの立上り時間の間に電磁波が伝わる距離は約15 c m になる。これに比べれば電流切替ノイズ、クロストークノイズ、反射ノイズ等の原因となるようなLSI接続部やカード、コネクタ等の寸法は十分小さいと言える(逆にもしこのような接続部の寸法が上に述べた距離と同等、あるいは大であったとすると、発生するノイズ振幅が信号振幅と同程度以上になってしまって実用に耐えない)。したがって以下に述べるように、このような伝送線接続部での電磁気的現象は電気回路の問題として取り扱うことができる。

すなわち計算機実装系での電磁気的現象を解析するには、形状からキャパシタンスとインダクタンスを求めれば、後は手計算か、既存の回路解析システムを利用することによって結果を得ることができる。

特にインダクタンスについては通常のインダクタンスの概念を拡張した部分インダク タンス (Partial Inductance) を導入して解析する方法が知られている[51][52]。

部分インダクタンスとは通常のインダクタのようにそれ自身で完全なループを形成し ていない導体、例えば円柱や直方体など(ループの一部分になっているもの)に対して 定義される電気的特性で,通常のインダクタンスと同様に取り扱って解析する。例えば コネクタの多数のピンに同時にパルス信号が通過した場合の過渡電流のループは単純で なく、信号ピンとグランドピン多数にわたるループの組合せになっており、形状だけか らループを抽出するのは困難な上、ループの途中にキャパシタンスがあるようなケース もあるので、この部分インダクタンスを用いなければ等価回路を構成できない。

この解析法の根拠は従来必ずしも明確でなかった。すなわちループの一部である遵体 の部分部分について部分インダクタンスを求め, それらを通常のインダクタとみなして 電気回路論的に過渡応答を求めることの正当性が電磁気学的に説明されていなかった。

これは導体ループの途中の点のスカラーポテンシャルをその点の電気回路としての電 圧と解釈することによって以下に述べるように説明可能である。

## (1) 通常の電圧の定義による説明

電気回路論の基本法則は J.R.Carson[53]等によって電磁気学から導けることが示さ れている。以下簡単にこれを紹介する。

まず電界EはスカラーポテンシャルΦ,ベクトルポテンシャルΑを使って次のように 表わせる

$$\mathbf{E} = -\operatorname{grad}\Phi - \frac{\partial \mathbf{A}}{\partial \mathbf{t}} . \qquad (2.2.1)$$

2点a, b間の電圧は通常の定義によれば

$$V_{ba} = -\int_{a}^{b} \mathbf{E} \cdot d\mathbf{l} = \int_{a}^{b} \operatorname{grad}\Phi \cdot d\mathbf{l} + \int_{a}^{b} \frac{\partial \mathbf{A}}{\partial t} \cdot d\mathbf{l}. \quad (2.2.2)$$

この式で積分経路をループにとると、右辺第1項は0になり、

$$V_{aa} = -\oint \mathbf{E} \cdot d\mathbf{l} = \oint \frac{\partial \mathbf{A}}{\partial \mathbf{t}} \cdot d\mathbf{l} \qquad (2.2.3)$$

となる。Kirchhoffの電圧則を導くにはループに沿う電圧の和は0でなければならない がこの式の右辺は必ずしも0とはならず、以下に示すようにループ内を貫通する磁束の 時間変化に等しくなる。

$$\oint \frac{\partial \mathbf{A}}{\partial \mathbf{t}} \cdot d\mathbf{l} = \frac{\partial}{\partial \mathbf{t}} \int \operatorname{rot} \mathbf{A} \cdot \mathbf{n} d\mathbf{s} = \frac{\partial}{\partial \mathbf{t}} \int \mathbf{B} \cdot \mathbf{n} d\mathbf{s}$$

$$= \frac{\partial \Psi}{\partial \mathbf{t}} , \qquad (2.2.4)$$

ここで  $\mathbf{s}$  はループを覆う面,  $\mathbf{B}$  は磁束密度,  $\mathbf{n}$  は面  $\mathbf{s}$  の法線ベクトル,  $\Psi$  は磁束を表す。

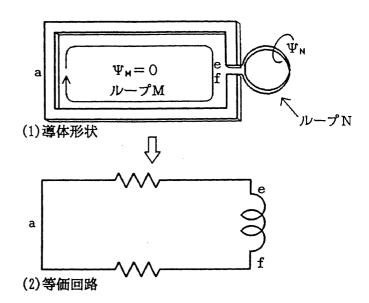

従ってインダクタを含むループについてKirchhoffの電圧則が成立するのは図2.2.1のループMのようにその内部を貫く磁東 $\Psi_{N}$ が0の場合のみである。この場合インダクタは図に示すようにループMから分離されたループNとみなせる構造をしており、その両端e、f間の電圧は $\partial$   $\Psi_{N}$ / $\partial$  t で与えられるが、内部の各点の電圧は定義できない。

$$V_{ba} = -\int_{a}^{b} E \cdot dl$$

$$= -\int_{a}^{b} \frac{J}{\sigma} \cdot dl$$

$$(2.2.5)$$

ここでJは電流密度, $\sigma$ は導電率を表す,

図2.2.1 インダクタ内部のみ鎖交磁束のある 導体系の等価回路

図2.2.2 鎖交磁束のある導体ループの 等価回路

となり,通常のインダクタのような, 電流の時間変化に比例する電圧が生じなくなってしまう。

## (2) 電圧の定義をスカラーポテンシャルの差とした説明

2点a, b間のスカラーポテンシャルの差 $\Phi_{ba}$ ( =  $\Phi_b$  -  $\Phi_a$ )は式(2.2.2)より

$$\Phi_{ba} = \int_{a}^{b} \operatorname{grad} \Phi \cdot dl = -\int_{a}^{b} \mathbf{E} \cdot dl - \int_{a}^{b} \frac{\partial \mathbf{A}}{\partial t} \cdot dl. (2.2.6)$$

導体内では

$$\mathbf{E} = \frac{\mathbf{J}}{\sigma} \quad \text{なので式} \ (2.2.6) \ \mathbf{L},$$

$$\Phi_{\mathbf{b}a} = -\int_{a}^{b} \frac{\mathbf{J}}{\sigma} \cdot d\mathbf{l} - \int_{a}^{b} \frac{\partial \mathbf{A}}{\partial t} \cdot d\mathbf{l}. \tag{2.2.7}$$

パルスの立上り時間の間に電磁波が伝播する距離に比べ小さい範囲におさまる系では ベクトルポテンシャルAは次の式で表すことができる。

$$\mathbf{A}(\mathbf{r}, \mathbf{t}) = \frac{\mu}{4\pi} \int \frac{\mathbf{J}(\mathbf{r}', \mathbf{t}) d\mathbf{r}'}{|\mathbf{r} - \mathbf{r}'|}, \qquad (2.2.8)$$

ただしμは透磁率, rは位置ベクトルで, 積分は全空間に対して行なう。

これを式(2.2.7)に代入すると

$$\Phi_{ba} = -\int_{a}^{b} \frac{J}{\sigma} \cdot dl - \frac{\mu}{4\pi} \int_{a}^{b} dl \cdot \int \frac{\partial}{\partial t} \frac{J(r', t) dr'}{|r - r'|} \cdot (2.2.9)$$

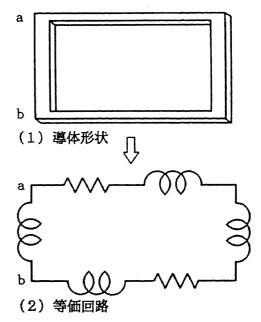

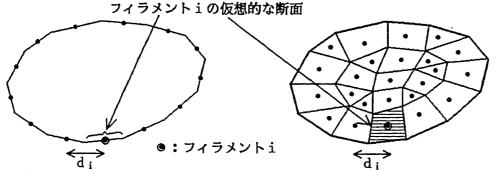

次に導体を図2.2.3に示すように電流の方向に断面積 $S_i$ , 長さ $\ell_i$ のフィラメント状のセルに分割し、式(2.2.9)の d $\ell$  に関する積分をセル i 内の積分の和として、 d $\ell$  に関する積分をセル j 内の積分の和で表す。ただし第2項についてはセルi内で太さ方向に平均した値を使う。 $\ell$  のパスをPで表すと、

$$\Phi_{ba} = -\sum_{i \in P} \int_{t \in P} \frac{J_i}{\sigma_i} \cdot dl_i$$

$$-\frac{\mu}{4\pi} \sum_{i \in P} \sum_{j \in 2} \frac{1}{S_i t \in N_i} \int_{t \in N_j} \frac{\partial}{\partial t} \frac{ds_i dl_i \cdot J_j dr_j}{|r_i - r_j|}. \quad (2.2.10)$$

セルi内でJ,  $\sigma$  がそれぞれ一定値J<sub>i</sub>,  $\sigma$ <sub>o</sub>iであるとすると(jも同様),

$$\Phi_{ba} = -\sum_{i \in P} \frac{J_i \ell_i}{\sigma_{ai}} - \frac{\mu}{4 \pi} \sum_{i \in P} \sum_{j \in 2 \# k} \frac{\partial J_j}{\partial t} \frac{1}{S_i t \hbar i} \int_{t \hbar j} \frac{d l_i \cdot d l_j d s_i d s_j}{|\mathbf{r}_i - \mathbf{r}_j|}, (2.2.11)$$

$$I_i = J_i S_i,$$

(2.2.12a)

$$R_{i} = \frac{\ell_{i}}{q_{2} \cdot S_{i}}, \qquad (2.2.12b)$$

$$L_{ij} = \frac{\mu}{4 \pi S_{i} S_{j}} \int_{t \neq i} \int_{t \neq j} \frac{d l_{i} \cdot d l_{j} ds_{i} ds_{j}}{|\mathbf{r}_{i} - \mathbf{r}_{j}|}$$

$$\Phi_{ba} = -\sum_{i \in P} I_{i} R_{i} - \sum_{i \in P} \sum_{j \in 2} L_{ij} \frac{\partial I_{j}}{\partial t}$$

$$(2.2.12c)$$

となり,抵抗Riと部分インダクタンスLijを含む経路の電流と電圧の関係になっていることがわかる。

式 (2.2.13) で経路 P がループになっていれば, すなわち点 a と b が同一の点ならば

$$\Phi_{ba} = \Phi_{aa} = \Phi_{a} - \Phi_{a} = 0$$

であるからKirchhoffの電圧則,

$$0 = -\sum_{i \in P} I_i R_i - \sum_{i \in P} \sum_{j \in 2 \not\equiv k} L_{ij} \frac{\partial I_j}{\partial t}$$

(2.2.14)

が成り立つ。

また式(2.2.13)の I i は電流の方向に断面積一定の柱状の細長いセル内の電流を表しており、導体は一般にはこれらを複数束にしたものになる。その各々を通るループについて式(2.2.14)をたて、後に述べるKirchhoffの電流則と連立させて解けば全体の過渡応答を求めることができる。

このように電圧としてスカラーポテンシャルをとれば、部分インダクタンスがある場合の過渡応答を電気回路の問題に帰着して解くことができるが、得られた「電圧」はあくまで通常の(1)の定義とは異なったものである。しかし通常ノイズとして実測にかかるのは近接した2点間の電圧であり、このような場合両者は一致する。

図2.2.3 フィラメント状のセルの例

## (3) 導体でつながっていないパス両端の電圧

$a \rightarrow b$  のパスが直接導体でつながっていない場合には式(2.2.7) 右辺第1項のJ,  $\sigma$  が共に0 となってしまい,式(2.2.1.3) のように表すことはできない。この場合には a, b 間の変位電流とスカラーポテンシャルの差の関係から以下のように定式化できる。 立上り時間の間に電磁波が伝播する距離に比べ小さい範囲におさまる系ではスカラーポテンシャルΦは次式で表すことができる。

$$\Phi(\mathbf{r}, \mathbf{t}) = \frac{1}{4\pi\epsilon} \int \frac{q(\mathbf{r}', \mathbf{t}) ds'}{|\mathbf{r} - \mathbf{r}'|}, \qquad (2.2.15)$$

ここで ε は誘電率, q(r', t)は, 位置 r', 時刻 t での電荷密度である。

これより導体の表面を n 個のセル(i,j=1,2,...,n)に分割し、それらをポテンシャルが一定とみなせる N 個のグループ(I,J=1,2,...,N)に分けると,i  $\in$  I として、

$$\Phi_{I} = \frac{1}{4 \pi \epsilon} \sum_{j=1}^{N} \sum_{j \in J} \int_{i \neq j} \frac{q(\mathbf{r}_{j}) ds_{j}}{|\mathbf{r}_{i} - \mathbf{r}_{i}|}, \qquad (2.2.16)$$

ここで変数 t は省略した

次にセルう内では電荷密度が一定であるとし、

$$G_{ij} = \frac{1}{4 \pi \epsilon S_i S_i} \int_{\mathbf{r}} \int_{\mathbf{r}_i - \mathbf{r}_i} \frac{d s_i d s_j}{|\mathbf{r}_i - \mathbf{r}_i|}, \qquad (2.2.17)$$

q:: セルj内の電荷,

Si, Si: セルi, jの面積,

とすると,式(2.2.16)より,

$$\Phi_{I} = \sum_{i=1}^{N} \sum_{i \in I} G_{ij} q_{i} \qquad (i \in I). \qquad (2.2.18)$$

式 (2.2.18) を  $q_1$ について解き、ポテンシャルが一定であるグループ I 内のセルの電荷の合計を  $Q_1$ とすると、

$$Q_{I} = \sum_{I=1}^{N} T_{IJ} \Phi_{J}, \qquad (2.2.19)$$

ここで

$$T_{ij} = \sum_{i \in I} \sum_{j \in J} G^{-i}_{ij}$$

(I,J = 1,2,...,N). (2.2.20)

ポテンシャルが一定であるセルのグループ a が $\Phi_{ab}$ ボルト, b および他のグループが全て 0ボルトのときの,グループ a から b に向かう電東  $\phi_{ab}$ は,グループ b の電荷  $Q_b$  の符号 を変えたものになるので式(2.2.19)より

$$\phi_{ab} = -Q_b = -T_{ab}\Phi_{ab} = T_{ab}\Phi_{ba} . \qquad (2.2.21)$$

これよりaからbへの変位電流は

$$\frac{\partial \, \psi_{ab}}{\partial \, t} = T_{ab} \, \frac{\partial \, \Phi_{ba}}{\partial \, t} \quad . \tag{2.2.22}$$

ここで

$$\frac{\partial \phi_{ab}}{\partial t} \rightarrow I_{ab} (a からbへの電流)$$

(2.2.23)

Φьα → Vьα(ba間の[bのaに対する]電圧)

-Tab → Cab (ab間のキャパシタンス)

と置き換えれば式 (2.2.22) は

$$I_{ab} = -C_{ab} \frac{\partial V_{ba}}{\partial t} . \qquad (2.2.24)$$

これはキャパシタCabを流れる電流と、両端の電圧との関係になっている。

なお,式(2.2.24)は a と b が直接導体で接続されている場合にも,式(2.2.13) と並列な枝として成立する。この時は電気回路としての電流は下記のように対応づければ よい。

$$\int J_{ab} \cdot \mathbf{n} \, ds + \frac{\partial \psi_{ab}}{\partial t} \rightarrow I_{ab} \qquad (2.2.25)$$

ただしこのようにaとbが直接導体で接続されている場合は,通常a,b間の変位電流は真の電流に比べて無視できることが多い。

また電流を式 (2.2.25) のように定義しておけば、Maxwell方程式より,

$$rot H = \frac{\partial D}{\partial t} + J.$$

これより

$$\operatorname{div}\left(\frac{\partial \mathbf{D}}{\partial t} + \mathbf{J}\right) = 0. \tag{2.2.26}$$

これを上に述べたポテンシャルが一定とみなせる領域D。について積分してもOになるから,

$$\int_{\Sigma_a} \left( \frac{\partial \mathbf{D}}{\partial t} + \mathbf{J} \right) \cdot \mathbf{n} \, ds = \int_{D_a} \operatorname{div} \left( \frac{\partial \mathbf{D}}{\partial t} + \mathbf{J} \right) \, d\mathbf{r} = 0. \quad (2.2.2.7)$$

これはこの領域の境界 $\Sigma$ 。から流出する電流と変位電流の和が0であること、すなわち式(2.2.2.5)で定義した電流に関し、Kirchhoffの電流則が成り立つことを示している。

以上述べたように寸法が波長に比べ無視できるような系の電磁気的な過渡応答は、電気

回路の問題として解くことができる。すなわち、

- (a) 形状からキャパシタンスとインダクタンスを求め,

- (b) 回路解析を行う,

ことによって過渡応答を計算できる。

そして特に部分インダクタンスを考える必要のある導体系の場合は各部のスカラーポテンシャルの差を電圧とし、電流と変位電流の和を電流とするような回路の動作として求めることができる。表 2.2.1 に要約を示す。

表2.2.1 部分インダクタンスのある系の電気回路との対応

| A THE HEAT IN THE STATE OF THE |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 電磁気学的諸量                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 電気回路的諸量       |

| スカラーポテンシャルの差                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| $\Phi_{ba} \ (=\Phi_{b}-\Phi_{a})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V ba (電圧)     |

| $\frac{\partial \psi}{\partial t} + \int \mathbf{J} \cdot \mathbf{n}  ds$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I (電流)        |

| ν<br>σS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R (抵抗)        |

| 部分インダクタンス                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| $\frac{\mu}{4\pi} \int \int \frac{d \mathbf{l}_i \cdot d \mathbf{l}_j  ds_i ds_j}{ \mathbf{r}_i - \mathbf{r}_j }$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Lii (インダクタンス) |

| -Σ Σ G <sup>-1</sup> ;<br>iea jeb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Саь(キャパシタンス)  |

| $\Phi_{\alpha\alpha} = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Kirchhoffの電圧則 |

| $rot H = \frac{\partial D}{\partial t} + J .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Kirchhoffの電流則 |

## 2.3 キャパシタンス計算手法

## 2.3.1 基本方式

一般的な形状のキャパシタンスの計算手法としては、有限要素法、差分法、表面電荷法が考えられ、一長一短がある。有限要素法、差分法は空間をセルに分割するので3次元形状ではセルの数が非常に多くなり、従って連立1次方程式の係数行列の次数が非常に大きくなるがスパース行列なので解きやすい。表面電荷法は導体の表面をセルに分割するので比較的少ないセル数、従って行列の次数ですむが密行列である。一般的な形状について計算時間、精度の点でどれが優れているかは簡単には判定出来ないが、計算機実装系の電気特性解析では3次元不規則形状の多数の導体を対象とするため、導体と導体の間の空間を3次元セルに分割することはほとんど不可能に近いと考えられる。そこで基本方式として表面電荷法を採用した。

表面電荷法は以下に述べるように係数行列の計算(セル数をnとして処理時間がn²に比例)と連立1次方程式を解く部分(n³に比例)に分けられるが,係数行列の計算を高精度化してnを比較的少なくても良いような工夫をしたSilvester等の方法[48][50](これにより係数行列の計算時間は大だが連立1次方程式を解く時間は短縮できる)を採用した。

採用した方法を簡単に紹介する。この方法は文献[48]等に述べられているのでここでは まとめて簡潔に述べておく。まず誘電率一定の空間内にN個の導体がある系について説明 する。

点rでの電位は下式で表わされる。

$$\Phi(\mathbf{r}, t) = \frac{1}{4\pi\epsilon} \int \frac{q(\mathbf{r}', t) ds'}{|\mathbf{r} - \mathbf{r}'|}, \qquad (2.3.1)$$

ここで q(r', t): 点 r', 時刻 t での電荷密度,

ε:誘電率

である。電荷は導体の表面のみに存在するので右辺の積分は導体の表面について行なう。 次にN個の導体の表面を合計n 個のセル(i,j=1,2,...,n)に分割する。なお変数 t は省略する。

$$\Phi(\mathbf{r}_{i}) = \frac{1}{4 \pi \epsilon} \sum_{j=1}^{n} \int \frac{q(\mathbf{r}_{j}) d\mathbf{s}_{j}}{|\mathbf{r}_{i} - \mathbf{r}_{i}|}, \qquad (2.3.2)$$

$q_i$ をセルj内の電荷, $S_i$ をセルjの面積とし,セルj内で電荷密度一定 $(=q_i/S_i)$ とすると,

$$\Phi(\mathbf{r}_{i}) = \frac{1}{4 \pi \epsilon} \sum_{j=1}^{n} \frac{q_{j}}{S_{i}} \int_{\mathbf{r}_{i} - \mathbf{r}_{i}} \frac{ds_{j}}{|\mathbf{r}_{i} - \mathbf{r}_{i}|}. \qquad (2.3.3)$$

$\Phi(\mathbf{r_i})$ に適当な値を仮定して $\mathbf{q_i}$ についてこの式を解けばキャパシタンスを求めることができるが、セルiとjのサイズがセル間の距離に比べ無視できない場合には右辺の積分で  $\mathbf{r_i}$ をどこに取るかによって結果が異なってくる。そこで  $\mathbf{r_i}$ はセルi内の代表的な点(重心など)に取ってセル分割を十分細かくする必要がある。ところがセル分割が細かくセル数が大だと係数行列が大きくなってしまうので、なるべく粗いセル分割ですむように式(2.3.3)をセルi内で平均し、

$$\Phi_{i} = \frac{1}{S_{i}} \int_{i} \Phi(\mathbf{r}_{i}) ds_{i}.$$

式 (2.3.3) よりこの $\Phi_i$ は,

$$\Phi_{i} = \frac{1}{S_{i}} \int_{i}^{\infty} \Phi(\mathbf{r}_{i}) ds_{i} = \sum_{j=1}^{n} G_{ij} q_{j}, \qquad (2.3.4)$$

$$G_{ij} = \frac{1}{4 \pi \epsilon S_i S_j} \int_{\nu} \int_{\nu} \frac{d s_i d s_j}{|\mathbf{r}_i - \mathbf{r}_j|}$$

(2.3.5)

となる。これより容量行列を求めるには式(2.3.5)で係数行列を求め、Φ;に適当な値を仮定して式(2.3.4)の連立1次方程式をq;について解けばよい。結果は以下のようになる。導体数をNとし、導体の番号を示す添え字をI,Jとすると、

$$\mathbf{g} = \mathbf{G}^{-1}$$

とおくと、 $\mathbf{j} \in \mathbf{J}$  ならば $\Phi_{\mathfrak{j}} = \Phi_{\mathfrak{j}}$ なので

$$q_i = \sum_{j=1}^n g_{ij} \Phi_j = \sum_{J=1}^N \Phi_J \sum_{j \in J} g_{ij}$$

.

導体 I 上のセル電荷の合計をQ<sub>1</sub>とすると

$$Q_{I} = \sum_{i \in I} q_{i} = \sum_{j=1}^{N} \Phi_{j} \sum_{i \in I} \sum_{j \in J} g_{ii}, \qquad (2.3.6)$$

ここで

$$T_{ij} = \sum_{i \in I} \sum_{j \in J} g_{ij}$$

とおけば式 (2.3.6) は, (2.3.7)

$$Q_{I} = \sum_{I=1}^{N} T_{IJ} \Phi_{J}, \qquad (2.3.8)$$

従って行列 {T<sub>II</sub>} は導体系の容量・誘導係数行列[95]になっている。

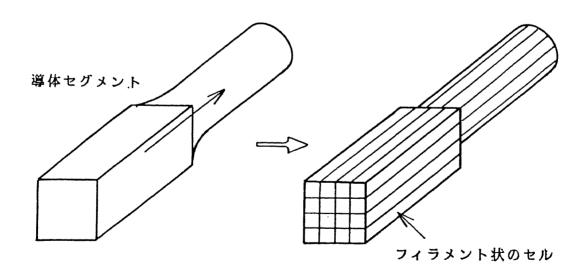

式(2.3.1)は誘電率が一様な場合にしか適用できない。いくつかの誘電率の異なる領域(領域内部では誘電率は一定であるものとする)がある場合には次のような解法が知られている[40]。

キャパシタンスを求めようとする真の系とすべての点で電界が同じであり、誘電率は全 領域で真空の誘電率に等しいような系(等価真空系)を考える。この系では式(2.3.1) が成立するので電位と電荷密度の関係が求まる。真の系の電荷密度は等価真空系での電荷 密度から簡単に求められるので、これより真の系の電位と電荷密度の関係がわかり、キャパ シタンスを計算することができる。

ここで真の系と等価真空系の関係について次のことが言える。q<sub>t</sub>を全電荷密度とし、等 価真空系での量に\*をつけて示すことにすると、

$$q_t^*(\mathbf{r}) = \epsilon_0 \operatorname{div} \mathbf{E}^*(\mathbf{r}) = \epsilon_0 \operatorname{div} \mathbf{E}(\mathbf{r}) = q_t(\mathbf{r})$$

(2.3.9)

より,真の系と等価真空系の全電荷分布は等しい。等価真空系では比誘電率が1なので $q^*(\mathbf{r}) = q_*^*(\mathbf{r})$  である。これより,

$$q^*(\mathbf{r}) = q_t(\mathbf{r}), \tag{2.3.10}$$

すなわち等価真空系の真電荷分布は真の系の全電荷分布に等しい(表 2.3.1)。

以下真の系として比誘電率がそれぞれ  $\epsilon_A$ ,  $\epsilon_B$ であるような領域 A, B がある場合(図 2.3.1)について電荷が満たすべき条件式を導出する。導体の表面と誘電体境界面をセルに分割し、

1,2,...,nを導体セル,

n+1,n+2,...,n+mを誘電体セルとする。

等価真空系でのセルう内の真電荷を q;とすると,導体セルiの電位 Φ;については式

(2.3.4)と同様に,

$$\Phi_{i} = \sum_{j=1}^{n+m} G_{ij} q_{j} \qquad (i=1,2,...,n) \qquad (2.3.11)$$

が成り立つ。誘電体セル(i=n+1,n+2,...,n+m)についても同じ式が成り立つが、導体セルの場合とちがって $\Phi_i$ を既知の量として与えることができないので使えない。

表2.3.1 真の系と等価真空系の諸量の関係

|     |     | 真の系                                                | 等価真空系                                    |

|-----|-----|----------------------------------------------------|------------------------------------------|

| 電界  |     | E(r)                                               | E*(r)[=E(r)]                             |

| 全電荷 | 密度  | q <sub>t</sub> (r)                                 | $q_t^*(r) [=q_t(r)]$                     |

| 真電荷 | 導体上 | $q(\mathbf{r}_c) [= \epsilon_r q_t(\mathbf{r}_c)]$ | $q^*(\mathbf{r}_c) [=q_t(\mathbf{r}_c)]$ |

| 密度  | 誘電体 | 0                                                  | $q^*(\mathbf{r}_D) [=q_t(\mathbf{r}_D)]$ |

|     | 境界上 |                                                    |                                          |

ε.: 比誘電率

添字C:導体表面上 添字D:誘電体境界

而上

\*: 等価真空系での

量

図2.3.1 誘電体境界上の真電荷および全電荷

そこで今等価真空系の誘電体セルi内の真電荷を $q_i$ とすれば, $E_{iA}$ , $E_{iB}$ をそれぞれセルi表面上のA側,B側での電界の領域A側向き法線方向成分とすると,

$$E_{iA} = \frac{q_i}{2 f_0 S_i} + E_{iD}, \qquad (2.3.12)$$

$$E_{iB} = \frac{-q_i}{2 \epsilon_n S_i} + E_{iD}, \qquad (2.3.13)$$

ここで

$$E_{io} = -\frac{\partial}{\partial n} \sum_{j \neq i} \frac{q_{j}}{4 \pi \epsilon_{o} S_{i} S_{j}} \int_{i} \frac{d s_{i} d s_{j}}{|r_{i} - r_{j}|} \qquad (2.3.14)$$

$$(i=n+1, n+2, \dots, n+m),$$

Si, Si: セルi, jの面積,

n:セルの法線ベクトル(領域A側向き).

一方 $E_{iA}$ ,  $E_{iB}$ は真の系でも同じ値なので、真の系の誘電体境界上で div D=0が成り立つことから、

$$\varepsilon_{A} E_{iA} = \varepsilon_{B} E_{iB}. \qquad (2.3.15)$$

式(2.3.12)~(2.3.15)より

$$q_{i} = 2 \epsilon_{0} \frac{\epsilon_{A} - \epsilon_{B}}{\epsilon_{A} + \epsilon_{B}} \sum_{j \neq i} \frac{q_{i}}{4 \pi \epsilon_{0} S_{i}} \int_{i}^{j} \frac{\partial}{\partial n} \frac{d s_{i} d s_{i}}{|\mathbf{r}_{i} - \mathbf{r}_{i}|}$$

$$(i=n+1, n+2, ..., n+m). \qquad (2.3.16)$$

式(2.3.11)と式(2.3.16)をまとめると,

ここで

$G_{i,j}$ は式(2.3.5)(i=1,2,...,n, j=1,2,...,n+m)で与えられ,

$$H_{ij} = -2 \epsilon_{0} \frac{\epsilon_{A} - \epsilon_{B}}{\epsilon_{A} + \epsilon_{B}} \frac{1}{4 \pi \epsilon_{0} S_{j}} \int_{i}^{\infty} \frac{\partial}{\partial \mathbf{n}} \frac{d s_{i} d s_{j}}{|\mathbf{r}_{i} - \mathbf{r}_{j}|}$$

$$(i=n+1,n+2,...,n+m, j=1,2,...,n+m, i \neq j),$$

$$H_{ii} = 1 \qquad (i=n+1,n+2,...,n+m). \qquad (2.3.18b)$$

容量行列を計算するには誘電率一様の場合と同様,導体の電位Φ<sub>i</sub>を適当な値の組合せ に順次仮定して連立方程式(2.3.17)によって各導体上の電荷を求めればよい。

#### 2.3.2 大規模問題への適用に向けての改良

計算機実装系の複雑な形状に適用するためには (a) 形状の記述の自由度が高いこと, (b) 実用可能な処理時間で精度の高い計算ができることが必要である。このため基本アルゴリズムに以下のような改良を加えた。

#### (1) セルの形状

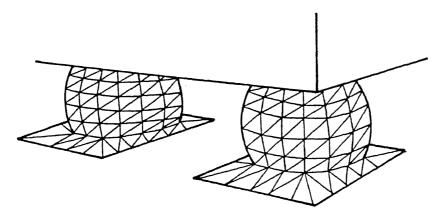

導体表面及び誘電体境界面は一般には不規則な形状をしており、長方形の組合せで記述できないことが多い。そこでセルの形状としては3角形を採用した。図2.3.2は不規則な形状をした対象の3角形セルへの分割の例である。

#### (2) 中心間距離近似

キャパシタンス計算処理は (a) 式(2.3.5)および式(2.3.18)による係数行列の計算(処理時間はセル数の2乗に比例)と、(b) 連立方程式(2.3.4)または(2.3.1

7)を解く部分(処理時間はセル数の3乗に比例)に分けられ、対象形状の複雑度によって それぞれの処理に要する時間の比率が異なる。(b)が問題になるのは数十ピンのコネク タ等特に複雑な形状で、それ以外では(a)が処理時間の大部分を占めている。

図2.3.2 三角形セルによる分割例

(a) の処理において式(2.3.5)または式(2.3.18a)はセルiとセルjが十分離れていれば被積分関数をほぼ定数とみなすことができ、それぞれ

$$G_{ij} = \frac{1}{4 \pi \epsilon | \mathbf{r}_{i0} - \mathbf{r}_{j0}|} \qquad (i=1,2,...,n,j=1,2,...,n+m), (2.3.19)$$

$$H_{ij} = -2 \epsilon_{0} \frac{\epsilon_{A} - \epsilon_{B}}{\epsilon_{A} + \epsilon_{B}} \cdot \frac{S_{i}}{4 \pi \epsilon_{0}} \cdot \frac{\partial}{\partial \mathbf{n}} \cdot \frac{1}{|\mathbf{r}_{i0} - \mathbf{r}_{j0}|} \qquad (2.3.20)$$

$$(i=n+1,n+2,...,n+m,j=1,2,...,n+m),$$

ただし rio, rio: セルi, jの重心座標 と近似することができる。以下この方法を中心間距離近似とよぶ。

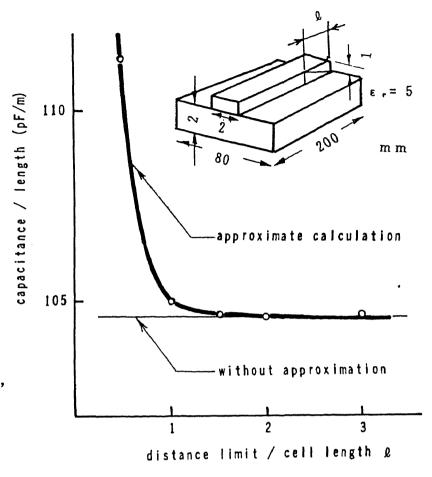

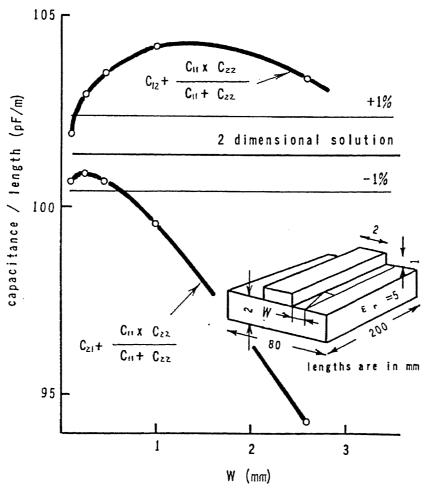

この近似法が適用可能かどうかはセルの重心間距離とセルサイズに依存する。図2.3.3は中心間距離近似によって計算した結果の例である。プログラムは各セルのペア(i,j)毎に重心間距離 | rio - rio | とセルi,jの最大辺長の比を求め,この比が一定の限界値以上になった場合のみ中心間距離近似を適用するようになっており,図2.3.3の横軸はこの限界値を示している。図よりこの限界値が約1.5以上ならば中心間距離近似を適用できることがわかる。これについては今までに適用した他の種々の形状についてもほぼ同じ結果が得られている。

## (3)係数行列要素の計算

式(2.3.5),(2.3.18a)はともに3角形セルiとjの面内の積分であり、4重積分になる。基本的には内側の2重積分について解析的に解いた式を用いて、数値積分により外側の2重積分を計算している。プログラム化に当って次の点に考慮した。

(a) セルi とjの位置関係によっては内側の2重積分が発散する場合がある。これを避けるために3角形を分割して円筒座標を使って特異性を除去する方法が知られている[96]。

一方処理時間の点では3角 形を直接直角座標で積分する ほうが有利なので,発散する ケースとしないケースによっ て使い分けることにした。

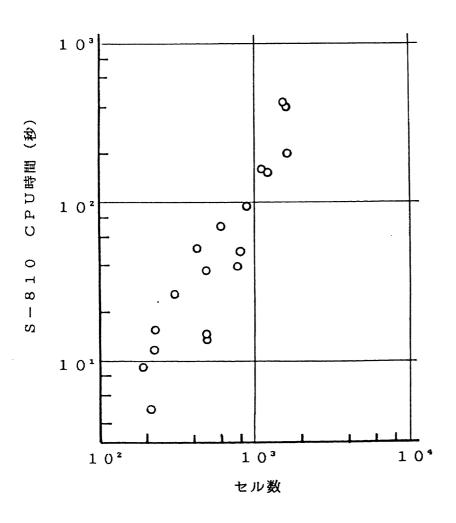

(b)プログラムは科学計算機の利用を前提に開発した。そこでベクトルプロセッサ,および仮想メモリ方式計算機の利用効率を高めるため,ループ構造の発がの除去に留意した[97]。

## 2.3.3 計算結果の例

図2.3.3 中心間距離近似の精度

計算のチェックのため、キャパシタンスが既知であるような形状に適用して比較した結果を図2.3.5,図2.3.6に示す。

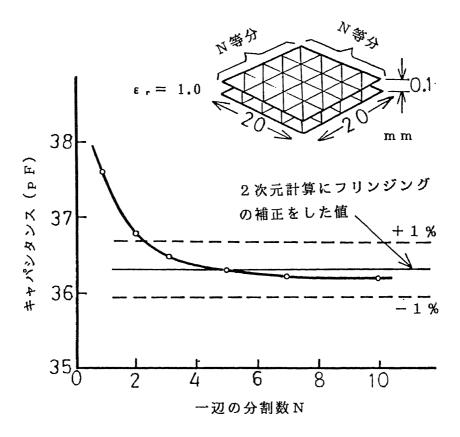

式(2.3.5)で、なるべく少ないセル数ですむように式(2.3.3)をセルi内で平均しているため、図2.3.5のように比較的粗いセル分割でもかなりの精度が得られている。ただし平均化はあくまでもセル内の電荷密度一定という条件のもとで行っているので、一般的にはこのケースのように電荷密度が(端を除いて)一定である場合に比べ、もっと細かくセル分割を行う必要がある。

伝送線の信号線とグランドの間のキャパシタンスは断面方向の寸法に比べ十分長ければ 2次元的に計算した値と一致するはずである。

図2.3.6はマイクロストリップラインの信号線とグランドの間のキャパシタンス計算値

を十分髙精度であることがわかっている2次元プログラム[98]による計算の結果と比較したもので、電荷密度が急激に変化する誘電体と信号線の接続部付近のセル分割を十分細かくすれば、セル数=230で2次元計算との差は1%以下になっている。

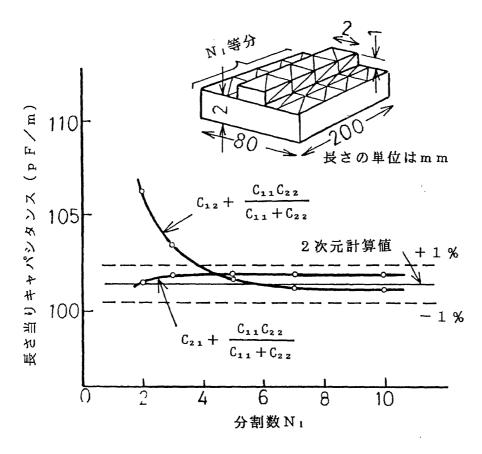

図2.3.6の形状は十分細長いので長手方向には電荷密度が一定であり、この結果長手方向にはセル分割が粗くてもよいことが期待されるが図2.3.7に示すように実際長手方向のセル分割は5分割で十分(誤差1%以下)であることがわかる(このとき断面方向の分割は、信号線表面7分割、グランド面8分割、誘電体境界面を8分割にして計算した)。

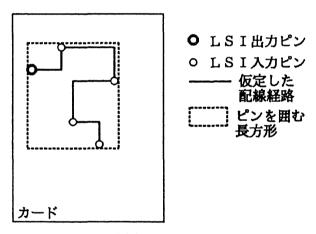

図2.3.5のように2次元的に一様な形状や図2.3.6のように長手方向に一様な形状では比較すべきデータがあるが、一般の3次元形状では正確であることが保証されている計算結果は得られていないので、実験値との直接、間接の比較が必要である。これについては2.6節に述べる。また一般の3次元形状のセル分割の細かさの定性的な目安としては、セル内で電荷密度がほぼ均一になるよう、セルサイズを最近接導体までの距離と同程度にすればよいことが経験的に言える。

図2.3.4 キャパシタンス計算の処理時間

図2.3.5 計算結果の例(平行平板)

図2.3.6 計算結果の例 (マイクロストリップライン)

図2.3.7 マイクロストリップライン容量計算値の 長手方向分割値依存性

## 2.4 インダクタンス計算手法

## 2.4.1 基本方式

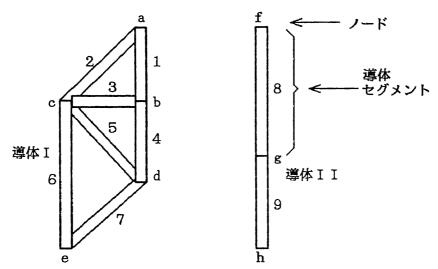

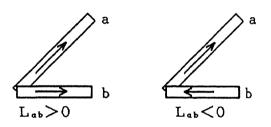

導体セグメントの部分インダクタンス計算法としては Ruehli等の方法[51][52]が知られている。以下簡単にこれを紹介する。なお表現を単純にするためこの節では部分インダクタンスを単にインダクタンスということにする。

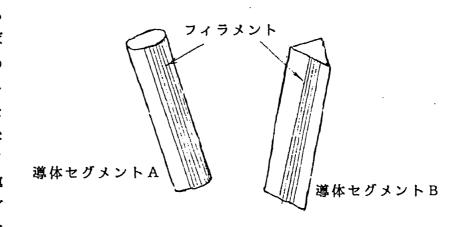

この方式は導体内の電流の方向が既知であることを前提としている。まず電流の流線に沿って導体セグメントをフィラメントに分割する(図 2.4.1参照)。フィラメントi,

図2.4.1 導体セグメントのフィラメント分割

フィラメント単位のミクロなインダクタンスから導体セグメント単位のマクロなインダクタンスを求めるには次のようにする。図2.4.1のように2つの導体セグメントA,Bがあり、フィラメント数がそれぞれn,mである場合を例にとって説明する。

導体セグメントA,Bの各フィラメントの両端の間の電位差からなるベクトルを $V_A$ , $V_B$ ,各フィラメントを流れる電流からなるベクトルを $I_A$ , $I_B$ とすると,

$$\begin{bmatrix} \mathbf{V}_{A} \\ \mathbf{V}_{B} \end{bmatrix} = \frac{\mathbf{d}}{\mathbf{d} \mathbf{t}} \{ \mathbf{L}_{ij} \} \begin{bmatrix} \mathbf{I}_{A} \\ \mathbf{I}_{B} \end{bmatrix}, \qquad (2.4.1)$$

$\{L_{ij}\}: L_{ij}$ を(i,j)要素とするn+m次の行列,

$$\mathbf{V}_{A} = \begin{bmatrix} \mathbf{V}_{A} \\ \mathbf{V}_{A} \\ \vdots \\ \mathbf{V}_{A} \end{bmatrix}, \quad \mathbf{V}_{B} = \begin{bmatrix} \mathbf{V}_{B} \\ \mathbf{V}_{B} \\ \vdots \\ \mathbf{V}_{B} \end{bmatrix},$$

V<sub>A</sub>, V<sub>B</sub>: 導体セグメントA, B両端の間の電位差

$$I_{A} = \begin{bmatrix} I_{A1} \\ I_{A2} \\ \vdots \\ I_{An} \end{bmatrix}, \quad I_{B} = \begin{bmatrix} I_{B1} \\ I_{B2} \\ \vdots \\ I_{Bm} \end{bmatrix},$$

IAi: 導体セグメントAのフィラメントiを流れる電流,

I Bi: 導体セグメントBのフィラメントiを流れる電流。

これより導体セグメントA,B両端の間の電位差と、導体セグメントA,Bを流れる電流は次の関係を満たすことがわかる。

$$\begin{bmatrix} V_A \\ V_B \end{bmatrix} = \frac{d}{dt} \begin{bmatrix} L_{MAA} & L_{MAB} \\ L_{MBA} & L_{MBB} \end{bmatrix} \begin{bmatrix} I_{AT} \\ I_{BT} \end{bmatrix}$$

(2.4.2)

ここで

$$\begin{split} &I_{AT} = \sum_{i=1}^{n} I_{Ai}, I_{BT} = \sum_{i=1}^{m} I_{Bi}, \\ &\begin{bmatrix} L_{MAA} & L_{MAB} \\ L_{MBA} & L_{MBB} \end{bmatrix} = \begin{bmatrix} N_{AA} & N_{AB} \\ N_{BA} & N_{BB} \end{bmatrix}, \\ &N_{AA} = \sum_{i=1}^{n} \sum_{j=1}^{n} L^{-1}_{ij}, \\ &N_{AB} = N_{BA} = \sum_{i=1}^{n} \sum_{j=n+1}^{n+m} L^{-1}_{ij}, \end{split}$$

$$N_{BB} = \sum_{i=n+1}^{n+m} \sum_{j=n+1}^{n+m} L^{-1}_{i,j}$$

.

式(2.4.2)は $L_{MAA}$ ,  $L_{MBB}$ がそれぞれ導体セグメントA, Bの自己インダクタンスを,  $L_{MAB}$  (=  $L_{MBA}$ ) が導体セグメントA, B間の相互インダクタンスであることを示している。

導体セグメントの抵抗が無視できない場合には式(2.4.1)のかわりに

$$\begin{bmatrix} V_A \\ V_B \end{bmatrix} = \{ Z_{ij} \} \begin{bmatrix} I_A \\ I_B \end{bmatrix}, \qquad (2.4.3)$$

ここで

$\{Z_{ij}\} = j \omega \{L_{ij}\} + \{R_{ij}\},$

$\{R_{i,i}\}$ : 対角要素  $R_{i,i}$  がフィラメントiの抵抗で非対角要素が0である行列, $\omega$ :解析しようとする角周波数,

として同様に

$$\begin{bmatrix} V_A \\ V_B \end{bmatrix} = \begin{bmatrix} Z_{AA} & Z_{AB} \\ Z_{BA} & Z_{BB} \end{bmatrix} \begin{bmatrix} I_{AT} \\ I_{BT} \end{bmatrix}$$

(2.4.4)

が得られ、 $Z_{AA}$ 、 $Z_{BB}$ の実数部がそれぞれ導体セグメントA、Bの求める周波数でのAC抵抗であり、 $Z_{AA}$ 、 $Z_{BB}$ 、 $Z_{AB}$ 、 $Z_{BA}$ の虚数部を $\omega$ で割ったものが自己、相互インダクタンスである。

#### 2.4.2 太さ0のフィラメントの採用

このアルゴリズムは従来,直方体等限られた断面形状の導体の自己,相互インダクタンス計算に利用されていたが,これを任意の断面形状を持つ対象に適用可能なよう,次のような計算方式を開発,実用化した。なおプログラム化の容易さを考慮し,導体セグメントはまっすぐな柱状とし,電流はその母線に平行である場合に限定した。曲がった導体や,太さの一定でない導体についてはこれらの導体セグメントを複数つなぎあわせて近似することにした。

式(2.2.12c)の積分はフィラメントi, jそれぞれ3次元空間について行う必要がある。このためにはまず導体セグメントを3次元的のフィラメントに分割し,これらのすべてのペアについて該当する領域内で積分を行わなければならない。これは

- (1) 計算機実装系の電気特性解析ではしばしば数十本から百本以上の導体セグメントの インダクタンス計算が必要で、それぞれについて3次元的にフィラメント分割を行うのは 煩雑な作業を必要とする。

- (2) 3 次元的なフィラメントでは式(2.2.12 c)は6重積分になって実用的な処理時間で正確に評価することがむずかしい。

の 2 つの理由で困難である。従来限られた形状以外に適用できなかったのはこの理由による。

そこでフィラメントとして太さのない線分を入力し,これからインダクタンスを計算する方式を考案した。まずフィラメントの相互インダクタンスは式(2,2,12c)より,

$$L_{ij} = \frac{\mu \cos \theta}{4 \pi} \int_{0}^{2} \int_{0}^{1} \int_{0}^{1} \frac{d l_{i} d l_{j}}{|\mathbf{r}_{i} - \mathbf{r}_{j}|} \qquad (i \neq j), \qquad (2.4.5)$$

ここで

$\theta$ : フィラメントi, jのなす角度,

$\ell_i$ ,  $\ell_i$ : フィラメントi, jの長さ.