# 多結晶 Ge 薄膜のキャリア移動度向上に関する研究

今城 利文

2022年 2月

# 筑波大学大学院博士課程

# 数理物質科学研究科博士論文

博士(工学)

多結晶 Ge 薄膜のキャリア移動度向上に関する研究

今城 利文 ナノサイエンス・ナノテクノロジー専攻

# 目次

| 第1章 序論                        | 3  |

|-------------------------------|----|

| 第 2 章 研究背景•目的                 | -  |

|                               |    |

| 2.1 IV族半導体 Ge の物性と近年の動向       |    |

| 2.2 絶縁体上における Ge 薄膜の低温合成技術     |    |

| 2.2.1 転写法                     |    |

| 2.2.2 レーザーアニール法               |    |

| 2.2.3 フラッシュランプアニール法           |    |

| 2.2.4 化学気相成長法                 |    |

| 2.2.5 固相成長法                   |    |

| 2.2.6 金属誘起成長法                 |    |

| 2.3 Ge 薄膜の固相成長に及ぼす前駆体加熱効果     |    |

| 2.3.1 非晶質 Ge 前駆体の密度変調効果       |    |

| 2.3.2 高キャリア移動度化への施策           | 19 |

| 2.4 固相成長 Ge の薄膜トランジスタ応用       | 26 |

| 2.5 研究目的                      | 32 |

| 2.6 参考文献                      | 33 |

| 第3章 固相成長 Ge 薄膜に加熱堆積が与える物性変調効果 | 41 |

| 3.1 緒言                        | 41 |

| 3.2 実験手法                      | 42 |

| 3.3 結晶性に与える影響                 | 43 |

| 3.4 光学的特性に与える影響               | 45 |

| 3.5 電気的特性に与える影響               | 46 |

| 3.5.1 キャリア起源の検討               | 47 |

| 3.5.2 キャリア輸送特性の検討             |    |

| 3.5 結言                        |    |

| 3.6 参考文献                      |    |

| 第 4 章 | 章 下部界面層挿入による Ge 結晶粒径の制御          | 55  |

|-------|----------------------------------|-----|

| 4.1   | 緒言                               | 55  |

| 4.2   | 実験手法                             | 57  |

| 4.3   | 下部絶縁層の選定                         | 57  |

| 4.4   | GeO <sub>x</sub> 下部層挿入           | 59  |

| 4     | l.4.1 Ge 膜厚変調効果                  | 59  |

| 4     | I.4.2 GeO <sub>x</sub> 下部層膜厚変調効果 | 62  |

| 4.5   | 結言                               | 69  |

| 4.6   | 参考文献                             | 70  |

| 第5章   | 章 多結晶 Ge 薄膜における歪印加の要因と影響         | 72  |

| 5.1   | 緒言                               | 72  |

| 5.2   | 実験手法                             | 73  |

| 5.3   | 応力導入機構の検討                        | 74  |

| 5.4   | 各種物性に与える影響                       | 79  |

| 5.5   | 結言                               | 82  |

| 5.6   | 参考文献                             | 83  |

| 第6章   | 章 固相成長 Ge 薄膜のフレキシブル基板への展開        | 85  |

| 6.1   | 緒言                               | 85  |

| 6.2   | 実験手法                             | 87  |

| 6.3   | 耐熱プラスチック基板上への合成                  | 88  |

| 6.4   | 結言                               | 98  |

| 6.5   | 参考文献                             | 99  |

|       | 章 結論                             |     |

|       | 本論文における主要成果                      |     |

| 7.2   | 今後の展望                            | 104 |

| 謝辞    |                                  | 107 |

| 研究第   | <b>業績</b>                        | 111 |

# 第1章

# 序論

IV 族半導体 Ge は半導体産業の草創期において活躍していた。日本初の Ge トランジスタは東京通信工業(現 SONY)が 1954 年に試作したものである。その発明を口火に、日本電信電話公社(現 NTT 研究所)が中心となって半導体産業を興し、1980 年代には世界トップシェアに輝いた。今日の我が国を経済大国へと誘った戦後日本の高度経済成長おいては、半導体産業が一翼を担う存在であったのは疑いようがない。とはいえ「盛者必衰」の言葉通り、Si の圧倒的優位性の前に Ge が凋落し、日本の半導体産業もまた斜陽化しているのは周知の事実である。

Si を大黒柱とした大規模集積回路は、微細化というレールに乗って我々に技術革新を送り届けてきた。しかし揺られて半世紀。物理的サイズの限界や Si の物性限界と対峙し始め、後進に道を譲る時も近いだろう。では我々を次世代へ運ぶポスト Si 材料は何か?取り沙汰されている候補に、一度は時代に取り残された Ge がある。再注目されている理由には、優れたキャリア輸送特性は勿論、人類が積み上げてきた Si プロセスとの親和性が大きい。さらに近年、Ge の材料的課題であった Ge/GeOx 界面不安定性やリーク電流に解決の糸口が見出されている。特に、後者に対応する絶縁体上 Ge 薄膜(GeOI)は材料希少性も同時に解決する技術である。くわえて、結晶化温度の低さを活かすことで、低耐熱ではあるが安価な汎用基板(ガラスやプラスチック)への展開も期待できる。すなわち Ge は、世界全体で IoT 化が進む中、薄膜デバイスを軸とした活路がある。

多くの研究機関がしのぎを削って低温 GeOI 技術に取り組んできた。一方、Ge 薄膜中には多量の欠陥誘起アクセプタや、粗悪な微結晶膜しか得られない問題があった。これにより、数十年間にわたってキャリア移動度は Si に及ばなかった。この背景において、当研究室では非晶質の工夫をベースとした固相成長法を構築してきた。本法により、低欠陥かつ大粒径な多結晶 Ge 薄膜

を低温合成し、そのキャリア移動度は単結晶 Si 基板を凌駕した。しかし、Ge の優れた物性ポテンシャルを活かし、民生応用を目指すならば、更なる高キャリア移動度化が望ましい。本論文では、固相成長法により合成した多結晶 Ge 薄膜に対しキャリア移動度の向上を多角的に検討する。

ここで、本論文における章構成を記す。本章につづき、第 2 章では、研究の背景・目的として、Geの物性と近年の動向、ならびに低温 GeOI 技術と我々の固相成長 Ge 薄膜の発展を説明する。第 3 章では、Ge の固相成長における各熱処理過程が物性に与える影響を包括的に議論する。続く第 4 章では、固相成長 Ge 薄膜の更なる高キャリア移動度化を検討し、下部層挿入を検討する。そして第 5 章では、歪導入機構と物性への影響を紐解く。第 6 章では、これまで為し得なかったフレキシブル基板上への高移動度 Ge 多結晶薄膜を実証する。最後の第 7 章で本論文を総括する。

低温 GeOI における我々の固相成長技術は、品質・プロセスの観点でも実用に最も近い位置に あると考えられる。本論文の知見が、再び脚光を浴びつつある Ge の復活を後押しすると共に、日 の丸半導体の再興の切り札となれば幸いである。

# 第2章

# 研究背景•目的

### 2.1 IV 族半導体 Ge の物性と近年の動向

半世紀のうちに人類は「驚くべき快挙」と称するに相応しい繁栄を築いた。かつてからは想像もつかない、夢のような機能を持つ電子デバイスに囲まれた豊かな生活に浴している。それはひとえに半導体の恩恵によるところが大きい。それらはどのように始まり、そしてどのように発展していったのだろうか。本節では、半導体産業の黎明期におけるトランジスタ利用に始まり、次世代デバイス材料としての価値が近年再興している Ge の物性と近年の動向を織り交ぜて記す。

Ge とは、Si や Sn と同じ IV 族に属する間接遷移型の元素半導体である。現在より遡ること 75年前、Ge 単結晶を用いてトランジスタの増幅作用が初めて観測された。半導体産業の先駆けとなった重要な存在である。そのしばらく後、金属-酸化物-半導体電界効果型トランジスタ (MOSFET) が産まれ、それを基幹素子とした大規模集積回路 (VLSI) に半導体産業が牽引されてきた¹。その進化の過程における Ge の立ち位置は悪かった。0.66 eV という小さな禁制帯幅が高温動作の難しさを産んだ。さらに、絶縁界面層に用いたい GeOx が潮解性を持つ上に、これを用いた Ge との界面品質が乏しく、MOSFET の電荷輸送に悪影響を及ぼした。くわえて Ge はレアメタルでもある。対する Si は上記問題を容易に乗り越えてきた。Ge よりも熱安定性が高く、さらにはシンプルな熱酸化により形成される SiO2 が卓越した Si/酸化物界面特性を提供した。地殻埋蔵量も極めて高く、産業的にも嬉しい。これらの明確な利点によって、半導体産業の花形である MOSFET の主役には Si が選ばれ、一方の Ge は退くこととなった。

さて、MOSFET の性能はスケーリング則によって①低消費電力化、②高速化、③高集積化という 3 要素を同時に達成してきた。これは MOSFET の 3 次元的なサイズダウンと電圧低減、そして不 純物濃度の増加で得られる<sup>2</sup>。とはいえ本法則も2006年頃に物理的な微細化限界とSiの材料特 性の限界と対峙し始めた。しかし、MOSFET 設計で重要な要素となるゲートスタック、チャネル等 に注目した「ポスト・スケーリング」技術を携え、MOSFET は今もなお進化し続けている。ゲートスタ ックに関しては、ゲート酸化膜が nm オーダーになると、量子力学的な要因(トンネル電流によるリ ーク)が浮上する。そこで SiO2 から離れ、高誘電率(high-k)材料を用いれば、「電気的な膜厚」を 薄くしつつ物理的な膜厚を大きくできる。チャネルに関しては、高度に培ってきた Si プロセスを活 かすために、歪導入によるキャリア輸送特性の向上が為されてきた。しかし歪みの印加量には限 界もある。そこで、「ゲートスタックが high-k ならばチャネル材料も代替ししてはどうか」とのアイデア が浮上した。高キャリア移動度を有する半導体材料を表 2.1 にまとめる 3.4。化合物半導体は電子 移動度が突出している。一方、両極性キャリア移動度の調和平均を考えると、バランスが優れてい るのは Ge となる。 VLSI で論理回路を担う相補型 MOSFET の設計において、高集積化には両極 性の MOSFET を同程度のスケールで構成することが鍵となる。 化合物半導体は p型 MOSFET に おいて他材料の助けが要りそうだが、Geならば単一材料で実現できる。これにより煩雑なプロセス を取り払い、コスト削減もできる。さらには無毒である。そして IV 族半導体であるため、これまで人 類が培ってきた Si プロセスとの相性も良い。

表 2.1 高キャリア移動度を有する半導体薄膜の物性値.

|                                                          | Si   | Ge   | GaAs | InAs  | InSb  |

|----------------------------------------------------------|------|------|------|-------|-------|

| 電子移動度 [cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | 1500 | 3900 | 9200 | 40000 | 77000 |

| 正孔移動度 [cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | 450  | 1900 | 400  | 500   | 850   |

| キャリア移動度の<br>調和平均 [cm² V-1 s-1]                           | 692  | 2555 | 767  | 988   | 1681  |

| 禁制帯幅 [eV]                                                | 1.12 | 0.66 | 1.42 | 0.36  | 0.17  |

先に述べた通り、Ge はその狭い禁制帯幅に起因したリーク電流や MOSFET 応用時のゲートスタックの困難さという隘路により VLSI の主役を Si に譲って来た。しかし、ポスト Si としての存在感が高まっている近年、ゲートスタックの改善(Ge/酸化物界面の克服)により Si ユニバーサルカーブを打破し、数倍の電界効果移動度を有する Ge-MOSFET が実現されている <sup>3,5</sup>。また、絶縁体上 Ge 薄膜(GeOI)技術によりリーク電流を抑制し、優れた ON/OFF 特性も実証された <sup>6</sup>。世界の CPU トップシェアを有する Intel が CPU に Ge-MOSFET を組み込むとの報 (IEDM2019)もあり、産業界からの追い風も強い。次世代チャネル材料として Ge が広まる土壌は豊かである。

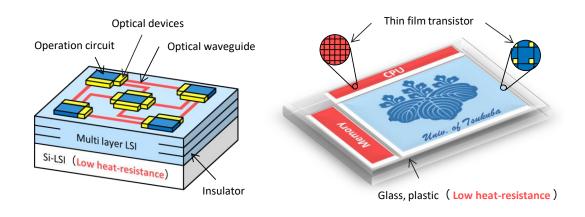

GeOI 技術に注目しよう。リーク電流を抑える技術として効果的であるが、レアメタルである Ge にとっては資源節約の観点も特筆すべきである。また、Ge は結晶化に必要な温度が低い(<500°C)という特徴をもつ。もし、耐熱温度は低いが廉価な絶縁基板上(ガラスやプラスチック)に高品質なGe 薄膜を実現できれば、応用の幅は飛躍的に広がる。すなわち、Ge は薄膜デバイスに活躍の場がある。これまでトランジスタ応用を切り口に論じてきたが、Ge の優れた光学的特性(高い光吸収係数 <sup>7</sup> や中赤外透過性)に着目した光学デバイス応用 <sup>8</sup> も魅力である。Ge を軸にした光電素子を集約することで、3 次元 LSI の性能向上・付加や多機能ディスプレイといった革新的デバイスの実現も期待できる(図 2.1)。以上のように、主役を Si に一度譲った Ge であるが、ポスト Si 材料として存在感を高めている。この事実を鑑みれば、正に「ルネサンスな」材料であると言えるだろう。

図 2.1 次世代デバイスの概要. (左)3 次元 LSI. (右)多機能ディスプレイ.

### 2.2 絶縁体上における Ge 薄膜の低温合成技術

前節で述べた通り、薄膜デバイスにおける Ge の存在感が勃興している。特に、ありふれた基板への低温合成を目指し、数多の手法が研究されてきた。本節では代表的な GeOI 低温合成技術を記す。

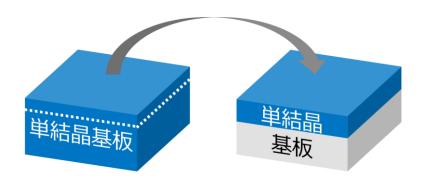

#### 2.2.1 転写法

活性化した単結晶基板の表面を、目標基板と接合させることで Ge 薄膜を転写する。単結晶基板とほぼ同質の Ge 薄膜が得られ、面方位の自由度も高い。張り合わせ法 <sup>10-13</sup> やイオンカット(スマートカット)法 <sup>14,15</sup> が知られている。関連するウエハ絶縁分離技術に、単結晶基板に酸素をイオンインプランテーションし、事後のアニールにより埋め込み酸化膜(絶縁層)を形成する方法(SIMOX: Separation by implantation of oxygen)がある <sup>16,17</sup>。転写法を基盤とし、GeOI デバイスの研究にも力が注がれている <sup>12</sup>。一方、本手法は基板サイズに制限されるため、大口径化が困難である。くわえて、アイデアは単純である一方で行程が複雑であり、高いコストを要する。これらは産業応用の障壁となる。従って、以下に述べるような直接形成法が注目を浴びている。

図 2.2 転写法.

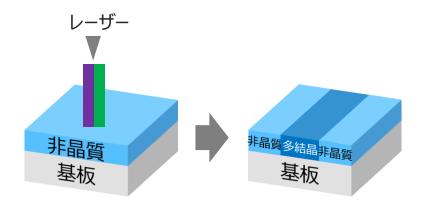

#### 2.2.2 レーザーアニール法

試料表面にレーザーを照射して、溶融・急速冷却(固化)による非熱平衡成長を誘起する。レーザー波長と対象材料の光吸収係数の兼ね合いで侵入長を変調できる。膜が充分にレーザーを吸収する、あるいはプロセスが極めて短い(≤ミリ秒)ため、基板へのダメージは殆ど無い<sup>18</sup>。使用される波長には、紫外(excimer)や緑色(Nd:YAG)等がある。発振動作はパルス <sup>19-21</sup>と連続波 <sup>22</sup>に大別される。本技術によって μm オーダーの結晶粒を持つ多結晶 Ge 薄膜や、Ge-TFT 応用も報告されている <sup>23,24</sup>。しかし、液相 Ge の輸送が顕著な表面凹凸を引き起こし、デバイス特性や歩留まりに悪影響をもたらす。さらに、大面積一括形成が困難であり太陽電池応用には不向きである。

図 2.3 レーザーアニール法.

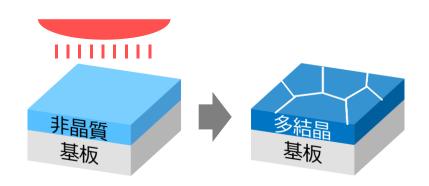

#### 2.2.3 フラッシュランプアニール法

Xe ランプを対象試料にミリ秒程度フラッシュする。処理時間が極めて短く、基板への熱拡散が抑えられる。瞬時に試料表面のみを高温(数千度)にすることで溶融・固化を行い、結晶化を促す非平衡過程である  $^{18}$ 。不純物の拡散を抑えつつ活性化を両立できることから、微細 Si プロセスにも期待されている。ドーパントが拡散しやすい Ge でも極浅接合と高い活性化率が報告されている  $^{25}$ 。一方で、面直方向に大きな熱勾配が発生し、応力が印加される。応力緩和の過程で膜や基板に物理的損傷が導入されるリスクがある  $^{26}$ 。絶縁体上多結晶 Ge(Sn) 薄膜の合成は産総研  $^{27,28}$  や大阪大  $^{29}$  からの報告がある。前者の合成膜は高い正孔密度( $2\times10^{18}$  cm $^{-3}$ )を示すが、その高配向性から優れた正孔移動度(200 cm $^{2}$   $V^{-1}$  s $^{-1}$ )を有する  $^{28}$ 。

図 2.4 フラッシュランプアニール法.

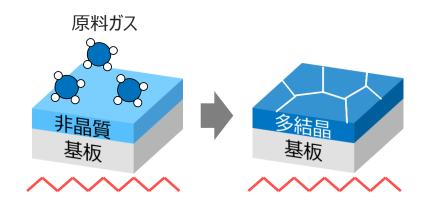

#### 2.2.4 化学気相成長法

構成元素からなる化合物ガスを基板上に供給し、気相または基板表面での熱化学反応により薄膜を形成する。低耐熱基板への低温合成 (< 500 °C)も可能である。プラズマの併用により更に低温 (~200 °C) での成長も可能となる  $^{30}$ 。堆積時の基板温度によって結晶相を選択できる。従来の研究では、得られる結晶粒は極めて小さい (< 200 nm)  $^{30-32}$ 。香港城市大学のグループでは、小粒径 (< 1  $\mu$ m) でありながらも優れたキャリア輸送特性 (~300 cm²  $V^{-1}$  s $^{-1}$ )を示す多結晶 Ge 薄膜を実証している  $^{33,34}$ 。

図 2.5 化学気相成長法.

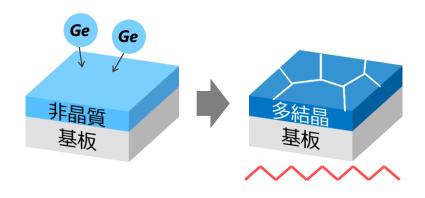

#### 2.2.5 固相成長法

図 2.6 固相成長法.

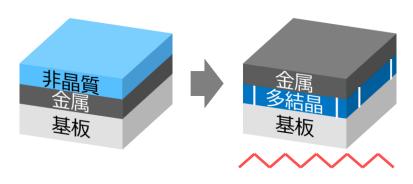

#### 2.2.6 金属誘起成長法

熱処理により Ge 中への金属拡散を誘起する。非晶質 Ge は通常 500 ℃ 付近で結晶化するが、金属の触媒作用により、100 ℃ 以上結晶化温度を低減できる <sup>45</sup>。特に Sn を用いると 70 ℃ で結晶化する <sup>46</sup>。高配向な多結晶薄膜も得られ、擬似単結晶としても期待できる。低温プロセスを活かした低耐熱基板 (ガラス、プラスチック) への展開が盛んである。TFT<sup>47-53</sup> や熱電素子 <sup>54-58</sup> といった実デバイス応用も多い。特殊な成長モードに層交換成長と横方向成長がある。以下に記す。

#### A. 層交換成長

Ge と金属が合金を形成する場合に見られる 57,59-63。特に Al,Ag,Au,Zn が盛んに研究され、実 デバイス応用もなされている。金属膜中に固溶限以上の Ge 原子が拡散すると、過飽和に達する。 結晶状態の Ge が析出し、初期核として横方向に結晶成長する。このとき金属が押し出される。このような過程により、Ge と金属が位置を交換 (=層交換)し、多結晶 Ge 薄膜が形成される。結晶化が低温であること ( $\le 250\,^{\circ}$ C)、エピタキシャル法ではなくとも高配向する (Au, Al) のが特徴である。 その高い配向性を活かし、Ge は元より III-V 族半導体等のエピタキシャルテンプレート応用がされている 64-67。一方、結晶化機構に起因した固溶限相当の金属が Ge 中に存在することになる。電気的特性に比較的影響が少ない Ag や Au は、擬似単結晶と見なせる Ge 薄膜の合成例もあり、TFT 動作もなされている 51-53。p 型ドーパントとして作用する Al や Zn は、自己組織的な高濃度ドーピングにより熱電応用が行われている 54-58。その知見から、アクセプタとして作用しない Ag や Au に対し不純物を添加することで、低温プロセス( $\le 500\,^{\circ}$ C)で優れた熱電特性が達成されている 68-70

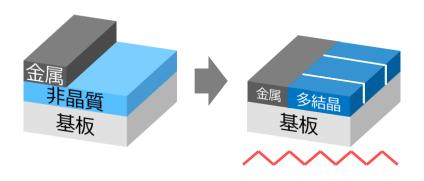

#### B. 横方向成長

金属と化合物を形成し、エピタキシャル関係を活かした樹状成長が発現する。一方、共晶系の Sn や Au 等でも確認されており、共晶系における詳しいメカニズムは未開拓である。本節では、Si に Ni 触媒を利用した代表的な化合物系に触れる  $^{71}$ 。NiSi₂/Si 間のエピタキシャル関係を活かし、 高配向な単一粒を薄膜面内方向に低温成長できる。その機構から、結晶粒はキャリア輸送に関 与しづらい低角粒界を形成する  $^{72}$ 。同じ IV 族半導体である Ge にも各種金属の応用が検討されている  $^{73-75}$ 。しかし、得られる結晶粒は極めて小さく(<  $10~\rm nm$ ) デバイス応用に堪えない粗悪膜である。これは Ge が本質的に微結晶化しやすい性質に起因するとされる。当研究室では、前駆体となる非晶質 Ge の加熱堆積(後述)の重畳し、Ni 誘起成長を検討した。その結果、電子後方散乱回折法で検出可能な横方向成長 Ge 結晶  $(2\times10~\rm \mu m)$  を初合成した  $^{76}$ 。

図 2.7 金属誘起層交換法.

図 2.8 金属誘起横方向成長法.

### 2.3 Ge 薄膜の固相成長に及ぼす前駆体加熱効果

これまで述べてきた通り、多結晶 Ge 薄膜の絶縁体上への低温・高品質・直接合成に向け、多くの研究機関がしのぎを削ってきた。しかし、未だ単結晶 Si を超えるキャリア移動度 (> 450 cm $^2$  V $^{-1}$  s $^{-1}$ ) 76 が得られていない。近年、当研究室では固相成長 Ge において、前駆体となる非晶質の密度に注目し、多結晶 Ge 薄膜のキャリア移動度を刷新してきた。本節ではその詳細を記す。

#### 2.3.1 非晶質 Ge 前駆体の密度変調効果 <sup>77</sup>

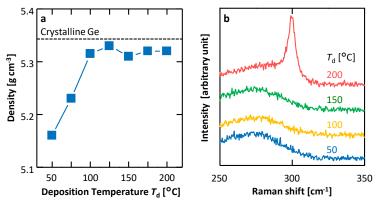

本研究は、固相成長の前駆体となる非晶質の堆積時熱処理が、成長層に与える影響を調査したものである。非晶質 Ge(100 nm)を  $SiO_2$  ガラス上に加熱堆積した。その結果、堆積温度  $(T_d)$  が上昇するにつれて、非晶質密度が結晶の値に漸近する (図 2.9(a))。これは以下の様に考えられる。基板に付着した原子が熱によって移動する。この時、非晶質相よりも結晶相のエネルギーが低い。従って、系全体のエネルギーを安定させるため、原子間距離、すなわち非晶質密度が結晶に近づいたと推察される。また Raman 分光法により、前駆体は  $T_d = 200$  °C において結晶 Ge 起因のピークを示した (図 2.9(b))。すなわち、比較的高温で堆積することで堆積時に結晶化することが判った。

図 2.9 (a) 前駆体密度. (b) Raman スペクトル.

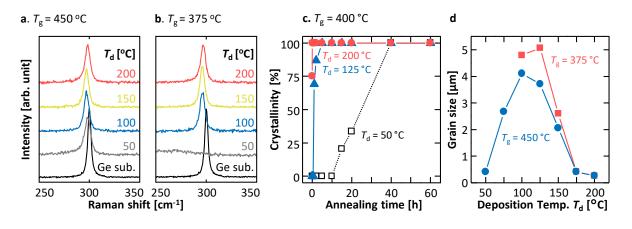

続いて、固相成長後の成長層に対し各種評価を行った。 $T_d$  の影響を、熱処理温度 ( $T_g$ ) の変調効果も併せて Raman 分光法で調べた。その結果、 $T_d$ =50 °C で低温成長 ( $T_g$ =375 °C)した場合のみ結晶 Ge 起因のピークが得られなかった (図 2.10(a),(b))。そこで、非晶質 Ge と結晶 Ge のRaman ピーク強度比から結晶化度を見積もり、時間に対してまとめた (図 2.10(e))。 $T_g$  は 400 °C とした。その結果、高  $T_d$  ほど成長速度も高いことが判った。電子後方散乱回折 (EBSD) 法により Ge 成長層の結晶粒径を確認すると、加熱堆積 ( $T_d$ =125 °C)により大粒径化していることが判る (図 2.10(d))。結晶粒径を $T_d$  に対し整理した。 $T_d$ =100 °C において粒径は最大値を取り、その後  $T_d$  の増加とともに減少に転じた。このとき、結晶粒径が最大となる点は非晶質前駆体の密度が結晶に漸近する堆積温度に対応する。また、結晶粒径は熱処理温度 ( $T_g$ ) の低下よって拡大し、最大で 5  $\mu$ m に達した。一方で、 $T_d$  > 150 °C の Ge 成長層では、結晶粒径の  $T_g$  依存性が見られなかった。この結果は、結晶粒径が堆積時に決定されることを示唆している。

図 2.10 (a)  $T_g = 450$  °C および(b) 375 °C の Raman スペクトル. (c) 結晶化率. (d) 結晶粒径.

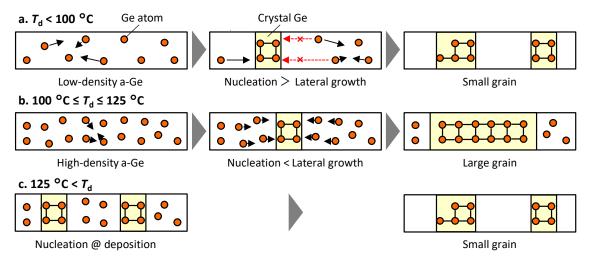

前駆体非晶質の密度、各相のラマンスペクトル、固相成長過程の結晶化率、および固相成長後の結晶粒径より、堆積した前駆体を「①低密度な非晶質、②高密度な非晶質、③堆積時に結晶化」の3領域に分類した。各領域における成長モデルの概要を示す。固相成長では、非晶質を熱処理することで結晶核が発生し、それらが原子を取り込むことで成長し、やがて膜全面が結晶化する。よって、結晶粒径は、結晶核の生成速度(核生成頻度)と結晶の成長速度(横方向成長速度)のバランスによって決定される。遅い核生成頻度と高い横方向成長速度により、大粒径化が見込める。核生成頻度は、堆積温度に依存する。また、非晶質が高密度であるほど、結晶相への遷移の際、原子間距離の適性化に要するエネルギーは少ない。従って、非晶質密度が横方向成長速度と相関する。すなわち、「堆積時の結晶核生成を抑制しつつ、高密度な非晶質」という状態が固相成長の前駆体としては望ましいと考えられる。以上から、前駆体非晶質の密度を結晶の密度に近づけることで、結晶成長の速度が増加し、劇的な大粒径化が見られたと推察される。一方で、堆積時に結晶核が発生している領域では、固相成長後の結晶も小粒径化したと考えられる。

図 2.11 各前駆体密度領域における結晶成長の模式図.

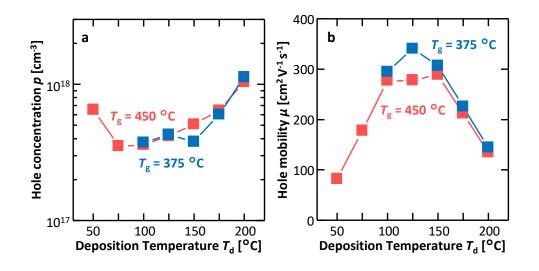

続いて、電気的特性の評価結果を図に示す。合成した固相成長 Ge 薄膜はノンドープでも p 型 伝導を示した。同様の報告が先行研究でもなされており、Ge 結晶中の空孔欠陥に起因するとされている  $^{78,79}$ 。正孔密度は  $T_{\rm d}$ に応じて変化した。結晶粒径が大きい Ge 成長層ほど低い値となった。また、キャリア移動度の向上も見られた。特に、 $T_{\rm d}=125\,^{\circ}{\rm C}$ 、 $T_{\rm g}=375\,^{\circ}{\rm C}$  で固相成長を誘起した際に 340 cm²  ${\rm V}^{-1}$  s<sup>-1</sup> に達した。すなわち、大粒径化に伴う粒界散乱の低減により、良好なキャリア伝導特性を達成できたと考えられる。以上、 ${\rm SiO}_2$  ガラス上に従来よりも優れた多結晶 Ge 薄膜を低温・直接合成することに成功した。

図 2.12 電気的特性. (a) 正孔密度 p および(b) 正孔移動度 μ.

#### 2.3.2 高キャリア移動度化への施策 80-83

固相成長 Ge 薄膜において、前駆体非晶質の加熱堆積を新プロセスとして採用した。前駆体 Ge は「非晶質状態のまま」高密度化した。その結果、結晶化過程における横方向成長速度が向上し、従来法より 1 桁以上大きな結晶粒径( $\sim$ 5  $\mu$ m)を達成した。結晶粒界での散乱が緩和され、高キャリア移動度 340 cm² V⁻¹ s⁻¹ を有する多結晶 Ge 薄膜を SiO₂ ガラス上に実現した  $^{77}$ 。その後も本知見をベースとして更なるキャリア移動度の向上を目指し、多くの手法が検討され、そして更新してきた。本節ではそれらを記す。

#### A. 厚膜化 80

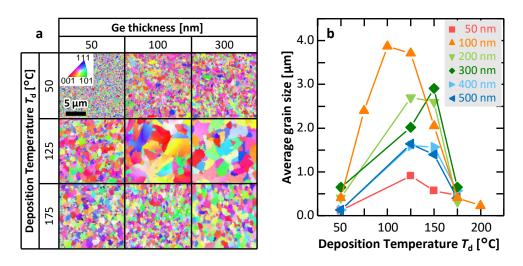

前節では非晶質 Ge 層の膜厚を 100 nm に固定していた。膜厚変調は結晶成長や物性に大きな影響を与えうる。また、固相成長の先行研究でも厚膜化の有用性が報告されている  $^{42}$ 。そこで、Ge 膜厚を 50-500 nm と変調し、それらの  $T_{\rm d}$  依存性を調査した。まず EBSD 法によって結晶粒径を確認すると、結晶粒径は 100 nm で最大となり、その後の膜厚増加と共に減少することが判る(図 2.13)。また、Ge 膜厚が 50 nm の場合も小粒径と成った。前者は、膜厚増加に伴い結晶核生成サイトが増加(=初期核生成頻度の増加)したことに起因する。また後者は、応力の影響で非晶質密度が向上せず結晶化速度が低下したと考えられる。また、粒径が最大となる  $T_{\rm d}$  は薄膜(<100 nm)から厚膜(>200 nm)となるにつれて高温にシフトした。これは、非晶質密度が向上する温度が高 $T_{\rm d}$  側にずれたことに由来する。続いて電気的特性を図 2.14 に示す。厚膜化に伴う正孔密度の低減、移動度の向上を確認できる。これは、結晶性の悪い界面領域の影響が減少することに起因すると考察されている。

図 2.13 EBSD 解析. (a) IPF 像. (b) 結晶粒径.

図 2.14 電気的特性. (a)正孔密度 p および(b)正孔移動度 μ.

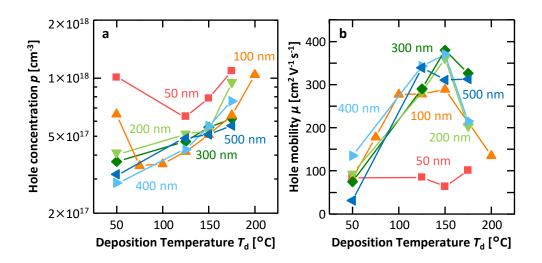

#### B. ポストアニール(PA) 80

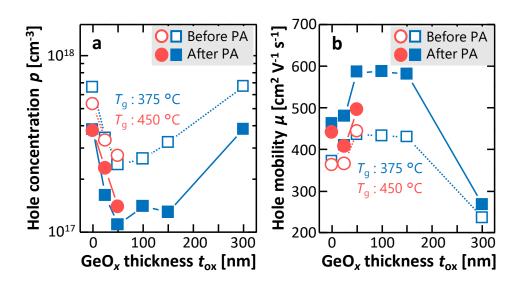

結晶化後、更に高温の熱処理を行うことで原子拡散を誘発する。それにより、多数キャリアである正孔の起源とされる結晶 Ge 内部の欠陥補償が期待できる。実際に固相成長 Ge 薄膜の先行研究で電気的特性に好適な効果がみられている  $^{81}$ 。本研究では、前項において各膜厚で最高移動度を示した Ge 成長層に対し、Ar 雰囲気中において PA  $(500\,^{\circ}\text{C}, 5\,\text{h})$  を行った。空孔補償により、全膜厚において正孔密度を低減した。さらに、400 nm の成長層において正孔移動度 450 cm $^{2}$  V $^{-1}$  s $^{-1}$  を記録した (図 2.15)。

図 2.15 電気的特性. (a) 正孔密度 p および(b) 正孔移動度  $\mu$ .

#### C. 焼締<sup>84</sup>

PAによってキャリア移動度が向上したことから、固相成長 Ge は不純物散乱にも律速されていると示唆される。従って、Ge 自体の結晶性を向上(=欠陥低減)すれば電気的特性の向上が期待できる。そこで、Ge 非晶質前駆体を加熱堆積した直後に真空チャンバー内部で熱処理を行う焼締(PDA: Post-deposition annealing)プロセスを導入した。本プロセスは、真空中で膜を緻密化し、大気暴露時の酸素混入を防ぐ狙いがある。ここで、酸素は結晶化を抑制する 82.83 ため、大粒径化や欠陥低減が見込める。しかし実際に焼締を施行した結果、結晶粒径は減少し、それに伴い正孔密度は増加した。一方、PAを行うことで正孔移動度は小粒径ながらも 530 cm² V-1 s-1 に至った。すなわち、高キャリア移動度の実現には不純物散乱や粒界散乱のバランスが重要との知見を得た。

図 2.16 (a) 結晶粒径. (b) 正孔密度 p および(c) 正孔移動度 μ.

#### D. Sn 添加 85

同族元素である Sn の微量添加は Ge に魅力的な作用を及ぼす。代表的なものは、高 Sn 置換条件下  $(>6\%)^{86}$  で Ge のバンド構造が変化するものである。間接遷移型であった Ge が直接遷移化すると共に、輸送キャリアの有効質量が減少する。これにより、発光・受光デバイスや電子デバイスに好的な特性  $^{86}$  を持つこととなる。また 2.2.5 節で述べた通り、成長温度低減  $^{86}$  や Ge 空孔アクセプタ補償  $^{87}$ 、結晶粒径の拡大  $^{40,42}$  など結晶成長にも多くの利点をもたらす。これらを活かすことで、正孔移動度 320 cm² V-1 s-1 を有する固相成長 GeSn 薄膜が報告されている  $^{42}$ 。しかし、この研究では、前駆体非晶質を高密度化していない。すなわち、我々の技術を融合することで更なる向上が見込める。本節では、我々の固相成長法に Sn 添加を重畳した結果を報告する。

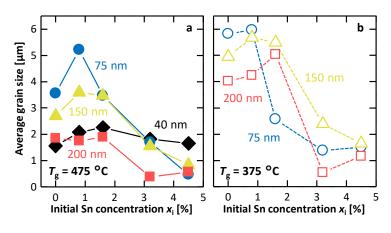

GeSn 膜厚を 75-2000 nm と変調した。また、熱処理前の Sn 組成 (初期 Sn 組成  $x_i$ ) は 0-4.5 % で制御した。また、2 通りの結晶化温度  $T_g$  (375, 475 °C)を採用した。まず、EBSD 法で結晶粒径を評価した。膜厚増加と共に 75 nm で最大粒径となり、その後減少した(図 2.17)。小粒径化は、薄膜領域 (40 nm) では前駆体が低密度であること、厚膜領域 ( $\geq$ 150 nm) では核生成サイトの増加に起因する。特に前者の影響は低温成長時に結晶化が完了しない形で顕著に表れた。続いて  $x_i$  に注目する。 $x_i$  の増加と共に粒径は拡大し、その後減少した。これらは格子置換した Sn の観点で説明できる(次項)。

図 2.17 結晶粒径. (a) T<sub>g</sub>=475 °C および(b) T<sub>g</sub>=375 °C.

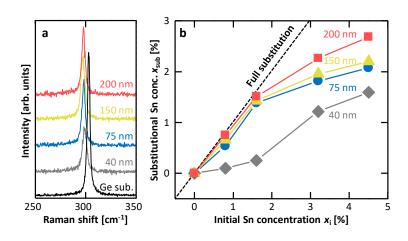

Raman 分光法を用い、実際に Ge 格子に取り込まれた Sn(置換 Sn 組成  $x_{sub}$ )を調査した。まず、 $x_i = 1.6$ %とした GeSn 成長層 ( $T_g = 475$  °C)の Raman スペクトルを示す (図 2.18(a))。結晶 Ge 由来のピークは、単結晶基板のものから大きく低波数シフトしている。これは、成長時導入歪に加えて Sn 導入に伴うものである。このピークシフトを用いて  $x_{sub}$  を見積もり、置換割合 ( $x_i$  に対する  $x_{sub}$ )を整理した  $x_{sub}$  を整理した  $x_{sub}$  を整理した  $x_{sub}$  を整理した Sn が極めて高く置換する傾向を見せた。これは Sn 固溶限の既報に符合する  $x_{sub}$  と  $x_{sub}$  と  $x_{sub}$  と  $x_{sub}$  と  $x_{sub}$  を  $x_{sub}$  を  $x_{sub}$  を  $x_{sub}$  と  $x_{sub}$  を  $x_{sub}$  を  $x_{sub}$  を  $x_{sub}$  を  $x_{sub}$  を  $x_{sub}$  を  $x_{sub}$  と  $x_{sub}$  を  $x_{sub}$  を  $x_{sub}$  と  $x_{sub}$  を  $x_{sub}$  と  $x_{sub}$  を  $x_{sub}$  を x

図 2.18 (a) Raman スペクトル. (b) x<sub>sub</sub> の x<sub>i</sub> 依存性.

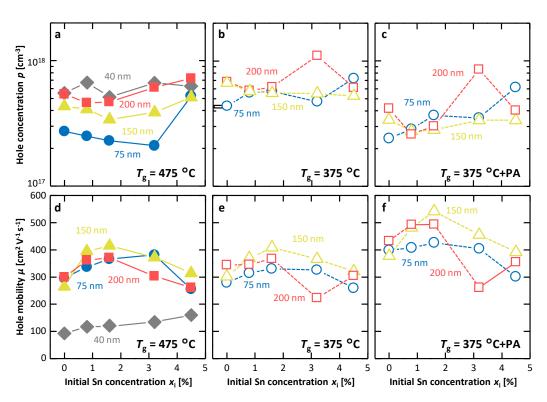

最後に電気的特性を示す。Sn 添加した固相成長 Ge 薄膜も、欠陥誘起アクセプタに伴うp型伝導を示した(図 2.19(a)(b))。微量な Sn 添加は結晶粒径にくわえて、p と $\mu$  の双方に好適な影響を及ぼした。興味深いことに、高温成長した場合は小粒径であったのに関わらず、比較的高い  $\mu$  と成った(図 2.19(d))。粒界散乱の影響が少ないことが推察される。

低温成長 (375 °C) した GeSn 成長層に対して PA を施した (図 2.19(c)(f))。その結果 p を効果 的に低減するとともに  $\mu$  も向上した。特に 150 nm において  $\mu$  = 540 cm² V<sup>-1</sup> s<sup>-1</sup> を達成した。これらは、適切な Sn 添加によるパッシベーションと結晶粒径の拡大、そして厚膜化による界面散乱の低減を反映したものであると考えられる。

図 2.19 電気的特性. (a),(d)  $T_g$  = 475 °C, (b),(e)  $T_g$  = 375 °C および(c),(f)  $T_g$  = 375 °C+PA における(a)-(c) 正孔密度 p ならびに(d)-(f) 正孔移動度  $\mu$ .

### 2.4 固相成長 Ge の薄膜トランジスタ応用 95

固相成長 Ge の薄膜トランジスタ応用に先立ち MOSFET を倣う。MOSFET の設計ではソース (S)/ドレイン(D)が重要な要素の一つとなる。通常の Si-MOSFET は S/D が自己整合的に形成されており、寄生抵抗が極めて小さい。続いて Ge がチャネル材料である場合を考える。Ge はドーパント作用がある不純物(13 族や 15 族)の固溶度が Si と比して低い 3,95,96。さらに、n 型ドーパントは極めて高い拡散係数を有する 97。これにより、Ge においては高い整流性(極浅かつ高濃度)を有する p/n 接合を形成するのが困難となる。従って、金属 S/D を用いたショットキー接合を利用する代案がある。しかし、Ge はフェルミレベルピニングという特異な現象が発生し、金属のフェルミ準位が Ge の価電子帯頂上近傍にピン止めされる 77,80-83。これにより、n-Ge はショットキー性が取りやすい一方、p-Ge ではオーミック性となってしまう。最近、本間題は解決の指針が示されているが98、オーミック性を受け入れて、低い正孔障壁高さを示す金属/p-Ge 接合を用いれば、ノンドープで p 型となる多結晶 Ge 薄膜が生かし易い 80。すなわち、S/D エンジニアリングの観点では、反転動作(整流性、少数キャリア駆動)ではなく通常の TFT に代表される蓄積動作(オーミック性、多数キャリア駆動) 設計により容易なデバイス実証が期待できる。

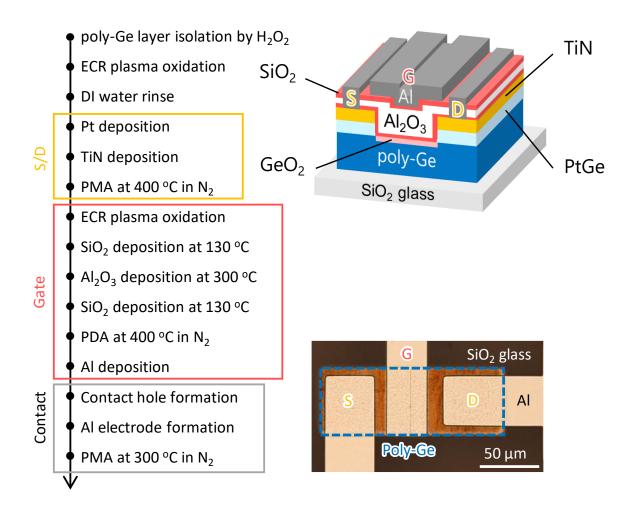

前節まで述べてきた通り、我々は多結晶 Ge 薄膜の最高移動度を更新してきた  $^{99}$ 。本章では、本法で得た高いキャリア移動度を有する Ge 薄膜を TFT 応用することで、膜特性とデバイス特性の体系化を検討した報告をまとめる。合成膜のデバイス化にあたり、Ge-MOSFET の低温作製プロセスに高い実績を誇る  $^{76,100,101}$  九州大学と共同研究を行った。図 2.20 に示す手法で、固相成長 Ge 薄膜 (初期膜厚  $t_i$ : 25-200 nm,堆積温度  $T_d$  = 125 °C,結晶化温度  $T_g$  = 450 °C)をベースとしたメタル S/D 型蓄積動作 p チャネル TFT (チャネル幅 W: 55  $\mu$ m,チャネル長 L: 5-15  $\mu$ m)を作成した。

図 2.20 Ge 薄膜トランジスタの作製プロセスおよび光学顕微鏡像.

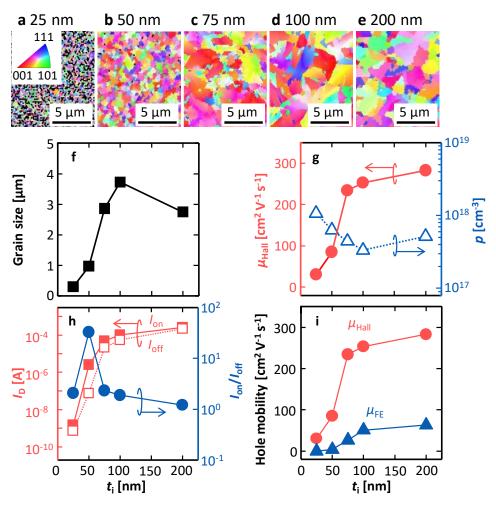

TFT 作製に先立ち、膜特性を評価した。結晶化後の結晶状態を EBSD 法で評価したところ、粒 径が t<sub>i</sub>によって劇的に変化していることが判る(図 2.21(a)-(e))。 結晶粒径は、t<sub>i</sub> = 100 nm で最大と なった(図 2.21(f))。薄膜側における小粒径化は、前駆体密度が向上しないことに起因する <sup>23,51,53,102-107</sup>。また、ti = 200 nm における小粒径化は、核生成サイトの増加に起因する。続いて、 Hall 効果測定によって電気的特性を評価した(図 2.21(g))。小粒径な成長層ほど高い正孔密度 pを示した。 すなわち、 結晶粒界が p の原因となっていることが示唆される。 粒径は  $t_i = 100$  nm でピ 一クを取ったが、正孔移動度  $\mu_{\text{Hall}}$  は  $t_i = 200 \text{ nm}$  で最大となった。この挙動は、 $\text{Ge/SiO}_2$  界面付近 でのキャリア散乱に起因すると考えられる 42。 続いて、これらの合成膜を TFT 化した。 ti とともにオ ン電流  $I_{ON}$  が増加することを示しており、これは  $\mu_{Hall}$  を反映している (図 2.21(h))。 さらに、 $t_i$ とともに オフ電流 Ioff も増加した。 蓄積動作型 TFT では、空乏層により OFF 状態を形成する。ここで、最 大空乏層幅 $d_{\text{max}}$ はチャネル領域の多数キャリア密度に決定される。すなわち $d_{\text{max}}$ と $t_i$ の関係から、 ti が低いほど固相成長 Ge 層における空乏層の占有率が高くなり、IoFF が減少すると考えられる。  $I_{ON}$ と  $I_{OFF}$  のバランスを反映し、オン/オフ電流比  $I_{ON}/I_{OFF}$  は  $t_i$  = 50 nm で最大となった。図 2.21(i) から、電界効果移動度  $\mu_{\text{FE}}$  は  $\mu_{\text{Hall}}$  の傾向と一致するが、 $\mu_{\text{Hall}}$  より遥かに低い。これは、MOS 界面 でのキャリア散乱だけでなく、Ioff が大きいために伝達コンダクタンスや μfe が過小評価されるため だと考えられる。従って、高い TFT 特性を得るためには、膜を完全空乏化する条件で、高い μ<sub>Hall</sub> を両立する必要がある。

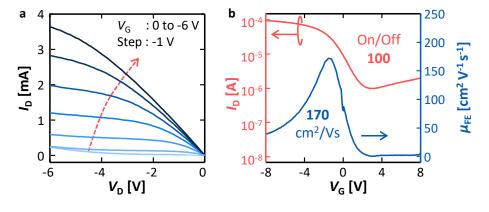

そこで、最大粒径であった  $t_i$  = 100 nm の成長層を化学機械研磨により 55 nm まで薄膜化した。 その結果、完全空乏化に相当する充分に低い  $p(3.0\times10^{17}~{\rm cm}^{-3})$  と高い  $\mu_{\rm Hall}$  (188 cm² V-¹ s-¹) を維持した。本サンプルを同様のプロセスで TFT 化した。図 2.22(a)に示す出力特性より、典型的な p チャネルトランジスタの動作を確認した。更に、高い  $\mu_{\rm Hall}$  による高い  $I_{\rm ON}$  と完全空乏化に起因した低い  $I_{\rm OFF}$  により、優れた  $I_{\rm ON}/I_{\rm OFF}$  (102)、 $\mu_{\rm FE}$  (170 cm² V-¹ s-¹) を実証した(図 2.22(b))。

図 2.21 (a) - (e) IPF 像. (f) 結晶粒径. (g) 膜の電気的特性. (h)ドレイン電流  $I_D$  ならびに  $I_{ON}/I_{OFF}$ . (i)  $\mu_{Hall}$  ならびに  $\mu_{FE}$ .

図 2.22 (a) 出力特性. (b) 伝達特性および µFE.

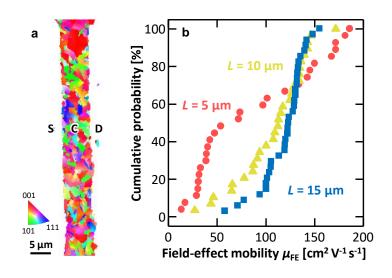

図 2.23(a)に L=10  $\mu$ m のチャネル領域(C)の IPF 像を示す。様々な結晶粒から構成されていることが判る。多結晶材料をチャネルに用いた TFT では、素子毎の特性にばらつきが発生する。これは、キャリア輸送の障害となる結晶粒界の含有割合が異なることに起因する。多結晶デバイスの研究において、このような歩留まりを把握するのは重要である。そこで、同一膜出身のチャネル長(L)を変えた TFT に対し、 $\mu$ <sub>FE</sub> の累積分布を調査した(図 2.23(b))。大きな L 程ばらつきが小さく、多結晶 TFT の先例  $^{99}$  に符合する。また、この結果は Ge-TFT では初めて実測できたものとなる。我々の固相成長 Ge 薄膜が従来よりも結晶粒径が大きく、また充分高いキャリア移動度を有することで実現したものである。

上記の歩留まりを向上し、優れた動作を得るために結晶粒界の制御が望まれる。今回試作した TFT はチャネル領域を微細化(< μm)していないものである。固相成長 Ge 薄膜の結晶粒径は充分に大きく(> μm)、さらに核発生の起点を制御できれば、チャネル領域を単結晶化することが可能になると考えられる。局所的に核生成層を導入したり、金属触媒や応力を加えたりすることで、核発生から粒界までを制御するアプローチが考えられる 76,100,101。

図 2.23 (a) IPF 像ならびに(b) µFE の累積分布.

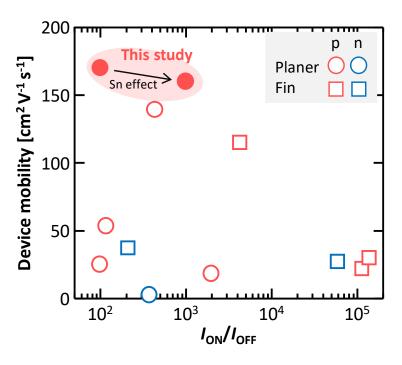

最後に、本研究で得たデバイス特性 ( $\mu_{FE}$ ,  $I_{ON}/I_{OFF}$ ) を他手法で作製した多結晶 TFT と比較する  $^{23,51,53,102-107}$  (図 2.24)。今回試作した Ge-TFT はこれまでで最も高い  $\mu_{FE}$  を有する。これは単結晶 Si-MOSFET に匹敵する値である。さらに、 $I_{ON}/I_{OFF}$  を比較的高い値で両立している。これは、チャネルを微細化しない Ge-TFT として最高レベルのトランジスタ特性である。さらに前節で触れた、Ge への Sn 添加に伴う高品質化  $^{83}$  を利用した。その結果、 $\mu_{FE}$  を維持 (160 cm $^2$  V $^{-1}$  s $^{-1}$ ) しつつ、 $I_{ON}/I_{OFF}$  を一桁向上した。未だシンプルな構造でありながらも、低温プロセスで優れたデバイス特性を実証できた事実は、固相成長 Ge 薄膜のポテンシャルを示す好例と言えよう。

しかし、TFT として  $\mu_{FE}$  は優れた値を得ているが、 $I_{ON}/I_{OFF}$  は多結晶 Si ベースの TFT に遠く及ばない。材料に起因した部分もあるので難しい点もあるが、現状の課題は  $I_{OFF}$ (リーク電流)が大きいことである。また、 $\mu_{FE}$  も Ge 本来の豊かな値を引き出すには及ばない。材料側のアプローチとしては、大粒径化(粒界割合の低減)や低キャリア密度化(空乏層の拡大)、高キャリア移動度化(高い  $I_{ON}$ 、 $\mu_{FE}$ )が望まれる。

図 2.24 多結晶 Ge 系 TFT 特性比較.

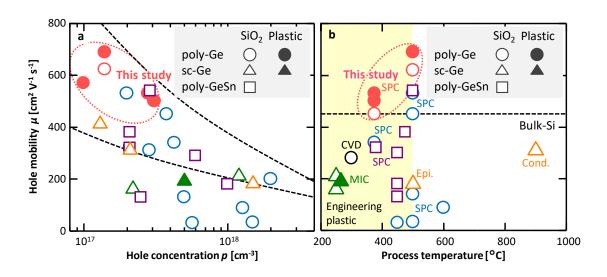

### 2.5 研究目的

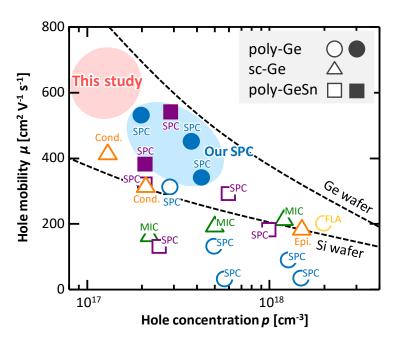

我々は、固相成長法にアイデアを積み重ねて多結晶 Ge 薄膜のキャリア移動度を刷新してきた。 今までの道程を俯瞰するため、絶縁体上に直接合成した Ge 系薄膜における電気的特性のベン チマークを掲載する 4.28,34,36-39,42-44,51,52,77,80-83,108-111 (図 2.25)。当研究室で得られた合成膜は、低 温(≤ 500 °C)直接合成膜としては最高の値を有する。しかし、Ge の優れた物性ポテンシャルを活 かし、民生応用を目指すのであれば、更なる高キャリア移動度化が望ましい。

本論文では、固相成長法により合成した多結晶 Ge 薄膜に対しキャリア移動度の向上を多角的に検討する。そして、高機能性と汎用性を両立した次世代デバイスを創出する技術の端緒を開くことを目的とする。第 3 章では、Ge の固相成長における各熱処理過程が物性に与える影響を包括的に議論する。続く第 4 章では、固相成長 Ge 薄膜の更なる高キャリア移動度化を検討し、下部層挿入を検討する。そして第 5 章では、歪導入機構と物性への影響を紐解く。最後の第 6 章では、これまで為し得なかったフレキシブル基板上への高移動度 Ge 多結晶薄膜を実証する。

図 2.25 絶縁体上 Ge 系薄膜の電気的特性比較.

### 2.6 参考文献

- <sup>1</sup> Y. Taur and T-H. Ning, *最新VLSIの基礎* (丸善出版, 2002).

- <sup>2</sup> R.H. Dennard, F.H. Gaensslen, H.-N. Yu, V.L. Rideout, E. Bassous, and A.R. LeBlanc, IEEE J. Solid-State Circuits **9**, 256 (1974).

- <sup>3</sup> A. Toriumi and T. Nishimura, Japanese Journal of Applied Physics **57**, 010101 (2017).

- <sup>4</sup> S.M. Sze and J.C. Irvin, Solid State Electron. 11, 599 (1968).

- <sup>5</sup> C.H. Lee, T. Nishimura, T. Tabata, S.K. Wang, K. Nagashio, K. Kita, and A. Toriumi, in *2010 International Electron Devices Meeting* (2010), pp. 18.1.1-18.1.4.

- <sup>6</sup> C. Hyun Lee, T. Nishimura, T. Tabata, D. Zhao, K. Nagashio, and A. Toriumi, Appl. Phys. Lett. **102**, 232107 (2013).

- <sup>7</sup> D.E. Aspnes and A.A. Studna, Phys. Rev. B Condens. Matter **27**, 985 (1983).

- <sup>8</sup> J. Kang, M. Takenaka, and S. Takagi, Opt. Express **24**, 11855 (2016).

- 9 敏則太子 and 一郎米永, まてりあ **50**,431 (2011).

- <sup>10</sup> C.J. Tracy, P. Fejes, N. David Theodore, P. Maniar, E. Johnson, A.J. Lamm, A.M. Paler, I.J. Malik, and P. Ong, Journal of Electronic Materials **33**, 886 (2004).

- <sup>11</sup> G. Taraschi, A.J. Pitera, and E.A. Fitzgerald, Solid State Electron. **48**, 1297 (2004).

- <sup>12</sup> K. Yu, F. Yang, H. Cong, L. Zhou, Q. Liu, L. Zhang, B. Cheng, C. Xue, Y. Zuo, and C. Li, J. Alloys Compd. **750**, 182 (2018).

- <sup>13</sup> Y. Moriyama, K. Ikeda, Y. Kamimuta, M. Oda, T. Irisawa, Y. Nakamura, A. Sakai, and T. Tezuka, Solid State Electron. **83**, 42 (2013).

- <sup>14</sup> M. Bruel, Electron. Lett. **31**, 1201 (1995).

- <sup>15</sup> F. Letertre, C. Deguet, C. Richtarch, B. Faure, J.M. Hartmann, F. Chieu, A. Beaumont, J. Dechamp,

- C. Morales, F. Allibert, P. Perreau, S. Pocas, S. Personnic, C. Lagahe-Blanchard, B. Ghyselen, Y.M. Le Vaillant, Jalaguier, N. Kernevez, and C. Mazure, MRS Online Proceedings Library (OPL) **809**, B4.4 (2004).

- <sup>16</sup> K. Izumi, M. Doken, and H. Ariyoshi, Electron. Lett. **14**, 593 (1978).

- <sup>17</sup> S. Fukatsu, Y. Ishikawa, T. Saito, and N. Shibata, Appl. Phys. Lett. **72**, 3485 (1998).

- <sup>18</sup> L. Rebohle, S. Prucnal, and W. Skorupa, Semicond. Sci. Technol. **31**, 103001 (2016).

- <sup>19</sup> W. Yeh, H. Chen, H. Huang, C. Hsiao, and J. Jeng, Appl. Phys. Lett. **93**, 094103 (2008).

- <sup>20</sup> M. Kurosawa, N. Taoka, H. Ikenoue, O. Nakatsuka, and S. Zaima, Appl. Phys. Lett. **104**, 061901 (2014).

- <sup>21</sup> H.A. Kasirajan, W.-H. Huang, M.-H. Kao, H.-H. Wang, J.-M. Shieh, F.-M. Pan, and C.-H. Shen, Appl. Phys. Express **11**, 101305 (2018).

- <sup>22</sup> R. Matsumura and N. Fukata, Mater. Lett. **288**, 129328 (2021).

- <sup>23</sup> L. Zhang, H. Hong, C. Yu, C. Li, S. Chen, W. Huang, J. Wang, and H. Wang, Phys. Stat. Solidi. Rapid Res. Lett. **13**, 1900420 (2019).

- <sup>24</sup> C.-Y. Liao, C.-Y. Huang, M.-H. Huang, W.-H. Huang, C.-H. Shen, J.-M. Shieh, and H.-C. Cheng, Jpn. J. Appl. Phys. **56**, 06GF08 (2017).

- <sup>25</sup> A. Satta, A. D'Amore, E. Simoen, W. Anwand, W. Skorupa, T. Clarysse, B. Van Daele, and T. Janssens, Nucl. Instrum. Methods Phys. Res. B **257**, 157 (2007).

- <sup>26</sup> W.-B. Jin, Y. Park, B.-K. Kim, H.J. Kim, J.-H. Hwang, H. Chung, J.H. Park, D.H. Kim, and S. Park, Int. J. Therm. Sci. **83**, 25 (2014).

- <sup>27</sup> H. Oka, W. Mizubayashi, Y. Ishikawa, N. Uchida, T. Mori, and K. Endo, Appl. Phys. Express **14**, 025505 (2021).

- <sup>28</sup> K. Usuda, Y. Kamata, Y. Kamimuta, T. Mori, M. Koike, and T. Tezuka, Appl. Phys. Express 7, 056501 (2014).

- <sup>29</sup> Y. Kamata, M. Koike, E. Kurosawa, M. Kurosawa, H. Ota, O. Nakatsuka, S. Zaima, and T. Tezuka, Appl. Phys. Express **7**, 121302 (2014).

- <sup>30</sup> T. Matsui, M. Kondo, K. Ogata, T. Ozawa, and M. Isomura, Appl. Phys. Lett. **89**, 142115 (2006).

- <sup>31</sup> M. Tada, J.-H. Park, J.R. Jain, and K.C. Saraswat, J. Electrochem. Soc. 156, D23 (2008).

- <sup>32</sup> A. Dey and D. Das, J. Phys. Chem. Solids **154**, 110055 (2021).

- <sup>33</sup> Z. Meng, Z. Jin, B.A. Gururaj, P.C.H. Kwok, M.W.Z. Meng, Z. Jin, B.A. Gururaj, P. Chu, c. H.S. Kwok, and M. Wong, J. Electrochem. Soc. **144**, 1423 (1997).

- <sup>34</sup> Z. Meng, Z. Jin, G.A. Bhat, P. Chu, H.S. Kwok, and M. Wong, J. Mater. Res. **12**, 2548 (1997).

- <sup>35</sup> O. Madelung, *Semiconductors: Data Handbook* (Springer, Berlin, Heidelberg, 2004).

- <sup>36</sup> K. Toko, I. Nakao, T. Sadoh, T. Noguchi, and M. Miyao, Solid State Electron. **53**, 1159 (2009).

- <sup>37</sup> C.-Y. Tsao, J. Huang, X. Hao, P. Campbell, and M.A. Green, Sol. Energy Mater. Sol. Cells **95**, 981 (2011).

- <sup>38</sup> H.-W. Jung, W.-S. Jung, H.-Y. Yu, and J.-H. Park, J. Alloys Compd. **561**, 231 (2013).

- <sup>39</sup> W. Takeuchi, N. Taoka, M. Kurosawa, M. Sakashita, O. Nakatsuka, and S. Zaima, Appl. Phys. Lett. **107**, 022103 (2015).

- <sup>40</sup> S. Zaima, O. Nakatsuka, N. Taoka, M. Kurosawa, W. Takeuchi, and M. Sakashita, Sci. Technol. Adv. Mater. 16, 043502 (2015).

- <sup>41</sup> H. Höhler, N. Atodiresei, K. Schroeder, R. Zeller, and P.H. Dederichs, Phys. Rev. B **71**, (2005).

- <sup>42</sup> T. Sadoh, Y. Kai, R. Matsumura, K. Moto, and M. Miyao, Appl. Phys. Lett. **109**, 232106 (2016).

- <sup>43</sup> C. Xu, X. Gong, M. Miyao, and T. Sadoh, Appl. Phys. Lett. **115**, 042101 (2019).

- <sup>44</sup> I. Yoshikawa, M. Kurosawa, W. Takeuchi, M. Sakashita, O. Nakatsuka, and S. Zaima, Mater. Sci. Semicond. Process. **70**, 151 (2017).

- <sup>45</sup> W. Knaepen, S. Gaudet, C. Detavernier, R.L. Van Meirhaeghe, J.J. Sweet, and C. Lavoie, J. Appl. Phys. **105**, 083532 (2009).

- <sup>46</sup> K. Toko, N. Oya, N. Saitoh, N. Yoshizawa, and T. Suemasu, Appl. Phys. Lett. **106**, 082109 (2015).

- <sup>47</sup> A.G. Fischer, D.J. Tizabi, and H. Blanke, IEEE Electron Device Lett. **4**, 447 (1983).

- <sup>48</sup> H. Utsumi, N. Nishiguchi, R. Miyazaki, H. Suzuki, K. Kitahara, and A. Hara, Jpn. J. Appl. Phys. **58**, 046501 (2019).

- <sup>49</sup> B. Hekmatshoar, S. Mohajerzadeh, D. Shahrjerdi, and M.D. Robertson, Appl. Phys. Lett. **85**, 1054 (2004).

- <sup>50</sup> D. Shahrjerdi, B. Hekmatshoar, S.S. Mohajerzadeh, A. Khakifirooz, and M. Robertson, J. Electron. Mater. **33**, 353 (2004).

- <sup>51</sup> K. Kasahara, Y. Nagatomi, K. Yamamoto, H. Higashi, M. Nakano, S. Yamada, D. Wang, H. Nakashima, and K. Hamaya, Appl. Phys. Lett. **107**, 142102 (2015).

- <sup>52</sup> H. Higashi, M. Nakano, K. Kudo, Y. Fujita, S. Yamada, T. Kanashima, I. Tsunoda, H. Nakashima, and K. Hamaya, Appl. Phys. Lett. **111**, 222105 (2017).

- <sup>53</sup> T. Suzuki, B.M. Joseph, M. Fukai, M. Kamiko, and K. Kyuno, Appl. Phys. Express **10**, 095502 (2017).

- <sup>54</sup> K. Kusano, A. Yamamoto, M. Nakata, T. Suemasu, and K. Toko, ACS Appl. Energy Mater. **1**, 5280 (2018).

- <sup>55</sup> T. Ozawa, K. Kusano, M. Murata, A. Yamamoto, T. Suemasu, and K. Toko, J. Appl. Phys. **129**, 015303 (2021).

- <sup>56</sup> M. Tsuji, T. Imajo, N. Saitoh, N. Yoshizawa, T. Suemasu, and K. Toko, J. Phys. D Appl. Phys. **53**, 075105 (2020).

- <sup>57</sup> K. Kusano, M. Tsuji, T. Suemasu, and K. Toko, Appl. Phys. Express **12**, 055501 (2019).

- <sup>58</sup> M. Tsuji, K. Kusano, T. Suemasu, and K. Toko, Appl. Phys. Lett. **116**, 182105 (2020).

- <sup>59</sup> K. Toko and T. Suemasu, J. Phys. D Appl. Phys. **53**, 373002 (2020).

- <sup>60</sup> K. Toko, M. Kurosawa, N. Saitoh, N. Yoshizawa, N. Usami, M. Miyao, and T. Suemasu, Appl.

- Phys. Lett. 101, 072106 (2012).

- <sup>61</sup> R. Yoshimine, K. Toko, N. Saitoh, N. Yoshizawa, and T. Suemasu, J. Appl. Phys. **122**, 215305 (2017).

- <sup>62</sup> J.-H. Park, T. Suzuki, M. Kurosawa, M. Miyao, and T. Sadoh, Appl. Phys. Lett. **103**, 082102 (2013).

- <sup>63</sup> H. Gao and T. Sadoh, Appl. Phys. Lett. **117**, 172102 (2020).

- <sup>64</sup> T. Nishida, M. Nakata, T. Suemasu, and K. Toko, Thin Solid Films **681**, 98 (2019).

- <sup>65</sup> T. Nishida, K. Moto, N. Saitoh, N. Yoshizawa, T. Suemasu, and K. Toko, Appl. Phys. Lett. **114**, 142103 (2019).

- <sup>66</sup> T. Nishida, T. Suemasu, and K. Toko, AIP Adv. **10**, 015153 (2020).

- <sup>67</sup> T. Nishida, K. Igura, T. Imajo, T. Suemasu, and K. Toko, Sci. Rep. **11**, 10159 (2021).

- <sup>68</sup> M. Tsuji, M. Murata, A. Yamamoto, T. Suemasu, and K. Toko, Appl. Phys. Lett. **117**, 162103 (2020).

- 69 美紀江辻.. 筑波大学院 修士論文, (2020).

- <sup>70</sup> T. Ozawa, M. Murata, T. Suemasu, and K. Toko, Materials **15**, 608 (2022).

- <sup>71</sup> C. Hayzelden and J.L. Batstone, J. Appl. Phys. **73**, 8279 (1993).

- <sup>72</sup> N. Vouroutzis, J. Stoemenos, N. Frangis, G.Z. Radnóczi, D. Knez, F. Hofer, and B. Pécz, Sci. Rep. 9, 2844 (2019).

- <sup>73</sup> M. Kurosawa, N. Taoka, M. Sakashita, O. Nakatsuka, M. Miyao, and S. Zaima, Appl. Phys. Lett. 103, 101904 (2013).

- <sup>74</sup> T. Sadoh, M. Kurosawa, T. Hagihara, K. Toko, and M. Miyao, Electrochem. Solid-State Lett. **14**, H274 (2011).

- <sup>75</sup> T. Nishijima, S. Shimizu, K. Kusano, K. Kudo, M. Furuta, Y. Kusuda, S. Motoyama, N. Naka, T. Numata, K. Takakura, and I. Tsunoda, AIP Adv. 10, 055306 (2020).

- <sup>76</sup> T. Ishiyama, T. Imajo, N. Saitoh, N. Yoshizawa, T. Suemasu, and K. Toko, Cryst. Growth Des. **22**, 1123 (2022).

- <sup>77</sup> K. Toko, R. Yoshimine, K. Moto, and T. Suemasu, Sci. Rep. **7**, 16981 (2017).

- <sup>78</sup> H. Haesslein, R. Sielemann, and C. Zistl, Phys. Rev. Lett. **80**, 2626 (1998).

- <sup>79</sup> H. Yang, D. Wang, and H. Nakashima, Appl. Phys. Lett. **95**, 122103 (2009).

- <sup>80</sup> R. Yoshimine, K. Moto, T. Suemasu, and K. Toko, Appl. Phys. Express 11, 031302 (2018).

- <sup>81</sup> T. Mizoguchi, T. Imajo, T. Suemasu, and K. Toko, Appl. Phys. Express 13, 101005 (2020).

- 82 K. Moto, N. Saitoh, N. Yoshizawa, T. Suemasu, and K. Toko, Appl. Phys. Lett. 114, 112110 (2019).

- 83 K. Moto, R. Yoshimine, T. Suemasu, and K. Toko, Sci. Rep. 8, 14832 (2018).

- <sup>84</sup> Y.-M. Ha, S.-H. Lee, C.-H. Han, and C.-K. Kim, Journal of Electronic Materials 23, 39 (1994).

- <sup>85</sup> S. Gupta, B. Magyari-Köpe, Y. Nishi, and K.C. Saraswat, J. Appl. Phys. **113**, 073707 (2013).

- <sup>86</sup> J.D. Sau and M.L. Cohen, Phys. Rev. B Condens. Matter **75**, 045208 (2007).

- <sup>87</sup> H. Lin, R. Chen, Y. Huo, T.I. Kamins, and J.S. Harris, Appl. Phys. Lett. **98**, 261917 (2011).

- <sup>88</sup> H. Li, J. Brouillet, A. Salas, X. Wang, and J. Liu, Opt. Mater. Express, OME 3, 1385 (2013).

- <sup>89</sup> K. Moto, K. Yamamoto, T. Imajo, T. Suemasu, H. Nakashima, and K. Toko, Appl. Phys. Lett. **114**, 212107 (2019).

- <sup>90</sup> T. Imajo, K. Moto, K. Yamamoto, T. Suemasu, H. Nakashima, and K. Toko, ECS Trans. **98**, 423 (2020).

- <sup>91</sup> K. Moto, K. Yamamoto, T. Imajo, T. Suemasu, H. Nakashima, and K. Toko, IEEE Electron Device Lett. **42**, 1735 (2021).

- <sup>92</sup> F.A. Trumbore, The Bell System Technical Journal **39**, 205 (1960).

- <sup>93</sup> E.N. Sgourou, Y. Panayiotatos, R.V. Vovk, N. Kuganathan, and A. Chroneos, NATO Adv. Sci. Inst. Ser. E Appl. Sci. **9**, 2454 (2019).

- <sup>94</sup> H. Bracht and S. Brotzmann, Mater. Sci. Semicond. Process. **4–5**, 471 (2006).

- 95 T. Nishimura, K. Kita, and A. Toriumi, Appl. Phys. Lett. **91**, 123123 (2007).

- 96 K. Yamamoto, R. Noguchi, M. Mitsuhara, M. Nishida, T. Hara, D. Wang, and H. Nakashima, J.

- Appl. Phys. 118, 115701 (2015).

- <sup>97</sup> A. Dimoulas, A. Toriumi, and S.E. Mohney, MRS Bull. **34**, 522 (2009).

- 98 K. Yamamoto, T. Sada, D. Wang, and H. Nakashima, Appl. Phys. Lett. 103, 122106 (2013).

- <sup>99</sup> A.W. Wang and K.C. Saraswat, IEEE Trans. Electron Devices **47**, 1035 (2000).

- <sup>100</sup> K. Toko, H. Kanno, A. Kenjo, T. Sadoh, T. Asano, and M. Miyao, Appl. Phys. Lett. **91**, 042111 (2007).

- <sup>101</sup> K. Toko, T. Sadoh, and M. Miyao, Appl. Phys. Lett. **94**, 192106 (2009).

- <sup>102</sup> T. Sadoh, H. Kamizuru, A. Kenjo, and M. Miyao, Appl. Phys. Lett. **89**, 192114 (2006).

- <sup>103</sup> Y. Kamata, Y. Kamimuta, K. Ikeda, K. Furuse, M. Ono, M. Oda, Y. Moriyama, K. Usuda, M. Koike, T. Irisawa, E. Kurosawa, and T. Tezuka, in *2013 Symposium on VLSI Technology* (2013), pp. T94–T95.

- <sup>104</sup> A. Hara, Y. Nishimura, and H. Ohsawa, Jpn. J. Appl. Phys. **56**, 03BB01 (2016).

- <sup>105</sup> W.-H. Huang, J.-M. Shieh, M.-H. Kao, C.-H. Shen, T.-E. Huang, H.-H. Wang, C.-C. Yang, T.-Y. Hsieh, J.-L. Hsieh, P. Yu, and W.-K. Yeh, Appl. Phys. Express 10, 026502 (2017).

- <sup>106</sup> K. Usuda, Y. Kamiata, Y. Kamimuta, T. Mori, M. Koike, and T. Tezuka, in *2014 IEEE International Electron Devices Meeting* (2014), pp. 16.6.1-16.6.4.

- <sup>107</sup> M. Kurosawa, Y. Kamata, H. Ikenoue, N. Taoka, O. Nakatsuka, T. Tezuka, and S. Zaima, in *Extended Abstracts of the 2014 International Conference on Solid State Devices and Materials* (The Japan Society of Applied Physics, 2014), p. F-2-5L.

- <sup>108</sup> T. Maeda, K. Ikeda, S. Nakaharai, T. Tezuka, N. Sugiyama, Y. Moriyama, and S. Takagi, Thin Solid Films **508**, 346 (2006).

- <sup>109</sup> J.-H. Park, K. Kasahara, K. Hamaya, M. Miyao, and T. Sadoh, Appl. Phys. Lett. **104**, 252110 (2014).

- <sup>110</sup> O. Nakatsuka, N. Tsutsui, Y. Shimura, S. Takeuchi, A. Sakai, and S. Zaima, Jpn. J. Appl. Phys. 49,

04DA10 (2010).

<sup>111</sup> N. Hirashita, Y. Moriyama, S. Nakaharai, T. Irisawa, N. Sugiyama, and S.I. Takagi, Appl. Phys. Express 1, 1014011 (2008).

# 第3章

# 固相成長 Ge 薄膜に加熱堆積が与える物性変調効果

### 3.1 緒言

次世代デバイスの実現を目指し、絶縁体上 Ge 薄膜の低温合成が盛んに行われている。一方、数十年にわたり、Ge 本来の好適なキャリア輸送特性を引き出すには至っていなかった。我々は固相成長法を工夫することで Ge 薄膜のキャリア移動度を刷新してきた <sup>1,2</sup>。本技術の基本は、①堆積中、②固相成長中、③成長後の熱処理(ポストアニール:PA)の 3 段階の加熱プロセスであり、単結晶 Si 基板と同等のキャリア移動度 450 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> に結実している。

しかし、その物性に関しては結晶粒径と電気的特性(正孔移動度 $\mu$ 、正孔密度p)の観点から現象論的に考察したに留まる。材料研究においては、物性に影響する機構を明らかにして、好適なものは育て、不要なものは取り除くのが品質向上への王道となる $^3$ 。本節ではより深く固相成長 $^4$  Ge 薄膜の物性を解析することにより、各熱処理過程が多結晶 $^4$  Ge 薄膜に与える影響について詳細に議論した。

3.2 節では、実験手法を説明する。その後、各熱処理過程が固相成長 Ge 薄膜の結晶性(3.3 節)、光学的特性(3.4 節)、そして電気的特性(3.5 節)に与える影響を論じる。3.6 節では、本章の結果をまとめる。

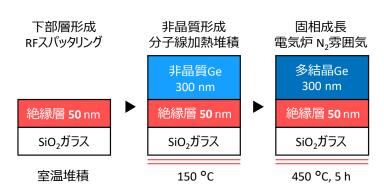

## 3.2 実験手法

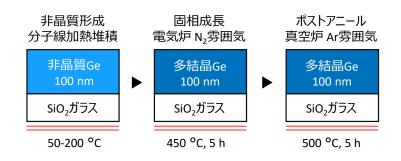

試料作製手順を図 3.1 に示す。先ず、 $SiO_2$  ガラス基板をアセトン、メタノール、純水で 2 min 超音波洗浄した。その後、1.5%HFaqに 1 min 浸漬し、純水でリンス後、乾燥  $N_2$ により水分除去した。その後、基板上へ Ge 100 nm を分子線加熱堆積 ( $T_d$ :50-200 °C)した。堆積レートは 1 nm min<sup>-1</sup> とし、Ge の純度は 99.999%である。その後、 $N_2$  雰囲気中で熱処理 (450 °C, 5 h)を行うことで固相成長を誘起した。結晶化後、Ar 雰囲気中で PA (500 °C, 5 h)を行った。

試料の結晶性は走査型電子顕微鏡 (JEOL JSM-7001F、電圧 25 kV、電流 15 mA) へアタッチメントされた電子後方散乱回折 (EBSD) 法 (TSL) と、Raman 分光法 (JASCO NRS-5100、波長 532 nm、出力 5 mW、スポットサイズ 20  $\mu$ m、露光 30 sec×2) により評価した。結晶粒径は、方位差  $\theta$ <5°の領域を単一粒と判別した。この際、双晶粒界 ( $\Sigma$ 3,9) は電気的に不活性であるため  $^{4.5}$ 、本処理からは除外した。単一粒と見なされた領域を等面積の円に換算し、面積加重平均で結晶粒径を算出した。Raman スペクトルは Origin6.0 の Pseudo Voight 関数でフィッティングした。光学的特性は顕微フォトルミネッセンス ( $\mu$ -PL) 法 (Princeton Instruments PyLon-IR-2.2、波長 647 nm、出力 20 mW、スポットサイズ: 1  $\mu$ m) にて評価した。電気的特性は Bio-Rad HL5500PC system を用いて van der Pauw 法により評価した。

図 3.1 試料作製手順.

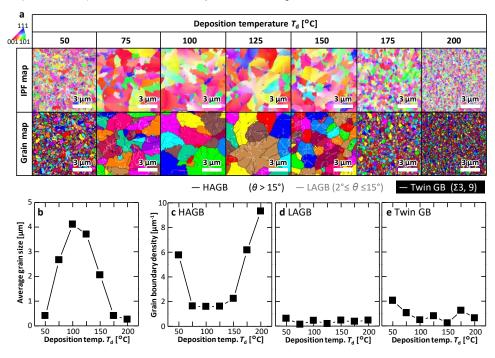

## 3.3 結晶性に与える影響

EBSD 法により Ge 成長層の結晶粒評価を行った。逆極点方位 (IPF) 像ならびに Grain 像により、堆積温度  $T_d$  に依って結晶粒径が大きく変化することが判る (図 3.2(a))。これは、2 章で記したように前駆体密度に応じて、固相成長過程における横方向成長速度が変化するためである  $^1$ 。図 3.2(b)に平均粒径を示す。加熱堆積に伴う非晶質の高密度化と堆積時結晶核発生のバランスにより、 $T_d$ =100 °C で結晶粒径はピークとなった  $^1$ 。高角粒界 (HAGB: High Angle Grain Boundary)を方位差  $\theta$  が 15°以上、低角粒界 (LAGB: Low Angle Grain Boundary)を 2 ° $\leq$   $\theta$   $\leq$  15°、双晶粒界を  $\Sigma$  3,9 と定義して密度を調査した  $^6$ 。HAGB 密度は、結晶粒径が大きい Ge 成長層において減少した (図 3.2(c))。また、あらゆる粒界種の中で支配的だった。LAGB 密度は、HAGB 密度に比べて少なく、さらに  $T_d$  に対する明確な依存性はなかった (図 3.2(d))。双晶粒界密度は低  $T_d$  ほど増加する傾向を見せた (図 3.2(e))。これは、低密度な非晶質 Ge の粒成長が遅く、生成エネルギーの低い双晶が発生しやすいためであると考えられる  $^{7.8}$ 。

図 3.2 EBSD 解析. (a) IPF 像. (b) 結晶粒径. (c) HAGB, (d) LAGB ならびに(e) 双晶粒界密度.

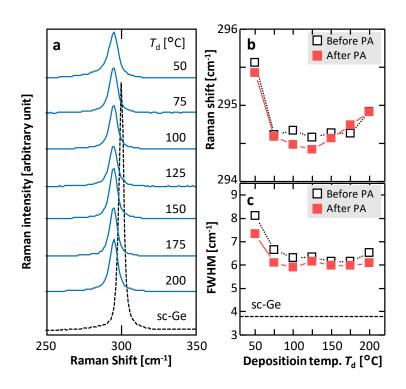

続いて、図.3.3(a)に熱処理後の Raman スペクトルを示す。全  $T_d$ に対して結晶相に由来する Ge-Ge peak が得られた。また、単結晶 Ge 基板の peak 位置 (300 cm<sup>-1</sup>) より低波数側にシフトしていた。 伸長歪が導入されていることが判る。 PA 前後の Ge-Ge peak 位置を  $T_d$  の関数とした。 Peak 位置は  $T_d$  によって異なり、結晶粒径 (図 3.2(b)) との比較から、以下のように考えられる。 基本的には小粒径ほどシフト量が少なく、歪が小さい。 これは、大粒径のサンプルでは応力が蓄積される、あるいは粒界での応力緩和がある。 また PA によって、大粒径ほど歪が蓄積 (Ge からのシフトが拡大) され、小粒径ほど緩和した。 図 3.3(c)に PA 前後の Ge-Ge peak の FWHM を  $T_d$  に対して整理した。 小粒径な  $T_d$  = 200 °C でも FWHM は小さく、主に粒内の結晶性を反映していると示唆される。  $T_d$  = 50 °C は非晶質成分が混じるため顕著に悪い。 すなわち、前駆体加熱堆積により得られる固相成長 Ge 薄膜は、結晶粒自体の品質も向上したと推察される。 PA で全  $T_d$  に対し FWHM は減少した。 これにより結晶性が高まったと言える。

図 3.3 Raman 分光法解析. (a) Raman スペクトル. (b) Raman shift. (c) FWHM.

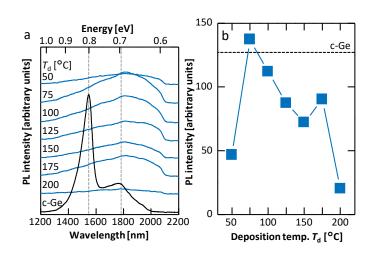

## 3.4 光学的特性に与える影響

図 3.4(a)に室温、大気下における Ge 成長層の PL スペクトルを示す。 Ge の吸収係数が 647 nm において約  $10^5$  cm- $^1$  であり  $^9$ 、本サンプル膜厚 (100 nm) では 63%を吸収すると見積もれる。充分 膜厚が薄いため、膜全体を測定していると考えられる。先ず Ge 成長層からは、0.69 eV 付近に間接遷移に起因する PL 発光が見られた  $^{10}$ 。一方、直接遷移起因の発光  $(\sim 0.8$  eV) は見られなかった。光励起キャリアの L 点における伝導帯底への遷移、あるいは粒界や他欠陥準位での非発光性再結合によると推察される。また、大粒径な Ge 成長層では発光強度の顕著な増加がみられた。さらに、ピーク位置は単結晶 Ge 基板より 50 meV 程度レッドシフトしていた。これは、(1)0.5%程度の圧縮歪の導入により伝導帯下端が下がった (1)1、あるいは②間接遷移以外に由来した (2)2、Peak の足し合わせによる見かけ上のシフトだと考えられる。図 (2)3、(3)4(b)に (2)4 に対し整理した結果を示す。強度の振る舞いは (2)4 に対して (2)5 がまると表えられる。また、一部のサンプルでは単結晶 (2)6 の強度を超えたが、これは上記①による発光効率の増加、あるいは、バンドギャップに近い発光性のサブバンド遷移の足し合わせに起因すると思われる。

図 3.4 光学的特性. (a) PL スペクトル. (b) PL 強度の Ta 依存性.

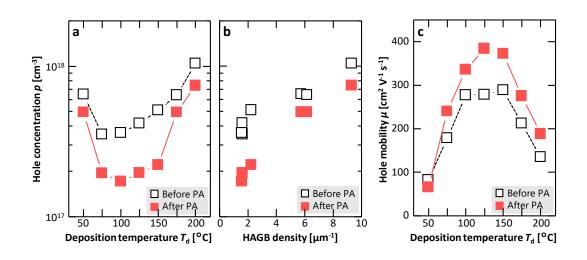

### 3.5 電気的特性に与える影響

図 3.5(a)に PA 前後の Ge 成長層の正孔密度 p を  $T_d$  に対し整理した。従来のあらゆる Ge 薄膜 と同様に p 型伝導となった。これは、結晶 Ge 中の欠陥が価電子帯頂上付近に浅い準位を形成し、正孔を放出する為と考えられている。また、p は  $T_d$  に依存して変化した。図 3.2(c)の結果と対比すると、PA 前の p は HAGB 密度と強い相関を持つ(図 3.5(b))。すなわち、HAGB もアクセプタ生成源であることが示唆される。PA 後、p は全  $T_d$  に対し減少した。欠陥誘起アクセプタの補償効果に起因すると考えらえる。また、PA では結晶粒径が大きい(75 °C  $\leq T_d \leq 150$  °C)ほど p が顕著に下がる傾向があった。すなわち、結晶粒内も正孔を放出することが考えられる。

図 3.5(c)に PA 前後の Ge 成長層の正孔移動度  $\mu$  を  $T_d$  に対し整理した。 $\mu$  も p と同様  $T_d$  に依存して変化した。また、一般的な多結晶半導体薄膜と同様に、結晶粒径が大きいほど高い値と成った。 $\mu$  は PA によって概ね全ての  $T_d$  に対し増加した。

図 3.5 電気的特性. 正孔密度 p の(a)  $T_d$  ならびに(b) HAGB 密度依存性. (c) 正孔移動度  $\mu$ .

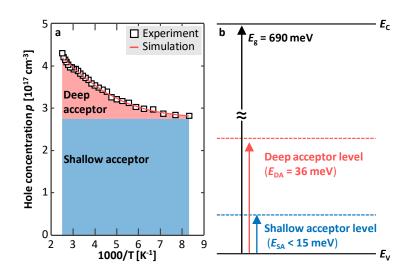

#### 3.5.1 キャリア起源の検討

p の温度依存性 (115—400 K) を測定し、多数キャリアである正孔の起源を検討した。図 5.6(a)は PA 前の Ge 成長層 ( $T_d$ =125 °C)の p を示す。アクセプタの不活性化を反映し、測定温度が下がるほど p が減少した。一般的には、p の飽和値から欠陥密度を、傾きの線形近似から欠陥準位を求める。しかし、固相成長 Ge 薄膜では Arrhenius plots をしたが、直線領域や飽和領域が現れなかった。従って、固相成長 Ge 内部には、正孔の起源が 2 準位以上あることが判る。しかし、二準位以上の近いエネルギー準位が半導体中にある場合はこの手法が適用できない。そこで、複数ある準位の推定には、Hoffmann<sup>12</sup> や Matsuura<sup>13</sup> らが解析法を提案している。しかし、本研究で得た固相成長 Ge 薄膜は p の温度変動幅が小さく、これらの手法を適用してもピークが判別しづらい。これによりフィッティング解を一義に導出するのは困難であった。そこで我々は、機械学習の知見を取り入れ、線形回帰をベースとしたシンプル且つ高速なシミュレーション方法を提案する。

完全にイオン化した $\mathbf{n}$ 個のアクセプタ準位による $\mathbf{p}$ は次のように表せる。ただし、アクセプタ準位の縮退因子 $\mathbf{g}_i$ は $\mathbf{1}$ とし、電子密度は正孔密度に比べて十分に小さく無視できるものとした。

$$p(T) = \sum_{j=1}^{n} N_j f(E_F - E_j, T)$$

(3.1)

$$f(E_{\rm F} - E, T) = \frac{1}{1 + g_j \exp\left(-\frac{E_{\rm F} - E}{k_{\rm B}T}\right)}$$

(3.2)

ここで、 $N_j$ , $E_j$  はそれぞれ j 番目の完全にイオン化したアクセプタ準位の密度、エネルギー準位である。また、 $k_B$ は Boltzmann 定数、T は絶対温度である。

Fermi 準位 $E_F$ は次の積分方程式を Newton 法で解くことにより数値的に求められる。

$$p(T) = \int_{E_V^{\text{bottom}}}^{E_V^{\text{top}}} 4\pi \left(\frac{2m}{h^2}\right)^{\frac{3}{2}} \sqrt{E_V^{\text{top}} - E} \left[1 - f(E_F - E, T)\right] dE$$

(3.3)

ここで、mは Ge の正孔の有効質量、hは Planck 定数、 $E_V^{\text{top}}$ は価電子帯の上端、 $E_V^{\text{bottom}}$ は価電子帯の下端である。測定温度点を  $T=T_1,\ T_2,\ \cdots,\ T_j$ とし、p を T の関数表現に変換して  $Y=(p(T_1),p(T_2)\ \cdots\ p(T_i))$  と表すと、(3.1)式は次の式と等価となる。

$$Y = W^t X \tag{3.4}$$

$$\boldsymbol{W} = \begin{pmatrix} N_1 \\ \vdots \\ N_n \end{pmatrix} \tag{3.5}$$

$$\mathbf{X} = \begin{pmatrix} f(E_{F} - E_{1}, T_{1}) & f(E_{F} - E_{1}, T_{2}) & \cdots & f(E_{F} - E_{1}, T_{m}) \\ f(E_{F} - E_{2}, T_{1}) & f(E_{F} - E_{2}, T_{2}) & \cdots & f(E_{F} - E_{2}, T_{m}) \\ \vdots & & \vdots & & \vdots \\ f(E_{F} - E_{n}, T_{1}) & f(E_{F} - E_{n}, T_{2}) & \cdots & f(E_{F} - E_{n}, T_{m}) \end{pmatrix}$$

(3.6)

この式はXを説明変数、Wを係数行列とした線形回帰モデルと捉えることができ、準位の組 $\{E_j\}$ が与えられればWの最適化問題は高速に解ける  $^{14}$ 。そのため、準位の探索範囲とエネルギー間隔を設けて総当たり探索をすれば、 $N_j$ と  $E_j$ を数秒の実行時間で求められる。つまり、我々は(3.1)式を次の最適化問題として解いた。

$$\underset{E_1, \dots, E_n}{\operatorname{argmin}} \left\{ \min_{N_1, \dots, N_n} \frac{1}{2} \sum_{i=1}^m [p(T_i) - N_j f(E_F - E_j, T_i)]^2 \right\}$$

(3.7)

複数準位を仮定した上で図 3.6(a)に示す結果に適応した結果、2 つのアクセプタ準位を含むシミュレーションカーブ (1 meV 間隔で探索)と最もよく一致した。これら 2 種のアクセプタを、相対的に深い準位 (DA)と浅い準位 (SA)と呼ぶ。ここで、DA の準位 ( $E_{DA}$ )は温度に伴い大きく変化した一方、SA の準位 ( $E_{SA}$ )は本測定温度範囲において一定となった。 $E_{SA}$  が今回の測定温度下限 (115 K)に相当するエネルギー (15 meV)以下であるため、出払い領域であると考えられる。一方、 $E_{DA}$  は 36 meV と見積もられた。以上、線形回帰シミュレーションを用いることで、多結晶 Ge 薄膜中には少なくとも 2 種類のアクセプタ準位が存在し、室温における正孔の支配的要因となっていることを見出した (図 3.6(b))。

図 3.6 (a)p の温度依存性とシミュレーション結果. (b)アクセプタ準位の概観.

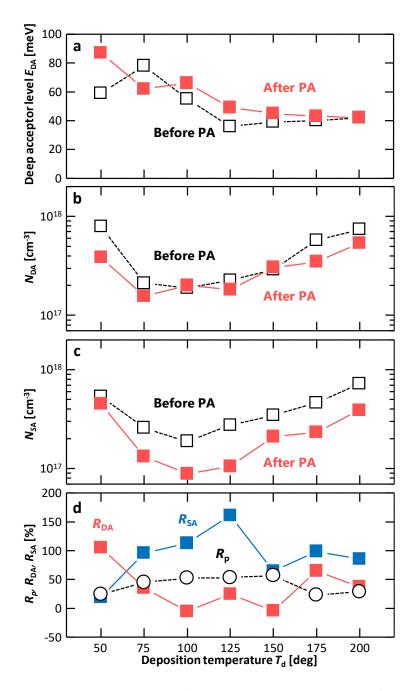

これらの起源を考察するため、欠陥密度の  $T_d$  依存性を解析した。先ず、シミュレーションにより 導出した  $E_{DA}$  は約 40-90 meV の範囲で変化し、 $T_d$  の増加と共に減少した(図 3.7(a))。また、PA は  $E_{DA}$  に大きな変化を及ばさなかった。続いて、シミュレーションにより導出した DA と SA の密度  $(N_{DA}, N_{SA})$  を示す。 $N_{DA}$  と  $N_{SA}$  の双方共に大粒径程(75 °C  $\leq T_d \leq 150$  °C)低くなった。これは p の 挙動に一致した。興味深いことに、PA は  $N_{SA}$  と  $N_{DA}$  に異なる働きをした。すなわち、PA によって  $N_{DA}$  は小粒径ほど低減した一方、 $N_{SA}$  は大粒径ほど低減した。PA 効果の系統的な理解のため、PA に伴う「密度 PA の低減率 PA を以下の通り定義した。

$$R = \frac{D_{before} - D_{after}}{D_{before}} \tag{3.8}$$

ここで $D_{before}$ ,  $D_{after}$ はそれぞれ PA 前後の密度である。式(3.8)に基づき、 $N_{DA}$ ,  $N_{SA}$  および p の PA による減少率 $R_{DA}$ 、 $R_{SA}$ および $R_p$ の  $T_d$ 依存性を図 3.7(d)に整理した。 $R_{DA}$ は小粒径 ( $T_d$ <75 °C, 150 °C <  $T_d$ ) ほど大きい一方、 $R_{SA}$ と $R_p$ は大粒径 (75 °C  $\leq T_d \leq 150$  °C) ほど大きい。したがって、PA による p の低減は、主として SA の低減に起因することが判る。

以上の結果に基づき、我々はアクセプタの起源について現象論的に考察する。第一に、結晶 粒径 (図 3.2(b)) および HAGB 密度 (図 3.2(c)) とp (図 3.5(a)) に相関があり、HAGB がアクセプタ の起源となっていると考えられる。第二に、結晶粒径 (図 3.2(b)) が大きいほど  $R_p$  (図 3.7(d)) も顕著 になる。すなわち結晶粒内にもアクセプタ源が存在し、それらは PA によって強く減少することが判る。Raman 分光法により見出した、結晶性が PA によって向上する事実と整合する (図 3.4(c))。

つまり、結晶粒径が大きいほど  $R_{DA}$  が減少し、 $R_{SA}$  が拡大する。これは、DA が粒界、SA が粒内起因であることを示唆する(図 3.7(d))。このように、我々は Ge 層のアクセプタ欠陥は粒界起因の DA (40-90 meV)と粒内起因の SA (<15 meV)から成ることを見出した。この結果は、理論計算や単結晶バルク Ge に関する既報と概ね整合する。粒界が比較的深いアクセプタ準位(約 60 meV) Ge 25 meV) Ge 25 meV) Ge 26 で形成する。

図 3.7 シミュレーションの定量結果. (a)  $E_{DA}$ . アクセプタ密度 (b)  $N_{DA}$  および (c)  $N_{SA}$ . (d) PA によるアクセプタ密度減少率  $R_p$ ,  $R_{DA}$  および  $R_{SA}$ .

#### 3.5.2 キャリア輸送特性の検討

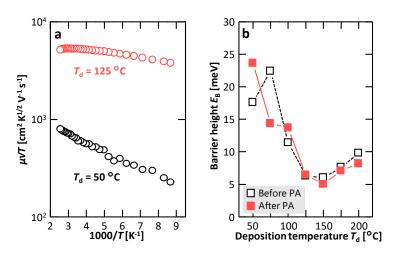

$T_{\rm d}$  の変調や PA によってキャリア移動度が向上することを確認した  $^1$ 。これらの起源を探索した。 粒界散乱が支配的な半導体薄膜における $\mu$ と $E_{\rm B}$ の関係は以下の式(Seto モデル)で表される  $^{17}$ 。

$$\mu = \frac{Lq}{\sqrt{2\pi m k_B T}} \exp\left(-\frac{E_B}{k_B T}\right) \tag{3.9}$$

図 3.8 (a)  $\mu\sqrt{T}$  の Arrhenius plots. (b) 粒界障壁  $E_{\rm B}$ .

### 3.6 結言

我々は固相成長法の高度化により、電気的特性や結晶粒径のブレイクスルーを達成してきた。 本章では、本法の基礎(非晶質前駆体の加熱堆積、結晶化熱処理、PA)に立ち返り、より深い物性探索を行った。

結晶性の観点では、堆積温度  $T_d$  の制御により結晶粒径が広範に変調できることが判った。また、キャリア輸送の障害となる HAGB が大粒径化に伴い減少した。Raman による結晶性評価において、加熱堆積や PA は結晶粒自体の品質も向上することが示唆された。

光学特性の観点では、大粒径  $(75\,^{\circ}\text{C} \leq T_{\text{d}} \leq 125\,^{\circ}\text{C})$ な Ge 成長層において、 $0.69\,^{\circ}\text{eV}$  付近の PL 発光強度が顕著に増加した。これは間接遷移が支配的に可視化されたと考えられる。一方、直接遷移起因の PL 発光は見られなかった。 単結晶 Ge 基板に匹敵する発光強度を得られた事実は、 固相成長 Ge 薄膜の品質が極めて高いことを裏付けるものである。

電気的特性の観点では、大粒径な Ge 成長層において優れた値を示した。更に、PA の施行により正孔移動度  $\mu$  の向上と正孔密度 p の低減を達成した。それぞれの物理的起源を探索するため、温度依存性を評価した。先ず、機械学習の知見を取り入れることで、p の温度依存性からアクセプタ準位と密度を見積もる線形回帰シミュレーションを提案した。これにより、少なくとも 2 種類のアクセプタが存在することを示した。結晶粒径と PA が p に与える影響を系統的に整理した結果、深い準位 (40-90 meV) は粒界起因、浅い準位 (<15 meV) は粒内起因であることが示唆された。続いて、 $\mu$  の温度依存性に対し Seto モデルを適用することで、粒界障壁  $E_B$  を見積もった。PA によって  $E_B$  の大きな変化は認められず、 $\mu$  の向上は不純物散乱の低減が主たる要因であることが判明した。

本研究を通じて得られた知見は、多結晶 Ge 薄膜の動的な物性研究の嚆矢となるものである。

## 3.7 参考文献

- <sup>1</sup> K. Toko, R. Yoshimine, K. Moto, and T. Suemasu, Sci. Rep. 7, 16981 (2017).

- <sup>2</sup> R. Yoshimine, K. Moto, T. Suemasu, and K. Toko, Appl. Phys. Express 11, 031302 (2018).

- 3 河東田 隆, 半導体評価技術 (産業図書, 1989).

- <sup>4</sup> E. Billig and M.S. Ridout, Nature **173**, 496 (1954).

- <sup>5</sup> J. Chen, D. Yang, Z. Xi, and T. Sekiguchi, J. Appl. Phys. **97**, 033701 (2005).

- <sup>6</sup> G. Faraji and Kim, *Severe Plastic Deformation: Methods, Processing and Properties* (Elsevier Science Publishing, Philadelphia, PA, 2018).

- <sup>7</sup> L.F. Mattheiss and J.R. Patel, Phys. Rev. B Condens. Matter **23**, 5384 (1981).

- <sup>8</sup> J. Narayan and A.S. Nandedkar, Philosophical Magazine B: Physics of Condensed Matter; Statistical Mechanics, Electronic, Optical and Magnetic Properties **63**, 1181 (1991).

- <sup>9</sup> D.E. Aspnes and A.A. Studna, Phys. Rev. B Condens. Matter 27, 985 (1983).

- <sup>10</sup> S. Gupta, B. Magyari-Köpe, Y. Nishi, and K.C. Saraswat, J. Appl. Phys. **113**, 073707 (2013).

- <sup>11</sup> J. Michel, J. Liu, and L.C. Kimerling, Nat. Photonics 4, 527 (2010).

- $^{12}$  H.-J. Hoffmann, J. Phys. D Appl. Phys. **19**, 307 (1979).

- <sup>13</sup> Hideharu Matsuura, Yoshitsugu Uchida, Tadashi Hisamatsu and Sumio Matsuda, Jpn. J. Appl. Phys.

37, 6034 (1998).

- <sup>14</sup> C.M. Bishop, *Pattern Recognition and Machine Learning* (Springer New York, 2016).

- <sup>15</sup> R.K. Mueller, J. Appl. Phys. **30**, 2015 (1959).

- <sup>16</sup> O. Madelung, Semiconductors: Data Handbook (Springer, Berlin, Heidelberg, 2004).

- <sup>17</sup> J.Y.W. Seto, J. Appl. Phys. **46**, 5247 (1975).

# 第 4 章

# 下部界面層挿入による Ge 結晶粒径の制御

### 4.1 緒言

絶縁体基板上への高キャリア移動度薄膜の低温合成が期待されている。我々は Ge の固相成長において、前駆体非晶質の密度制御により大粒径化とアクセプタ欠陥低減を達成した  $^1$ 。本技術をシーズとし、厚膜化による界面散乱の低減、ポストアニール (PA) での欠陥補償により、固相成長 Ge 薄膜の正孔移動度を  $450~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$  へと更新した  $^2$ 。しかし、Ge 本来の優れたキャリア輸送特性  $^3$  が得られているとは言い難い。

更なる特性向上のため、キャリア散乱要因を検討した。Matthiessen 則により、半導体中のキャリア輸送の緩和時間は、各散乱要因の逆数和で表現できる。

$$\frac{1}{\tau_{\text{tot}}} = \frac{1}{\tau_{\text{phonon}}} + \frac{1}{\tau_{\text{imp}}} + \frac{1}{\tau_{\text{others}}}$$

(4.1)

ここで $\tau_{tot}$ は合計、 $\tau_{phonon}$ がフォノン、 $\tau_{imp}$ がイオン化不純物、 $\tau_{others}$ がその他の要因の総和による緩和時間である。移動度と緩和時間の関係は、キャリアの質量を $m^*$ 、電荷素量をqとして

$$\mu = \frac{q\tau}{m^*} \tag{4.2}$$

と表される。式(4.2)を用いて式(4.1)をキャリア移動度に関して整理する。

$$\frac{1}{\mu_{\text{tot}}} = \frac{1}{\mu_{\text{phonon}}} + \frac{1}{\mu_{\text{imp}}} + \frac{1}{\mu_{\text{others}}}$$

(4.3)

式(4.3)に対して、正孔移動度 450 cm $^2$  V $^{-1}$  s $^{-1}$  を示した固相成長 Ge 薄膜に、各散乱要因  $^3$  を代入し、方程式的に $\mu_{\rm others}$ を得る。

$$\frac{1}{(\mu_{\text{tot}} =) 450} = \frac{1}{(\mu_{\text{phonon}} =) 1900} + \frac{1}{(\mu_{\text{imp}} =) 880} + \frac{1}{(\mu_{\text{others}} =) 1800}$$

(4.4)

ここで $\mu_{\text{others}}$ の起源としては粒界散乱や、界面散乱が候補となる。(4.4)により、粒界散乱 ( $\mu_{\text{others}}$ ) が支配的な従来の多結晶 Ge 薄膜  $^{4-6}$ とは異なり、イオン化不純物 ( $\mu_{\text{phonon}}$ ) が最もキャリア輸送を散乱していると推察される。これは、Ge 薄膜中の多数キャリア (正孔) を意味する。前章では、固相成長 Ge 薄膜には、結晶粒界・粒内双方に起因したアクセプタ欠陥が存在するとの知見を得た。すなわち、結晶性の向上や粒界密度の低減 (大粒径化) が正孔低減に繋がり、キャリア移動度の向上が期待できる。固相成長では、下部層界面に発生した初期核から結晶成長が開始することが知られている  $^{7-9}$ 。また、Ge/SiO2 ガラス界面にはダングリングボンド発端するとされる欠陥が問題となっている  $^{10-14}$ 。以上より、従来の Ge/SiO2 ガラス界面を再検討することで、界面欠陥の抑制と初期結晶核の改善に伴う固相成長 Ge 薄膜の高品質化が期待できる。

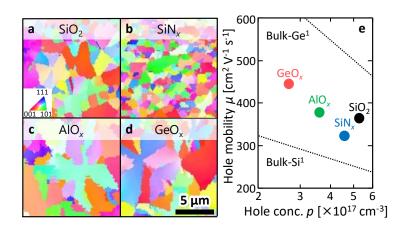

本章では、固相成長 Ge 薄膜の更なるキャリア移動度向上の施策として、Ge と反応性の乏しい下部層挿入を検討する。4.2 節では、実験手法を説明する。4.3 節では、下部界面層に適した絶縁層を電気的特性と結晶粒径の観点から探索する。4.4 節では、4.3 節の結果を元に、GeOx下部層が固相成長 Ge 薄膜に与える影響を論じる。4.5 節では、本章の結果をまとめる。

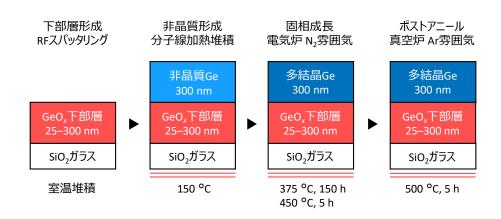

## 4.2 実験手法

## 4.3 下部絶縁層の選定

本節では、固相成長 Ge 薄膜に適した下部絶縁層の選定について記す。試料作製手順を図 4.1 に示す。前章と同様の洗浄を行った  $SiO_2$  ガラス基板上に、RF マグネトロンスパッタにより  $AlO_x$ 、 $SiN_x$ 、および  $GeO_x$ を各 50 nm ずつ室温堆積した。このとき、ベース真空度は  $3.0\times10^{-4}$  Pa とし、RF 電力は全て 50 W とした。製膜後、MBE チャンバーにおいて固相成長の前駆体となる非晶質 Ge を加熱堆積  $(150\,^{\circ}C)$  した。堆積レートは 1 nm  $min^{-1}$  とし、300 nm 製膜した。その後、石英管アニール炉を用い、 $N_2$  雰囲気中で  $450\,^{\circ}C$ 、5 h の熱処理を行うことで固相成長を誘起した。

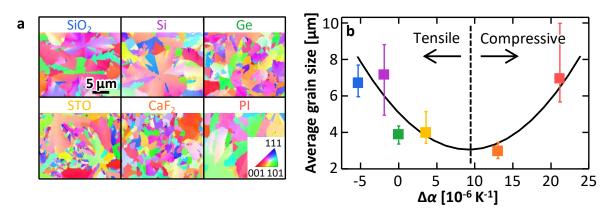

図 4.2(a)-(d)に示す逆極点方位(IPF)像より、固相成長 Ge 層の結晶粒径が下部絶縁層種に強く影響されていることが判る。Ge/下部層間における界面エネルギーの変質に伴う核発生頻度

の変化が示唆される  $^{12}$ 。IPF 像を解析することで、各下部層を挿入した成長層の結晶粒径は、下部層挿入無し(SiO<sub>2</sub>)で  $^{2.9}$  μm、SiN<sub>x</sub>が  $^{1.4}$  μm、AlO<sub>x</sub>が  $^{5.3}$  μm、そして  $^{60}$  なが  $^{4.5}$  μm と判った。電気的特性評価を行った結果、全ての  $^{60}$  成長層が従来の  $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$   $^{60}$

図 4.1 試料作製手順.

図 4.2 固相成長 Ge(300 nm)の下部絶縁層依存性. (a)-(d) IPF 像および(e)電気的特性.

## 4.4 GeOx下部層挿入

4.3 節では、 $Ge/SiO_2$  ガラス界面への  $GeO_x$  下部層を挿入により電気的特性と結晶粒径の改善を同時に見込めることが判った。本節では Ge 膜厚  $t_{Ge}$  と  $GeO_x$  膜厚  $t_{ox}$  を独立に制御することで、 $GeO_x$  下部層が固相成長 Ge 薄膜に与える影響を体系化する。

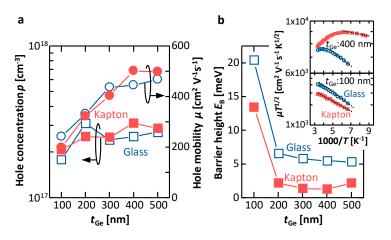

#### 4.4.1 Ge 膜厚変調効果

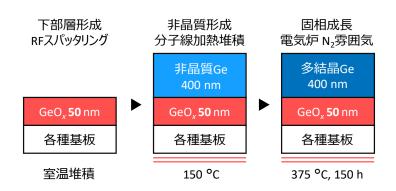

本節では、 $t_{ox}$ を 50 nm に固定し、 $t_{Ge}$ を変調した際の固相成長 Ge 薄膜の振る舞いを記す。試料作製手順を図 4.3 に示す。RF マグネトロンスパッタにより GeO $_x$ (50 nm)を SiO $_2$ ガラス基板上に室温堆積した。このとき、ベース真空度は  $3.0\times10^{-4}$  Pa とし、RF 電力は全て 50 W とした。製膜後、MBE チャンバーにおいて固相成長の前駆体となる非晶質 Ge を加熱堆積(150 °C)した。堆積レートは 1 nm min<sup>-1</sup> とし、100-600 nm 製膜した。その後、石英管アニール炉を用い、 $N_2$  雰囲気中で熱処理 ( $T_g$ : 375-450 °C)を行うことで固相成長を誘起した。結晶化後、Ar 雰囲気中でポストアニール (PA: 500°C, 5 h)を行った。

図 4.3 試料作製手順.

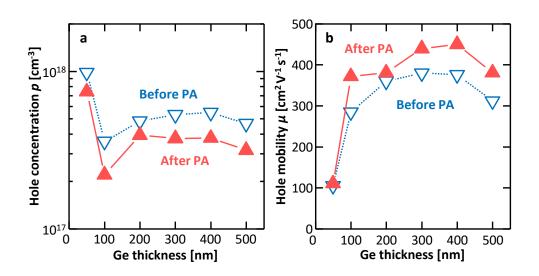

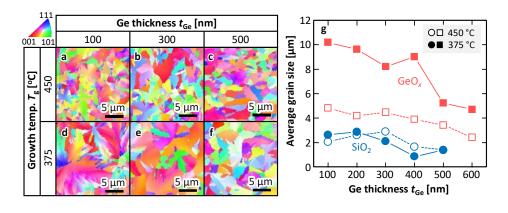

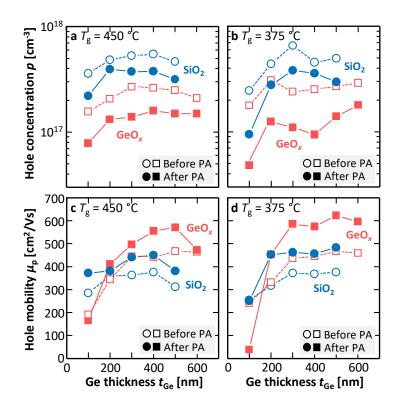

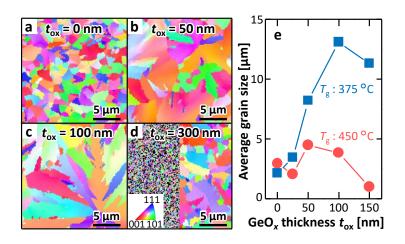

図 4.4(a)—(f)に GeO<sub>x</sub> 下部層層を挿入した固相成長 Ge 薄膜の IPF 像を示す。結晶はランダム配向しており、結晶粒径は  $t_{Ge}$  と  $T_g$  の両者に影響されていることが判る。 $t_{Ge}$  について図 4.4(g)に整理した。Ge 成長層の結晶粒径は、 $GeO_x$  下部層挿入により劇的に向上した。また、 $t_{Ge}$  の増加と共に結晶粒径は減少している。これは核生成サイトの増加に起因する  $^{2,9,11}$ 。 固相成長の先行研究  $^{4,11}$  と同様、成長温度の低減 ( $T_g$ =375 °C) により、更なる結晶粒径の拡大を達成した。この傾向は、 $GeO_x$  下部層挿入時に顕著であった。特に、 $GeO_x$  下部層を挿入し、 $t_{Ge}$  = 100 nm、 $T_g$  = 375 °C で得た Ge 成長層は、これまで得た固相成長  $Ge(Sn)^{1,2,11,19}$  の中で最大レベルの結晶粒径 10  $\mu$ mを達成した。

続いて電気的特性を示す。図 4.5(a),(b)より、全  $t_{\rm Ge}$ と  $T_{\rm g}$ に対し  ${\rm GeO}_{\rm x}$  下部層挿入によって p の 低減が為された。結晶性の向上と大粒径化を反映し、欠陥誘起アクセプタを低減したと考えられる。図 4.5(c),(d)より結晶粒径が減少した(図 4.4(g))一方、 $t_{\rm Ge}$ と共に  $\mu$  が増加傾向にあることが判る。これは界面散乱の低減に起因すると説明できる  $^{2,11}$ 。 ${\rm GeO}_{\rm x}$  下部層を挿入した場合、 $t_{\rm Ge} \leq 200$  nm では、 ${\rm SiO}_2$  ガラス上に直接形成した場合よりも結晶粒径は大きいが、 $\mu$  はより小さな値と成った。これは、現状の  ${\rm Ge}/{\rm GeO}_{\rm x}$  界面が従来の  ${\rm Ge}/{\rm SiO}_2$  ガラス界面よりも強い散乱源となっていることを示唆している。 $t_{\rm Ge} > 200$  nm では、 ${\rm GeO}_{\rm x}$  下部層を挿入した場合の方が高  $\mu$  と成った。4.1 節で述べた Matthiessen の規則と  ${\rm Irvin}$  カーブ  $^{20,21}$  より、 $t_{\rm Ge} > 200$  nm では、 $\mu$  が粒界散乱と不純物散乱のバランスで決定される  $^{1,2}$ 。従って、 ${\rm GeO}_{\rm x}$  下部層挿入による  $\mu$  の向上は、大粒径化に伴う粒界散乱の低減と p の低減に伴う不純物散乱の低減に由来すると考えられる。

PA の施行により、Ge 成長層中の欠陥誘起アクセプタを補償し不純物散乱の低減を検討した。これにより、全ての Ge 成長層でp が減少した(図 4.5(a)(b))。Ge 膜中の陥誘起アクセプタが、Ge 原子の熱拡散により補償されたことを示唆している。低温成長 ( $T_g$  = 375 °C)した際には大きく減少し、結晶粒径が最も大きかった 100 nm の成長層において、 $10^{16}$  cm<sup>-3</sup> 台前半という極めて低いp を実現した。図 4.5(c)(d)より、下部層の有無に関わらず、 $t_{Ge}$  > 200 nm において高い $\mu$  を有していることが判る。この傾向は、 $T_g$  = 375 °C の時に顕著である。これは、不純物散乱が支配的な領域で

あることに起因する。高密度前駆体を用いた固相成長に対して  $GeO_x$  下部層挿入、低温結晶化  $(T_g = 375 \, ^{\circ}\text{C})$ 、厚膜化 $(t_{Ge} = 500 \, \text{nm})$ 、そして PA を重畳することで  $SiO_2$  ガラス上に極めて高い  $\mu$   $(620 \, \text{cm}^2 \, \text{V}^{-1} \, \text{s}^{-1})$ を実証した。これは、酸化濃縮法で合成した単結晶 Ge 薄膜  $^{9,22}$  よりも優れており、低温プロセス  $(<800 \, ^{\circ}\text{C})$  で絶縁体基板上に直接合成した半導体薄膜中最高の値である。

図 4.4 EBSD 解析. (a)-(f) IPF 像ならびに(g) 結晶粒径.

図 4.5 Ge 成長層の PA 前後の電気的特性の Ge 膜厚  $t_{Ge}$  依存性. (a),(b)正孔密度 p, (c),(d)正孔移動度  $\mu$ . (a),(c)  $T_g$  = 450 °C および (b),(d)  $T_g$  = 375 °C.

#### 4.4.2 GeOx下部層膜厚変調効果

前節では、我々の Ge 固相成長プロセスに対して GeO<sub>x</sub> 下部層を採用した。これにより、低温プロセス( $<800\,^{\circ}$ C) で絶縁体基板上に直接合成した半導体薄膜中最高の $\mu(620\,\mathrm{cm^2\,V^{-1}\,s^{-1}})$ を SiO<sub>2</sub> ガラス上で実証した。しかし、GeO<sub>x</sub> 下部層が固相成長プロセスに作用する物理機構への理解は浅い。従って、本節では GeO<sub>x</sub> 膜厚  $t_{\mathrm{ox}}$  の制御によりメカニズム解明を試みた。

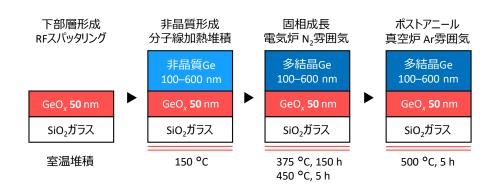

本節では、 $t_{Ge}$ を 300 nm に固定し、 $t_{ox}$ を変調した際の固相成長 Ge 薄膜の振る舞いを記す。試料作製手順を図 4.6 に示す。前章と同様の洗浄を行った SiO<sub>2</sub> ガラス基板上に、RF マグネトロンスパッタにより GeO<sub>x</sub>(25-300 nm)を室温堆積した。このとき、ベース真空度は  $3.0\times10^{-4}$  Pa とし、RF電力は全て 50 W とした。製膜後、MBE チャンバーにおいて固相成長の前駆体となる非晶質 Geを加熱堆積(150 °C)した。堆積レートは 1 nm min<sup>-1</sup>とし、300 nm 製膜した。その後、石英管アニール炉を用い、N<sub>2</sub>雰囲気中で熱処理( $T_g$ : 375-450 °C)を行うことで固相成長を誘起した。結晶化後、Ar 雰囲気中でポストアニール (PA: 500 °C, 5 h)を行った。

図 4.6 試料作製手順.

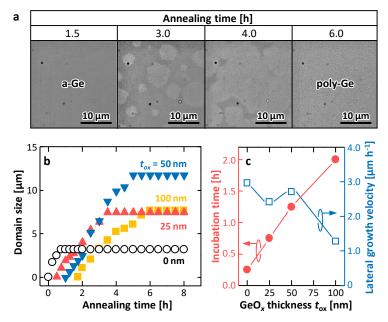

*in-situ* 光学顕微鏡 (Linkam 10042 D with a Keyence VH-5500)を用いて Ge 固相成長におけるドメイン生成過程を評価した。ここで、 $t_{ox}$  を変調した際のドメイン径と測定時間の兼ね合いにより、 $T_g = 400$  °C を採用した。図 4.7(a)は固相成長の典型的な成長様態を示している。すなわち、熱処理時間の増加とともに①初期結晶核が生成、②ドメインが横方向に成長し、③飽和して膜全面が最終的に多結晶 Ge に覆われる。GeO<sub>x</sub> 下部層を挿入しない場合の固相成長 Ge に対し、飽和ドメイン径は数倍となった <sup>1,2</sup>。また、ドメイン径が全  $t_{ox}$  (0-100 nm) に対し、時間とともに発展していく様が判る(図 4.7(b))。 $t_{ox}$  と共に飽和ドメイン径も増加し、 $t_{ox} = 50$  nm で極大となった後、減少に転じた。固相成長では、核発生と横方向成長のバランスが飽和ドメイン径を決定する。すなわち、低い核発生頻度と高い横方向成長速度の重畳により大粒径化が見込める <sup>24</sup>。図 4.7(c)より核発生頻度と横方向成長速度が  $t_{ox}$  によって変化している。また、初期核が生成するまでの時間(潜伏時間)は  $t_{ox}$  と共に線形増加した。その一方で、横方向成長速度は  $t_{ox}$  > 50 nm で減少した。非晶質薄膜においては異種界面が核生成サイトとなる <sup>25</sup>。非晶質半導体への酸素取り込みが結晶化を遅延させること <sup>23</sup>を考慮すれば、 $GeO_x$ 層に起因した Ge 膜中の微量酸素  $(t_{ox} \le 50$  nm) が界面核発生を抑制し、多量の場合  $(t_{ox} > 50$  nm) にはさらに横方向成長を遅延させたと推察される。

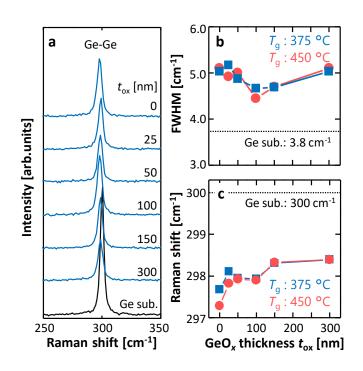

Raman 分光法により、 $t_{ox}$  が Ge 成長層の結晶性に与える影響を調査した。図 4.8(a)は Ge-Ge 振動モードを示すピークが約 300 cm<sup>-1</sup> に位置しており、熱処理後に全試料が結晶化していることを示唆している。Raman スペクトルより、 $T_g$  = 375, 450 °C に対する当該ピークの半値全幅と Raman シフトを導出した。図 4.8(b)は Ge ピークの FWHM が  $t_{ox}$  に依存していることを示している。この振舞いは、適切な  $t_{ox}$  において酸素原子が GeO $_x$  層から Ge 層に程よく拡散することにより、結晶性を向上させることを示唆している。図 4.8(c)は単結晶 Ge 基板から低波数側にピークシフトしているため Ge と SiO $_2$  ガラス基板の熱膨張係数差によって引張ひずみが導入されることを示す  $^{24}$ 。また、Ge-Ge ピークのシフトは  $t_{ox}$  の増加によって単結晶 Ge の値に漸近した。これは GeO $_x$ (7.6×10<sup>-6</sup> K<sup>-1</sup>) で Ge(5.8×10<sup>-6</sup> K<sup>-1</sup>) や SiO $_2$  ガラス (0.5×10<sup>-6</sup> K<sup>-1</sup>) よりも大きな熱膨張係数を有する為、SiO $_2$  ガラス基板からの応力を緩和したためだと考えられる。

図 4.7 固相成長 Ge のドメイン観察. (a) in-situ 光学顕微鏡像. (b)ドメイン径の熱処理時間依存性および(c) 潜伏時間と横方向成長速度の GeOx 膜厚 tox 依存性

図 4.8 Raman 分光法. (a) Raman スペクトル. (b) FWHM および(c) Raman shift.

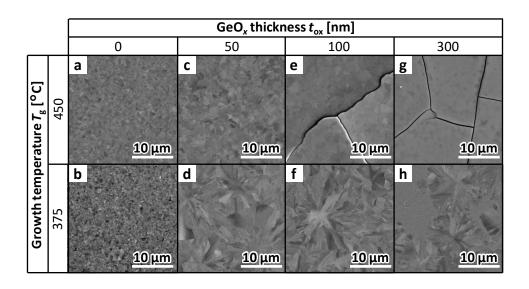

Ge 成長層の二次電子 (SE) 像を SEM によって取得した (図 4.9)。一部、高品質結晶に由来した結晶方位が可視化されている (チャネリングコントラスト)  $^{26}$ 。コントラストを確認すると、 $GeO_x$  下部層挿入によって Ge の結晶粒が拡大していることが判る。 $t_{ox} \geq 100$  nm では、低温熱処理 ( $T_g = 375$  °C) では認められない Ge 成長層でのクラックが、 $T_g = 450$  において発生した。400 °C 以上の場合、 $Ge/GeO_x$  界面反応により GeO が脱離する  $^{27,28}$ 。これを鑑みると、Ge 成長層を GeO ガスが掘進したことにより導入されたと考えられる。 $t_{ox} = 300$  nm の場合、結晶コントラストの存在しない非晶質状の領域が結晶化温度に関わらず観察された。これは図 4.7 の結果と一貫しており、 $GeO_x$  層からの過度の酸素供給が Ge 層へ為され、Ge の結晶化を著しく遅延させたと推察される。

図 4.9 Ge 成長層の SE-SEM 像.

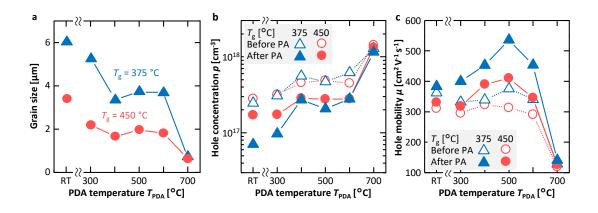

図 4.10(a)—(d)に  $T_g$  = 375 °C で結晶化した異なる  $t_{ox}$ に対する Ge 成長層の IPF 像を示す。Ge 結晶粒はランダム配向しており、 $t_{ox}$  に対して粒径は大きく変化した。特に、 $t_{ox}$  = 300 nm において非晶質領域が確認できた。SEM 観察の結果(図 4.9(g)(h))と符合しており、熱処理時間が Ge 成長層の全面結晶化を完了させるに不充分だったと考えられる。これらの結晶粒径を  $t_{ox}$  の関数として整理した(図 4.10(e))。前節と同様、低温 ( $T_g$  = 375 °C)で結晶化を促すことにより、全ての Ge 成長層に対して大粒径化した。固相成長において核発生頻度が低温で抑制される典型的な現象である  $^{1.4,11}$ 。 $T_g$  = 450 °C では、結晶粒径が  $t_{ox}$  と共に増加して  $t_{ox}$  = 50 nm でピークをとり、減少に転じる。図 4.7 で論じた  $T_g$  = 400 °Cの場合に一致する。一方、 $T_g$  = 375 °C では  $t_{ox}$  = 100 nm で最大粒径となった。これらは、 $GeO_x$  層からの酸素導入、ならびに Ge 結晶化の活性化エネルギーには差異があり、二者のバランス(温度で変化)が結晶粒径を決定することを示唆している。

図 4.10 Ge 成長層の EBSD 解析. (a)-(d) IPF 像および(e)結晶粒径の  $GeO_x$  膜厚  $t_{ox}$  依存性.

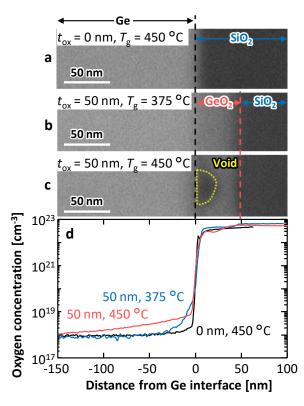

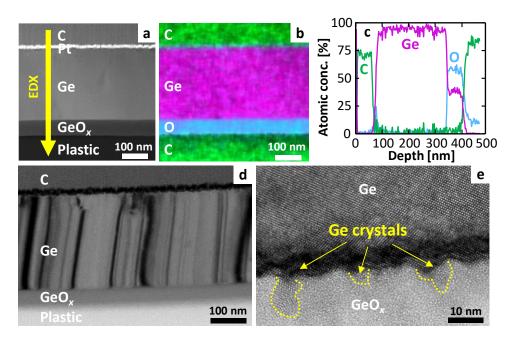

FIB-SEM (Helios Nanolab 600i) により、Ge 成長層 ( $t_{ox}$ = 0,50 nm) の断面構造を反射電子 (BSE) 像で観察した (図 4.11)。Ge, GeO<sub>x</sub>, SiO<sub>2</sub> ガラス各層に対応する領域が観察できる。GeO<sub>x</sub>層は  $T_g$ = 375 °C において均質である一方、 $T_g$ = 450 °C では暗領域が確認される。BSE 像では原子番号に応じたコントラストが生じる。従って、暗領域は Ge が欠損した体積欠陥:ボイドであると推察される。これは、高温熱処理に伴う GeO 脱離に起因する  $^{27}$  と考えられ、図 4.9 の結果と符合する。二次イオン質量分析法 (SIMS、PHIADEPT1010) によって Ge/GeO<sub>x</sub> 界面近傍の酸素濃度を見積もった。GeO<sub>x</sub>下部層が無く ( $t_{ox}$ = 0 nm) とも酸素が  $1\times10^{18}$  cm<sup>-3</sup> 程度存在することが判った。これは、非晶質堆積中に混入するものと考えられる。一方、Ge/GeO<sub>x</sub> 界面近傍において、酸素濃度は  $1\times10^{18}$  cm<sup>-3</sup> よりも高くなり、結晶化温度が高温であるほど顕著であった。これにより、GeO<sub>x</sub>層から Ge への酸素導入が裏付けられる。また、高温熱処理において GeO<sub>x</sub>層にボイドが形成される証拠ともなる。以上により、酸素の拡散が Ge/GeO<sub>x</sub> 界面での不均一核生成を抑制したため、核生成頻度が低減し(図 4.7)、大粒径化した (図 4.10)と考えられる。

図 4.11 Ge 成長層の断面評価. (a)-(c)断面 BSE-SEM 像ならびに(d) SIMS による酸素濃度プロファイル.

Ge 成長層の電気的特性を評価した。ここで、クラックが発生した  $t_{\rm ox} \geq 100$  nm、 $T_{\rm g} = 450$  °C は除外した(図 4.9(e)(g))。測定可能な試料は欠陥誘起アクセプタに起因した p 型伝導を示した  $^{29,30}$ 。 先ずPA前の場合について論じる。 $t_{\rm ox}$ と共にpが減少し、そして増加に転じる(図 4.12(a))。FWHM と結晶粒径の  $t_{\rm ox}$  に対する振る舞いと同様であるため、結晶性を反映していると考えられる。また、 $t_{\rm ox}$  の増加と共に $\mu$  は増加し、減少に転じる(4.12(b))。p と粒径の振る舞いに一致しており、 $\mu$  が不純物散乱と粒界散乱に影響されていることが示唆される。

更なる特性向上のため、PA を行った。PA によって欠陥誘起アクセプタが補償され、全ての Ge 成長層のp が減少した。 $\mu$  はp の減少に伴い増加した。すなわち不純物散乱の緩和である。低温熱処理( $T_g = 375$  °C) することによる大粒径化を反映し、低いp と高い $\mu$  を達成できる。以上より  $t_{ox}$  や  $T_g$  を制御することで、Ge 層への微量酸素を導入でき、固相成長 Ge 薄膜の結晶性(結晶粒径、品質)と電気的特性の向上が期待できることが判明した。

図 4.12 Ge 成長層の電気的特性. (a)正孔密度 p ならびに(b)正孔移動度 μ.

### 4.5 結言

我々は固相成長法の高度化により、Ge 薄膜のキャリア移動度を刷新してきた。しかし、単結晶 Si 基板の値(正孔:  $450 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ )を大きく超えない現状では、Ge 薄膜は民生応用に堪えるとは言えない。本章では、下部界面層挿入による  $Ge/SiO_2$  ガラス界面の改質を通じ、固相成長 Ge 薄膜の高度化を試みた。

まず、Ge に対して化学反応性の乏しい絶縁材料を候補に下部層材料を検討した。その結果、下部層挿入により固相成長 Ge 薄膜の特性が変化した。特に結晶粒径と電気的特性の観点から AlOxと GeOx が下部層材料に好適であった。

最後に、 $GeO_x$ 下部層が Geの固相成長プロセスに作用する機構を探索した。 $Ge/GeO_x$  膜厚比と結晶化温度を制御することにより、 $GeO_x$  から Ge 層への酸素拡散が結晶成長速度と不純物補償に影響することを見出した。両者のバランスを最適化することで、これまでよりも優れた結晶粒径  $(10 \ \mu m)$  と電気的特性を有する固相成長 Ge 薄膜が実現できるとの知見を得た。

本章では、Ge の固相成長プロセスを変化させる物理要因(界面改善、酸素拡散)の一端に触れた。特に GeOx 下部層挿入により、固相成長 Ge 薄膜を従来よりも高度化した。

## 4.6 参考文献

- <sup>1</sup> K. Toko, R. Yoshimine, K. Moto, and T. Suemasu, Sci. Rep. 7, 16981 (2017).

- <sup>2</sup> R. Yoshimine, K. Moto, T. Suemasu, and K. Toko, Appl. Phys. Express 11, 031302 (2018).

- <sup>3</sup> S.M. Sze and J.C. Irvin, Solid State Electron. 11, 599 (1968).

- <sup>4</sup> K. Toko, I. Nakao, T. Sadoh, T. Noguchi, and M. Miyao, Solid State Electron. **53**, 1159 (2009).

- <sup>5</sup> H. Watakabe, T. Sameshima, H. Kanno, and M. Miyao, Thin Solid Films **508**, 315 (2006).

- <sup>6</sup> N. Uchida, T. Maeda, R.R. Lieten, S. Okajima, Y. Ohishi, R. Takase, M. Ishimaru, and J.-P. Locquet, Appl. Phys. Lett. **107**, 232105 (2015).

- <sup>7</sup> K. Toko, K. Nakazawa, N. Saitoh, N. Yoshizawa, N. Usami, and T. Suemasu, CrystEngComm **16**, 2578 (2014).

- <sup>8</sup> I. Yoshikawa, M. Kurosawa, W. Takeuchi, M. Sakashita, O. Nakatsuka, and S. Zaima, Mater. Sci. Semicond. Process. **70**, 151 (2017).

- <sup>9</sup> P. Germain, K. Zellama, S. Squelard, J.C. Bourgoin, and A. Gheorghiu, J. Appl. Phys. **50**, 6986 (1979).

- <sup>10</sup> K. Moto, K. Yamamoto, T. Imajo, T. Suemasu, H. Nakashima, and K. Toko, Appl. Phys. Lett. **114**, 212107 (2019).

- <sup>11</sup> T. Sadoh, Y. Kai, R. Matsumura, K. Moto, and M. Miyao, Appl. Phys. Lett. **109**, 232106 (2016).

- <sup>12</sup> K. Kasahara, Y. Nagatomi, K. Yamamoto, H. Higashi, M. Nakano, S. Yamada, D. Wang, H. Nakashima, and K. Hamaya, Appl. Phys. Lett. 107, 142102 (2015).

- <sup>13</sup> D. Wang and H. Nakashima, Solid State Electron. **53**, 841 (2009).

- <sup>14</sup> C.G. Ahn, H.S. Kang, Y.K. Kwon, S.M. Lee, B.R. Ryum, and B.K. Kang, J. Appl. Phys. **86**, 1542 (1999).

- <sup>15</sup> E. Billig and M.S. Ridout, Nature **173**, 496 (1954).

- <sup>16</sup> J. Chen, D. Yang, Z. Xi, and T. Sekiguchi, J. Appl. Phys. **97**, 033701 (2005).

- <sup>17</sup> C.-Y. Tsao, J. Huang, X. Hao, P. Campbell, and M.A. Green, Sol. Energy Mater. Sol. Cells **95**, 981 (2011).

- <sup>18</sup> O. Madelung, Semiconductors: Data Handbook (Springer, Berlin, Heidelberg, 2004).

- <sup>19</sup> K. Moto, R. Yoshimine, T. Suemasu, and K. Toko, Sci. Rep. **8**, 14832 (2018).

- <sup>20</sup> T. Maeda, K. Ikeda, S. Nakaharai, T. Tezuka, N. Sugiyama, Y. Moriyama, and S. Takagi, Thin Solid Films **508**, 346 (2006).

- <sup>21</sup> N. Hirashita, Y. Moriyama, S. Nakaharai, T. Irisawa, N. Sugiyama, and S.I. Takagi, Appl. Phys. Express **1**, 1014011 (2008).

- <sup>22</sup> Z. Wang, L.P.H. Jeurgens, W. Sigle, and E.J. Mittemeijer, Phys. Rev. Lett. **115**, 016102 (2015).

- <sup>23</sup> Y.-M. Ha, S.-H. Lee, C.-H. Han, and C.-K. Kim, Journal of Electronic Materials **23**, 39 (1994).

- <sup>24</sup> T. Imajo, T. Suemasu, and K. Toko, Sci. Rep. **11**, 8333 (2021).

- <sup>25</sup> M. Cavillon, P.D. Dragic, and J. Ballato, Opt. Lett. **42**, 3650 (2017).

- <sup>26</sup> D.C. Joy, D.E. Newbury, and D.L. Davidson, J. Appl. Phys. **53**, R81 (1982).

- <sup>27</sup> A. Toriumi and T. Nishimura, Japanese Journal of Applied Physics **57**, 010101 (2017).

- <sup>28</sup> T. Nishimura, X. Tang, C. Lu, T. Yajima, and A. Toriumi, IEEE Journal of the Electron Devices Society **6**, 1212 (2018).

- <sup>29</sup> H. Haesslein, R. Sielemann, and C. Zistl, Phys. Rev. Lett. **80**, 2626 (1998).

- <sup>30</sup> H. Yang, D. Wang, and H. Nakashima, Appl. Phys. Lett. **95**, 122103 (2009).

## 第5章

# 多結晶 Ge 薄膜における歪印加の要因と影響

#### 5.1 緒言

Si は物性限界(キャリア移動度)が懸念されたが、歪エンジニアリング <sup>1-3</sup> を契機にポスト Moore 時代でも活躍している。これは、応力印加によりバンド構造が変化する物理を利用したものである。 同様にポスト Si 材料となる Ge においても、歪印加によりキャリア移動度の向上や直接遷移化に寄与する現象が見られる <sup>4-6</sup>。その秀抜な物性を駆使したデバイス開発も活発に検討されている <sup>7,8</sup>。

多結晶 Ge 薄膜では、合成後に圧縮方向の残留歪が生じる傾向にあることが知られてきた<sup>9</sup>。しかし、その詳細な機構は解明されていない。また、この成長時導入応力による歪はキャリア輸送特性に影響するほど大きな値ではないが<sup>5</sup>、結晶成長や粒界特性には影響を与える可能性がある。 残留応力は熱応力と真性応力に大別できるが、前者に関しては Ge と基板の熱膨張係数差に着目すれば変調が可能である<sup>10</sup>。すなわち、応力が与える影響を探索できると期待できる。

本章では、基板変調を通じて固相成長 Ge 薄膜における歪印加の要因と影響を調査する。5.2 節では実験手法を説明する。5.3 節では、固相成長における歪印加プロセスを体系化する。5.4 節では、成長時導入歪が固相成長 Ge 薄膜の諸特性に与える影響を包括的に考察する。5.5 節では、本章で得られた結果を総括する。

#### 5.2 実験手法

試料作製手順を図 5.1 に示す。多結晶 Ge 薄膜に加わる歪を変調するため、熱膨張係数  $\alpha$  の 異なる基板を採用した。それらは、 $SiO_2$  ガラス,Polyimide (PI),n 型 Fz-Si (001),n 型高抵抗 Ge (110), $SrTiO_3$  (STO) (001), $CaF_2$  (001) であり、Ge と基板の熱膨張係数差を  $\Delta\alpha$  として表 5.1 に整理した。基板を有機洗浄後、Ge 成長層と基板界面の差異を除くため、RF マグネトロンスパッタにより  $GeO_x$  層 50 nm を室温堆積した。下部層形成後、前節と同様に MBE チャンバーにおいて非晶質 Ge を加熱堆積 (150 °C) した。堆積レートは 1 nm  $min^{-1}$  とし、Ge 膜厚は 400 nm で固定した。その後、石英管アニール炉を用い、 $N_2$  雰囲気中で 375 °C、150 nm の熱処理を行うことで固相成長を誘起した。

試料の結晶性は Raman 分光法 (JASCO NRS-5100、波長 532 nm、出力 0.5 mW、露光 60 sec  $\times$ 2、スポットサイズ: 5  $\mu$ m)、X-Ray Diffraction (XRD)法 (Rigaku SmartLab、Cu Ka 放射線源、電圧 40 kV、電流 30 mA)、走査型電子顕微鏡 (JEOL JSM-7001F、電圧 25 kV、電流 15 mA)へア タッチメントされた電子後方散乱回折 (EBSD) 法 (TSL) を用いて評価した。面直 ( $\theta$ -2 $\theta$ ) および面内 ( $\varphi$ -2 $\theta_\chi$ ) XRD パターンはスキャン範囲を 20°から 60°の範囲を 0.01°ステップで行った。解析において、Raman スペクトル及び XRD パターンのフィッティングには Origin6.0 における Pseudo Voight 関数を用いた。電気的特性は Bio-Rad HL5500PC system を用いて van der Pauw 法により評価した。

図 5.1 試料作製手順.

表 5.1 熱膨脹係数  $\alpha$  と Ge-基板間の  $\alpha$  の差  $\Delta\alpha$ .

| 基板               | 熱膨張係数 α [10 <sup>-6</sup> K <sup>-1</sup> ] | Δα [10 <sup>-6</sup> K <sup>-1</sup> ] |

|------------------|---------------------------------------------|----------------------------------------|

| SiO <sub>2</sub> | 0.5                                         | -5.3                                   |

| Si               | 3.9                                         | -1.9                                   |

| Ge               | 5.8                                         | 0                                      |

| STO              | 9.4                                         | 3.6                                    |

| CaF <sub>2</sub> | 18.9                                        | 13.1                                   |

| PI               | 27.0                                        | 21.2                                   |

### 5.3 歪導入機構の検討

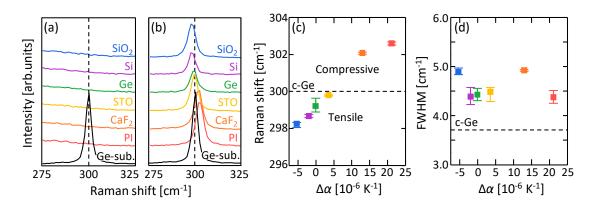

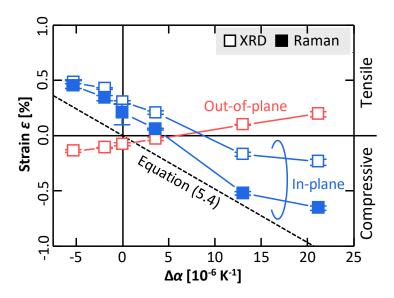

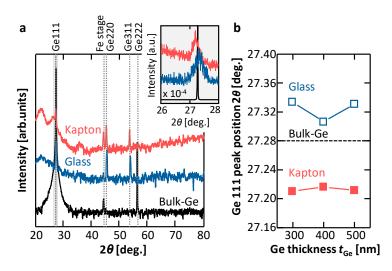

固相成長後の多結晶 Ge 薄膜の歪と結晶性の調査のため、Raman 分光法と XRD 法を用いた。図 5.2(a)は、熱処理前の Ge 薄膜の Raman スペクトルにはピークが生じず、非晶質状態であることを示している。一方、熱処理後には結晶 Ge の振動モードに相当するピークが 300 cm<sup>-1</sup> 付近に生じており、全 Ge 成長層が結晶化していることが判る(図 5.2(b))。図 5.2(c)より、Raman シフト位置は  $\Delta \alpha$  とともに高波数側に移動した。また、 $\Delta \alpha < 5 \times 10^{-6}~\mathrm{K}^{-1}$  では引張歪、 $\Delta \alpha > 5 \times 10^{-6}~\mathrm{K}^{-1}$  では圧縮 歪となる  $^{11}$ 。図 5.2(d)は、半値全幅 (FWHM) が  $\Delta \alpha$  と明確な相関を持たないことを示している。すなわち、固相成長 Ge 薄膜における Ge-Ge 結合の質が  $\Delta \alpha$  に依存しないことを示唆する。

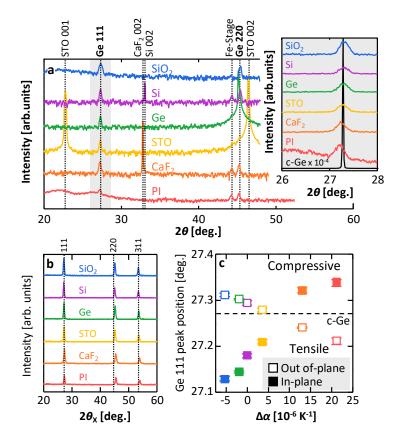

図 5.3(a)の面直  $\theta$ -2 $\theta$  XRD パターンより、すべての試料で Ge111 面と 220 面に対応する回折ピークが生じた。挿入図によると、試料の Ge 111 面のピーク位置は単結晶 Ge(111)基板のピーク位置から僅かにずれており、更に基板毎に異なっている。図 5.3(b)の面内  $\varphi$ -2 $\theta_\chi$  XRD パターンでは、全ての Ge 成長層で Ge111, 220, 311 のピークが見られた。以上の XRD パターンと Ge の粉末回折パターン (JCPDS 04-0545) 12 と照らし合わせると、固相成長 Ge 薄膜は多結晶であることが判る。これは、界面に挿入した GeO $_\chi$  が非晶質であり、単結晶基板とのエピタキシャル関係が断たれた為である。図 5.3(a),(b)で得られた Ge111 ピークの回折角(面直:2 $\theta$ , 面内:2 $\theta_\chi$ )を導出し、 $\Delta \alpha$  の関数として図 5.3(c)に整理した。多結晶 Ge 薄膜の Ge111 のピーク位置が  $\Delta \alpha$  に強く依存していることを示している。面内測定においてピーク位置  $2\theta_\chi$ は  $\Delta \alpha$  とともに増加するが、面直測定 (2 $\theta$ ) では逆の振る舞いが見られる。この挙動は、面直/面内に対する Ge 薄膜の歪の方向が逆であることを示しており、これは一般的な等方弾性体の特性と一致している。以上より、 $\Delta \alpha$  は Ge 成長層の歪に影響を与えることが判る。

図 5.2 Raman 分光法解析. (a) 熱処理前ならびに(b) 熱処理後の Raman スペクトル. (c) Raman shift ならびに(d) FWHM の Δα 依存性.

図 5.3 XRD 解析. (a)  $\theta$ -2 $\theta$  ならびに(b)  $\varphi$ -2 $\theta_\chi$ XRD パターン. (c) Ge111 ピーク回折位置(2 $\theta$ ,2 $\theta_\chi$ )の  $\Delta \alpha$  依存性.

Raman 分光法と XRD 法の結果を基に Ge 成長層に導入される歪 $\epsilon$ を解析した。一般的に、Raman シフト $\Delta\omega$ と歪 $\epsilon$ は以下の関係式で表される。

$$\varepsilon = \frac{\Delta\omega}{b} \tag{5.1}$$

Manganelli<sup>11</sup> らによって提案された歪フォノン係数b (= -395 cm<sup>-1</sup>)を用いて、膜に印加される歪を結晶 Ge ピークの Raman シフトから見積もった。また、固相成長後の冷却過程において、Ge 成長層には  $\Delta \alpha$  に対応する歪が印加される。薄膜に発生する熱応力 $\sigma_{th}$ は次の式で表される <sup>10</sup>。

$$\sigma_{th} = \left(\alpha_f - \alpha_s\right) \frac{\Delta T}{1 - \nu} E_f \tag{5.2}$$

ここで、 $\alpha_f$ と $\alpha_s$ はそれぞれ薄膜と基板の熱膨張係数、 $\Delta T$  は温度差、 $\nu$  は薄膜のポアソン比、 $E_f$  は薄膜材料の Young 率である。更に、Hook の法則より応力 $\sigma$ と歪 $\epsilon$ の関係は次の式で表される。

$$\varepsilon = E\sigma \tag{5.3}$$

式(5.2)と式(5.3)より、熱歪 $\varepsilon_{th}$ を得る。

$$\varepsilon_{\rm th} = \left(\alpha_f - \alpha_s\right) \frac{\Delta T}{1 - \nu} \tag{5.4}$$

非晶質 Ge が基板に拘束されつつ収縮するためと考えられる。 すなわち、Ge 成長層の歪の総量 は Δα 起因の熱歪のみならず、非晶質から結晶への相転移の際に導入される歪も要因になっていることを示唆している。

図 5.4 固相成長 Ge 薄膜の歪解析.

### 5.4 各種物性に与える影響

まず、Ge 成長層の結晶粒径を EBSD 法で評価した。図 5.5(a)の IPF 像より、すべての成長層がランダムに配向した結晶で構成されており、非晶質  $GeO_x$  下部界面層のために単結晶基板とのエピタキシャル関係がないことが判る。これは XRD の結果に一致する(図 5.3)。粒径は基板種に依らず  $\mu m$  オーダーと従来法よりも 1 桁以上大きい  $^{15}$ 。これは非晶質前駆体の高密度化と  $GeO_x$  下部層の効果による  $^{16}$ 。Ge の粒径は基板の種類に依存し、 $\Delta\alpha$  に対して放物線状の傾向を示した(図 5.5(b))。図 5.4 の結果を踏まえると、図 5.5(b)は $|\varepsilon|$ が大きいほど結晶粒径も拡大する。固相成長を導入する熱処理時には、基板との熱膨張係数差により非晶質 Ge 層にも応力印加がなされる。これらの結果は、 $\varepsilon$ の二乗に比例する内部弾性ポテンシャルが Ge の横方向成長を促進することを示唆している。この挙動は、歪を利用して非晶質 Ge 層の成長促進を行った既報と一致する 17-19。

図 5.5 EBSD 解析. (a) IPF 像. (b) 結晶粒径の  $\Delta \alpha$  依存性.

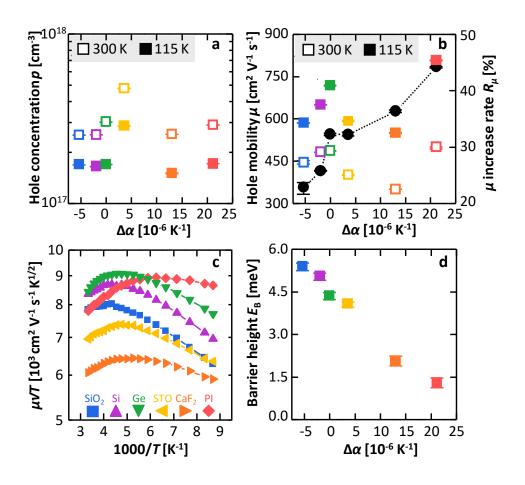

続いて図 5.6 に電気的特性の温度依存性を示す。全ての Ge 成長層で、欠陥誘起アクセプタに起因する  $10^{17}$  cm<sup>-3</sup> オーダーの正孔密度 p が見られた  $^{20,21}$ 。STO 上の合成膜は比較的高い p を示している。原因は明らかになっていないが、STO 基板からの過剰な酸素脱離により Ge 成長層の結晶性を損なったと考察している  $^{22}$ 。室温  $(300~{\rm K})$  から  $115~{\rm K}$  に下げることで、全 Ge 成長層のp が減少した。これは、アクセプタの不活性化に伴う一般的な半導体の挙動である  $^{21}$ 。図 5.6(b) は、 $\mu$  が  $\Delta \alpha$  に対して明確な傾向を持たないことを示している。単結晶 Ge の  $\mu$  と p の関係  $^{23}$  によると、本研究における Ge 成長層の  $\mu$  は、不純物・粒界の両方の散乱によって制限される  $^{24}$ 。この挙動は、 $\mu$  が GB 散乱によってのみ制限される一般的な多結晶半導体とは異なる  $^{24}$ 。我々は、 $\mu$  の増加率 $R_{\mu}$ を以下のように定義した。

$$R_{\mu} = \frac{\mu_{115} - \mu_{300}}{\mu_{300}} \tag{5.5}$$

ここで、添え字は測定温度(300 K, 115 K)を示す。図 5.6(b)は、 $R_{\mu}$ が  $\Delta\alpha$  とともに増加することを表す。Seto による多結晶半導体のキャリア輸送モデルを用いて、粒界障壁  $E_{\rm B}$ を推定した。

$$\mu = \frac{Lq}{\sqrt{2\pi m^* k_B T}} \exp\left(-\frac{E_B}{k_B T}\right) \tag{5.6}$$

ここで、T は絶対温度、L は結晶粒径、 $m^*$ は有効質量、 $k_B$ はボルツマン定数である。図 5.6(c)は、 $\mu T^{1/2}$ の Arrhenius plots を示す。 $\mu T^{1/2}$ は増加し、その後減少することが判る。この挙動は、 $\mu$  が室温付近では不純物散乱の影響を受け、低温では粒界散乱によって制限されることを示している。また、Arrhenius plots の形状が基板の違いによって大きく異なっていることから、 $E_B$  の違いが大きいことがわかる。これらの  $E_B$ を  $\Delta \alpha$  で整理した(図 5.6(d))。 $\Delta \alpha$  の増加に伴い  $E_B$  が減少することを示している。この  $E_B$  の挙動は図 5.6(b)の  $R_\mu$  の挙動の原因となっている。すなわち、 $\Delta \alpha$  の大きい(すなわち圧縮歪の)  $G_B$  層は  $G_B$  が小さいため、不純物散乱が $G_B$  に与える影響が強くなる。ここで注意したいのは、 $G_B$  下部界面層を挿入した一方で、異なる材料の基板を用いている以上、単純に歪の影響だけを抽出することはできないことである。しかし、多結晶  $G_B$  の  $G_B$  を下げるには、圧縮歪が導入される基板種が好適であると強く示唆された。応力に対する  $G_B$  変調のメカニズムはまだ明らかになっていないが、一般的な多結晶材料で発生する圧電効果に起因すると考えている  $G_B$  25。

以上、固相成長 Ge 薄膜において引張歪 $(L_B)$  を上昇させ、圧縮歪 $(L_B)$  を低減させることが判明した。

図 5.6 電気的特性の  $\Delta \alpha$  依存性. (a)  $t_{Ge} = 500$  nm における  $\theta$ -2 $\theta$  XRD パターン. (b) Ge111ピーク回折位置 (2 $\theta$ )の  $t_{Ge}$  依存性.

#### 5.5 結言

本章では、固相成長における基板種により熱応力を変調できることに着目し、多結晶 Ge 薄膜における歪印加の要因とその影響を探索した。

まず、Raman 分光法と XRD 法を用いて Ge 成長層に導入される歪を熱膨張係数差  $\Delta \alpha$  に対し整理した。その結果、固相成長 Ge 薄膜においては熱応力に起因する歪と、相遷移(非晶質→結晶) 時の引張歪の両者が支配的であることが判明した。

続いて、歪と物性の関連性を調査した。Ge 成長層内部における歪量に対し結晶粒径は 2 次関数的な挙動となった。これは弾性ポテンシャルによると考えられる。また、Seto モデルにより導出した粒界障壁  $E_B$  は  $\Delta \alpha$  に対し線形に減少した。すなわち、多結晶 Ge 薄膜における面内圧縮歪がキャリア輸送に好適であることが強く示唆される。

以上、歪導入機構を体系化するとともに、固相成長 Ge 薄膜における諸特性への影響を包括的に纏めた。本知見は多結晶材料のエンジニアリングに有用である。

## 5.6 参考文献

- <sup>1</sup> T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr, in *IEEE International Electron Devices Meeting* 2003 (2003), pp. 11.6.1-11.6.3.

- <sup>2</sup> S. Takagi, T. Mizuno, T. Tezuka, N. Sugiyama, T. Numata, K. Usuda, Y. Moriyama, S. Nakaharai, J. Koga, A. Tanabe, N. Hirashita, and T. Maeda, in *IEEE International Electron Devices Meeting* 2003 (2003), pp. 3.3.1-3.3.4.

- <sup>3</sup> J.L. Hoyt, H.M. Nayfeh, S. Eguchi, I. Aberg, G. Xia, T. Drake, E.A. Fitzgerald, and D.A. Antoniadis, in *Digest. International Electron Devices Meeting*, (2002), pp. 23–26.

- <sup>4</sup> G. Taraschi, A.J. Pitera, and E.A. Fitzgerald, Solid State Electron. **48**, 1297 (2004).

- <sup>5</sup> M.V. Fischetti and S.E. Laux, J. Appl. Phys. **80**, 2234 (1996).

- <sup>6</sup> J. Greil, A. Lugstein, C. Zeiner, G. Strasser, and E. Bertagnolli, Nano Lett. **12**, 6230 (2012).

- <sup>7</sup> K. Ikeda, Y. Kamimuta, Y. Moriyama, M. Ono, M. Oda, T. Irisawa, and T. Tezuka, in *2014 7th International Silicon-Germanium Technology and Device Meeting (ISTDM)* (2014), pp. 3–4.

- <sup>8</sup> Y. Hoshina, M. Shimizu, K. Tadokoro, and A. Yamada, in *2011 37th IEEE Photovoltaic Specialists Conference* (2011), pp. 000242–000245.

- <sup>9</sup> K. Toko, I. Nakao, T. Sadoh, T. Noguchi, and M. Miyao, Solid State Electron. **53**, 1159 (2009).

- <sup>10</sup> Wolf, Stanley., Tauber, and R. N., *Silicon Processing for the VLSI Era. Vol. 1, Vol. 1,* (Lattice Press, Sunset Beach, California, 2000).

- <sup>11</sup> C.L. Manganelli, M. Virgilio, O. Skibitzki, M. Salvalaglio, D. Spirito, P. Zaumseil, Y. Yamamoto, M. Montanari, W.M. Klesse, and G. Capellini, J. Raman Spectrosc. 51, 989 (2020).

- <sup>12</sup>JCPDS File No. 04-0545 (Cubic Ge).

- <sup>13</sup> W.H. Bragg and W.L. Bragg, Proceedings of the Royal Society of London. Series A, Containing Papers of a Mathematical and Physical Character **88**, 428 (1913).

- <sup>14</sup> H. Miura, H. Ohta, N. Okamoto, and T. Kaga, Appl. Phys. Lett. **60**, 2746 (1992).

- <sup>15</sup> K. Toko, R. Yoshimine, K. Moto, and T. Suemasu, Sci. Rep. 7, 16981 (2017).

- <sup>16</sup> T. Imajo, K. Moto, R. Yoshimine, T. Suemasu, and K. Toko, Appl. Phys. Express 12, 015508 (2018).

- <sup>17</sup> B. Hekmatshoar, S. Mohajerzadeh, D. Shahrjerdi, and M.D. Robertson, Appl. Phys. Lett. **85**, 1054 (2004).

- <sup>18</sup> M. Moniwa, M. Miyao, R. Tsuchiyama, A. Ishizaka, M. Ichikawa, H. Sunami, and T. Tokuyama, Appl. Phys. Lett. **47**, 113 (1985).

- <sup>19</sup> K. Toko, T. Sadoh, and M. Miyao, Appl. Phys. Lett. **94**, 192106 (2009).

- <sup>20</sup> H. Haesslein, R. Sielemann, and C. Zistl, Phys. Rev. Lett. **80**, 2626 (1998).

- <sup>21</sup> H. Yang, D. Wang, and H. Nakashima, Appl. Phys. Lett. **95**, 122103 (2009).

- <sup>22</sup> Y.J. Chang and S.H. Phark, Current Applied Physics 17, 640 (2017).

- <sup>23</sup> S.M. Sze and J.C. Irvin, Solid State Electron. 11, 599 (1968).

- <sup>24</sup> J.Y.W. Seto, J. Appl. Phys. **46**, 5247 (1975).

- <sup>25</sup> R. Baraki, N. Novak, M. Hofstätter, P. Supancic, J. Rödel, and T. Frömling, J. Appl. Phys. **118**, 085703 (2015).

## 第6章

# 固相成長 Ge 薄膜のフレキシブル基板への展開

#### 6.1 緒言

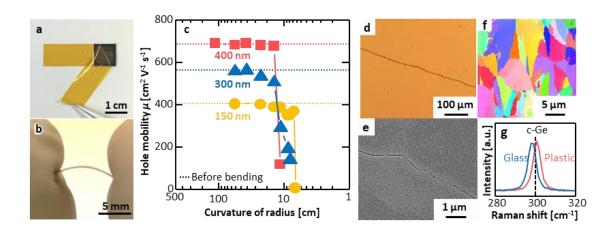

モノのインターネット(IoT) 化が進展した新しい社会「Sociery5.0」が取り沙汰されている「。従来「重く、高価で、固く、割れやすい」単結晶基板上に形成されてきたトランジスタは IoT 化に荷が重い。「軽く、安価で、曲げ畳め、丈夫な」フレキシブル基板上へと代替できれば、常識が転換するデバイスも夢ではない。サイズや設置場所を問わず、無毒であればウェアラブルに、更には「電子皮膚」といった生体融合デバイスも叶えられる<sup>2</sup>。再び文明開化の音が鳴るだろう。フレキシブルTFTの創出のため、水素化アモルファス Si<sup>3-6</sup>や酸化物半導体<sup>7</sup>、有機半導体薄膜 <sup>8,9</sup>の研究が国内外で盛んである。既にディスプレイ画素用として実用化されているものもある一方、材料物性の観点から電界効果移動度は低く<sup>10</sup>、ディスプレイ信号駆動ドライバや CMOS 論理回路には不向きである。CPU や駆動素子を全て集積した次世代デバイス「システム・オン・ディスプレイ」を目指し、高いキャリア移動度を有する無機半導体への注目が集まっている。Ge のフレキシブル TFT 応用も検討されている <sup>11-15</sup>が、未だ単結晶 Si-MOSFET を超える電界効果移動度は得られていない。 隘路となっているのがフレキシブル基板上への高キャリア移動度薄膜の合成である。

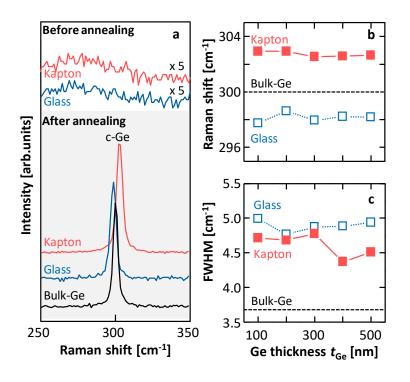

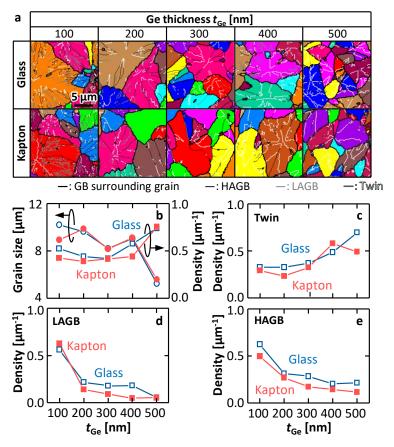

4 章では下部界面層の挿入が固相成長 Ge 薄膜の成長機構に与える影響を探索した。これにより、 $GeO_x$  層からの微量の酸素拡散が Ge の固相成長プロセスに好適であることを見出した。さらに、低温プロセス( $\leq 500$  °C)によって、大粒径( $10~\mu m$ )かつ優れたキャリア輸送特性( $620~cm^2~V^{-1}$   $s^{-1}$ )を有する多結晶 Ge 薄膜を  $SiO_2$  ガラス上に実証した。また 5 章では多結晶 Ge 薄膜に対する 歪導入と物性への影響を包括的に議論した。その結果、Ge より大きな熱膨張係数を持つ基板利

用により導入される圧縮歪が、粒界障壁を緩和することを発見した。

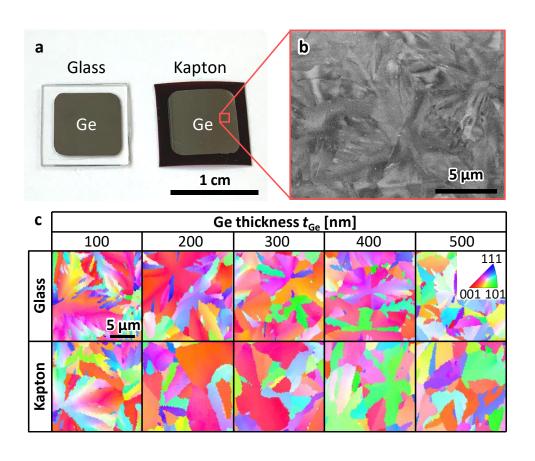

本章では、前章まで築いてきた知見を基に、高耐熱プラスチック基板上 (Polyimide、耐熱温度: Kapton  $\leq$  400 °C, XENOMAX  $\leq$  500 °C) への高移動度な多結晶 Ge 薄膜の展開を検討する。 6.2 節では実験手法を説明する。 6.3 節では、前章まで得た知見を活かし、プラスチック基板上へ高キャリア移動度を有する多結晶 Ge 薄膜を合成する。 6.4 節では、本章で得られた結果を総括する。

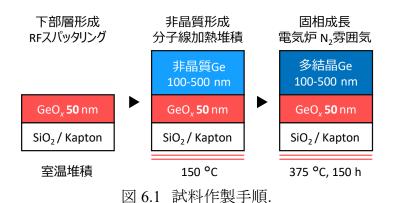

#### 6.2 実験手法

試料作製手順を図 6.1 に示す。RF マグネトロンスパッタにより  $GeO_x$  層 50 nm を  $SiO_2$  ガラス基板上とプラスチック基板上に室温堆積した。下部層形成後、前節と同様に MBE チャンバーにおいて非晶質 Ge を加熱堆積  $(150\ ^\circ C)$  した。堆積レートは  $1\ nm\ min^{-1}$  とし、Ge 膜厚  $\underline{t}_{Ge}$  は 100-500 nm で変調した。その後、石英管アニール炉を用い、 $N_2$  雰囲気中で  $375\ ^\circ C$ 、 $150\ h$  の熱処理を行うことで固相成長を誘起した。

試料の結晶性は Raman 分光法 (JASCO NRS-5100、波長 532 nm、出力 0.5 mW、露光 60 sec ×2、スポットサイズ 5 μm)、X-Ray Diffraction (XRD) 法 (Rigaku SmartLab、Cu Kα 放射線源、電圧 40 kV、電流 30 mA)、走査型電子顕微鏡 (SEM: JEOL JSM-7001F、電圧 25 kV、電流 15 mA)へ装着された電子後方散乱回折 (EBSD) 法 (TSL)、透過型電子顕微鏡 (TEM: FEI、Tecnai Osiris、電圧 200 kV)を用いて評価した。面直 (θ-2θ) XRD パターンはスキャン範囲を 20°から 60°の範囲を 0.01°ステップで行った。解析において、Raman スペクトル及び XRD パターンのフィッティングには Origin6.0 における Pseudo Voight 関数を用いた。電気的特性は Bio-Rad HL5500PC systemを用いて van der Pauw 法により評価した。

### 6.3 フレキシブル基板上への固相成長 Ge 薄膜の合成